嘉峪检测网 2024-11-01 08:35

导读:某芯片IO口开路失效,难道又是一个封装级故障。

某芯片IO口开路失效,难道又是一个封装级故障。

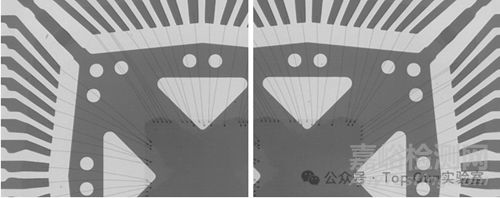

X射线检查没有发现故障Pin键合丝EOS烧毁断线形貌,也未见键合点明显异常。

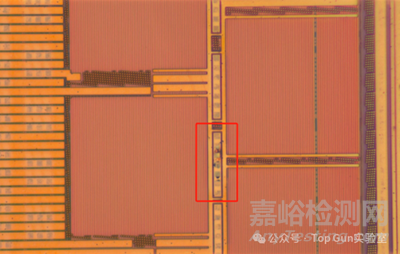

开盖后芯片正面未见明显异常,故障Pin位置也未见明显的烧毁或键合脱落形貌。

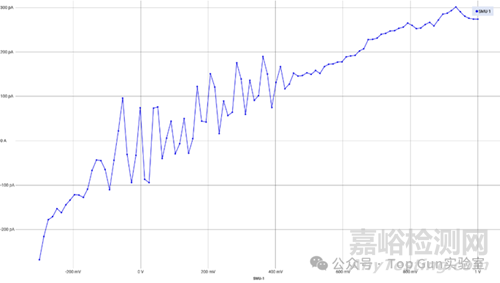

探针分别点在一焊点pad和外部引脚,进行IV测试,pad对地开路、外部引脚对地开路、pad对外部引脚短路,从该测试结果可知,二焊点接触良好,是芯片内部发生了开路问题。开路的IV曲线如下图所示。

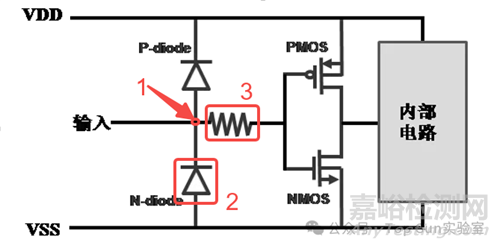

首先,进行理论分析,以制定下一步分析策略:典型的IO端口电路原理图示意如下图所示。

1)如果位置1开路,符合目前的IV测试结果,故障点应该在Pad往里走的via孔位置,该位置还没有到一级ESD保护电路;

2)如果位置2烧开路,正常芯片表面会有烧毁形貌,甚至会把键合丝烧毁,且IV测试会走poly电阻过二级ESD保护电路,会有IV曲线,与目前的开盖镜检和IV测试结果不符;

3)如果位置3烧开路,芯片顶层可能不会有明显的烧毁形貌,但是IV测试会走一级ESD保护电路,与目前的IV测试结果不符。

小结:该芯片烧毁位置在Pad到一级保护电路之前的位置,大概率为过孔位置有问题,因此可以对芯片表面金属进行去除观察。

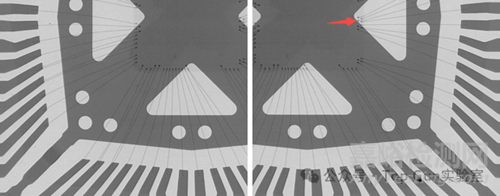

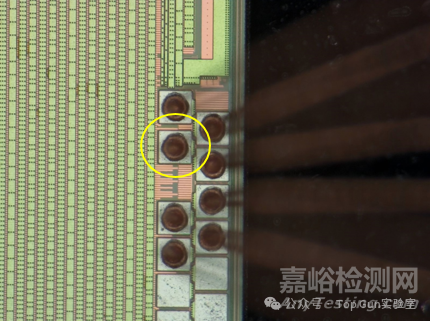

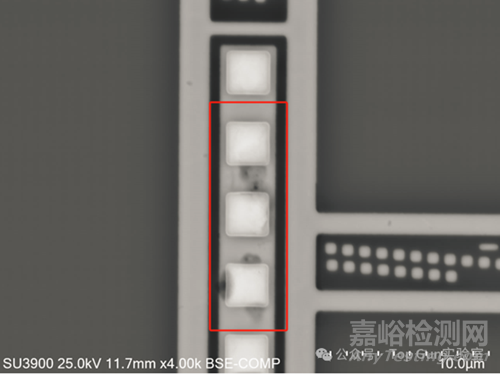

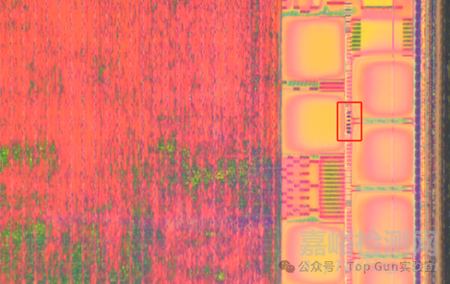

顶层金属去层观察:去除顶层后发现该Pad往内部电路走的过孔有疑似烧毁形貌。

继续向下去层:确认该过孔烧毁导致开路。

写在最后:本案只分析到故障现象,该案例主要介绍的是在缺少EFA故障点定位条件的时候,如何进行缺陷暴露的方案制定。此类问题的分析,需要结合电性测试结果以及芯片IO口典型设计大致推断故障点在哪个位置,然后针对性的制定缺陷暴露方法,最后实施精确的小范围有针对性的故障观察。

来源:Top Gun实验室

关键词: 芯片