嘉峪检测网 2024-11-03 11:43

导读:本文介绍了半导体失效之铜电迁移(Cu EM)模型研究。

《半导体器件的失效机理和模型》将针对硅基半导体器件常见的失效机理展开研究。这些失效机理大致按照从硅到封装器件的半导体生产工艺流程进行了分类:前段制程(FEoL)、后段制程(BEoL)和封装/界面失效机理。

注:失效机理研究只包括那些业界相对成熟,同时还包括这些失效机理的模型研究现状。内容主要来源为国内外文献的翻译整理,供大家学习参考。

各阶段常见的典型失效机理

前段制程(FEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 栅极氧化物

2)热载流子注入(HCI)

3)负偏压温度不稳定性(NBTI)

4)表面反转(移动离子)

5)浮栅非易失性存储器数据保持

6)局部电荷捕获非易失性存储器数据保持

7)相变(PCM)非易失性存储器数据保持

后段制程(BEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- low k材质电介质/移动铜离子

2)铝电迁移(Al EM)

3)铜电迁移(Cu EM)

4)铝和铜腐蚀

5)铝应力迁移(Al SM)

6)铜应力迁移(Cu SM)

封装/界面常见的失效机理

1)因温度循环和热冲击导致的疲劳失效

2)因温度循环和热冲击导致的界面失效

3)因高温导致的金属间化合物和氧化失效

4)锡须

5)离子迁移动力学(PCB)--组件清洁度

本文对铜电迁移(Cu EM)模型进行研究

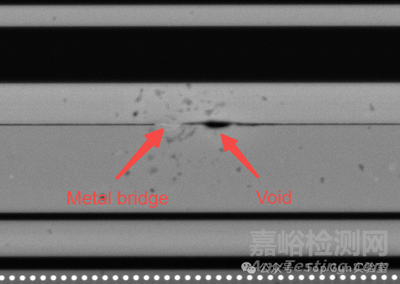

就像铝(Al)的情况一样,在铜(Cu)线中,载流电子与铜(Cu)离子之间的动量交换会导致铜离子沿电子电流的方向漂移这种漂移会产生与电流密度成正比的应力梯度,其可能是拉伸的也可能是压缩的。

在足够长的金属导体中和电流密度足够高的情况下,负发散位点的拉伸应力会导致其形成空洞,随着空洞的增长而导致故障;正发散位点的压缩应力会导致其形成挤出物或小丘,导致钝化层开裂或由于挤出的铜而使相邻导体短路。

对于铜制程,电流密度指数n约为1.1。目前尚不清楚该指数为何不完全等于1,可能是由于铜中存在非金属杂质。在某些结构中,n的值可能大于1.1但小于2。数值较高的原因也不明确,但不是因为焦耳热。

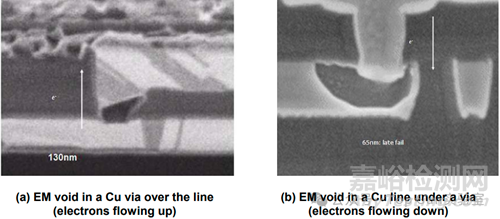

同铝线,铜线在高电流密度测试条件下,需要考虑发热(焦耳热)产生的温度梯度,未考虑到的自热可能会产生明显大于2的电流密度指数,从高电流密度到低电流密度的失效时间数据外推必须考虑到这一点。另外,由于金属走线和过孔中铜晶界的密度、位置和电流传输路径的差异,金属走线和过孔的电迁移动力学不同。

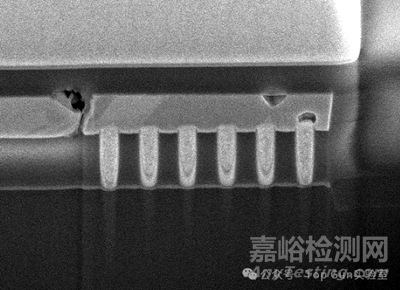

注:与铝一样,具有简单键合焊盘连接的单层金属走线电迁移测试结构比过孔供电测试结构的寿命长得多,因此简单键合焊盘连接的单层金属走线电迁移测试结构会产生过于乐观的寿命预测。此外,这种结构在实际中很少存在,过孔端接的测试结构更能代表产品设计。

过孔端接测试结构(Via-terminated test structures)寿命分布会受到电子流方向、过孔数量和布局的影响,设计师需要考虑电阻和饱和效应。过孔端接测试结构必须精心设计,以避免电阻饱和和水库效应,这会产生具有误导性的t50和σ值。

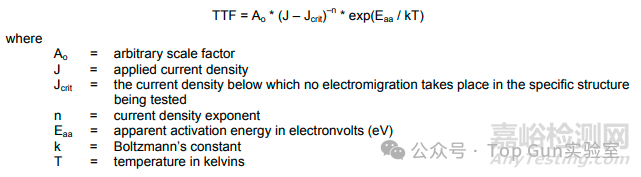

失效时间(TTF)的模型公式如下:

在这个模型中,J必须远大于Jcrit才能从测试条件外推到正常使用条件。J是平均电流密度。

根据布莱奇关系公式:Lb×Jcrit=常数,布莱奇长度和临界电流密度相关,铜金属导体的常数在3000A/cm左右。例:对于20mA/μm²量级的应力电流密度,测试结构的长度通常在200~400μm之间。

必须强调的是,足够长的金属导体定义必须是该线的长度大大超过所施加电流密度下的布莱奇长度。如果线的长度不超过布莱奇长度的数倍,那么从测试中可以得到较大的表观n值。

失效判据是电阻百分比增加(常用的是ΔR/R×100%=20%)。铜的电阻与时间R(t)曲线的表现与铝的不同。铝显示出一个较短的不活跃期(电阻无变化),主要是由于潜伏期,随后电阻随时间线性增加;而铜显示出一个较长的初始不活跃期,随后电阻迅速跃升,然后电阻随时间线性增加。

铜电迁移的过孔/线路测试结构1.1<n<2,激活能Eaa=0.85~0.95eV。

Cu EM寿命预估示例:

目标:

计算加速条件下和正常使用条件下的加速因子(AF)。

假设条件:

被测样品:具有大晶粒尺寸的长Cu金属导线

1)正常使用条件为:50°C芯片温度和2.0×105A/cm²的电流密度

2)加速条件为:80°C芯片温度和2.5×105A/cm²的电流密度

3)表观活化能Eaa:0.9eV

4)J>>Jcrit,n=1.1

AF计算公式:

AF=(Juse/Jaccel)–n*exp[(Eaa/k)(1/Tuse–1/Taccel)]

假设条件代入计算:

AF=(2.0/2.5)–1.1*exp[(0.9eV/8.62x10–5eV/K)(1/(273+50)K–1/(273+80)K)]=1.28*15.6=20

结论:从电流密度高、温度高的加速测试环境转移到电流密度低、温度低的正常使用环境,TTF(故障时间)值将增加约20倍。电流密度使故障加速约1.3倍,而温度使故障加速约16倍。

相关文献:

1)E.T. Ogawa, et al., “Electromigration Reliability Issues in Dual-Damascene Cu Interconnections,” IEEE Transactions on Reliability, Vol. 51, Issue 4, 2002, pp. 403-419.

2)K.N. Tu, “Recent advances on electromigration in very-large-scale-integration of interconnects,” Journal of Applied Physics, Vol. 94, Issue 9, 2003, pp. 5451-5473.

3)A.H. Fischer, O. Aubel, J.Gill, T.C.Lee, B.Li, C.Christiansen, F.Chen, M.Angyal, T.Bolom, E.Kaltalioglu "Reliability Challenges in Copper Metallizations arising with the PVD Resputter Liner Engineering for 65 nm and beyond," IEEE International Reliability Physics Symposium Proceeding,s 2007, pp. 511-515

4)B. Li, T.D. Sullivan, and T.C. Lee, “Line Depletion Electromigration Characterization of Cu Interconnects,” IEEE Transactions on Device and Materials Reliability, Vol. 4, Issue 1, 2004, pp. 80-85

5)B. Li, et al., “Impact of Via-line Contace on Cu Interconnect Electromigration Performance,” IEEE International Reliability Physics Symposium Proceedings, 2005, pp. 24-30.

6)J.R. Black, “Electromigration Failure Modes in Aluminum Metallization for Semiconductor Devices,” Proceedings of the IEEE, Vol. 57, Issue 9, 1969, pp. 1587-1594.

7)J.J. Clement, “Reliability analysis for encapsulated interconnect lines under dc and pulsed dc current using a continuum electromigration transport model,” Journal of Applied Physics, Vol. 82, Issue 12, 1997, pp. 5991-6000.

8)R.G. Filippi, et al., “Electromigration Results with Large Sample Size for Dual Damascene Structures in a Copper/CVD Low-k Dilelectric Technology,” IEEE International Interconnect Technology Conference Proceedings, 2006, pp. 98-100.

来源:Top Gun实验室

关键词: 半导体