嘉峪检测网 2024-11-04 08:39

导读:本文将为您解释系统级 ESD 现象和器件级 ESD 现象之间的差异,并向您介绍一些提供 ESD 事件保护的系统级设计方法。

1、引言

随着技术的发展,移动电子设备已成为我们生活和文化的重要组成部分。平板电脑和智能手机触摸技术的应用,让我们能够与这些设备进行更多的互动。它构成了一个完整的静电放电 (ESD) 危险环境,即人体皮肤对设备产生的静电放电。

例如,在使用消费类电子设备时,在用户手指和平板电脑 USB 或者 HDMI 接口之间会发生 ESD,从而对平板电脑产生不可逆的损坏,例如:峰值待机电流或者永久性系统失效。

本文将为您解释系统级 ESD 现象和器件级 ESD 现象之间的差异,并向您介绍一些提供 ESD 事件保护的系统级设计方法。

2、系统级ESD保护与器件级ESD保护的对比

IC 的 ESD 损坏可发生在任何时候,从装配到板级焊接,再到终端用户人机互动。ESD 相关损坏最早可追溯到半导体发展之初,但在 20 世纪 70 年代微芯片和薄栅氧化 FET 应用于高集成 IC 以后,它才成为一个普遍的问题。

所有 IC 都有一些嵌入式器件级 ESD 结构,用于在制造阶段保护 IC 免受 ESD 事件的损坏。

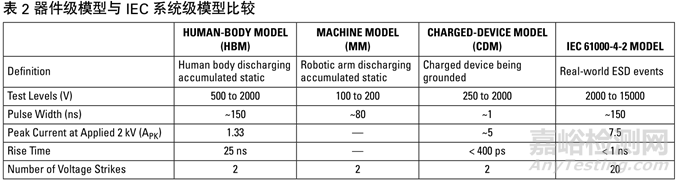

这些事件可由三个不同的器件级模型进行模拟:人体模型 (HBM)、机器模型 (MM) 和带电器件模型(CDM)。

HBM 用于模拟用户操作引起的 ESD 事件,MM 用于模拟自动操作引起的 ESD 事件,而 CDM则模拟产品充电/放电所引起的 ESD 事件。这些模型都用于制造环境下的测试。在这种环境下,装配、最终测试和板级焊接工作均在受控 ESD 环境下完成,从而减小暴露器件所承受的 ESD 应力。在制造环境下,IC 一般仅能承受 2-kV HBM 的 ESD 电击,而最近出台的小型器件静电规定更是低至 500V。

尽管在厂房受控 ESD 环境下器件级模型通常已足够,但在系统级测试中它们却差得很远。在终端用户环境下,电压和电流的ESD电击强度要高得多。

因此,工业环境使用另一种方法进行系统级 ESD 测试,其由IEC 61000-4-2 标准定义。器件级 HBM、MM和CDM 测试的目的都是保证 IC 在制造过程中不受损坏;IEC 61000-4-2规定的系统级测试用于模拟现实世界中的终端用户ESD事件。

IEC 规定了两种系统级测试:接触放电和非接触放电。使用接触放电方法时,测试模拟器电极与受测器件(DUT) 保持接触。非接触放电时,模拟器的带电电极靠近 DUT,同 DUT 之间产生的火花促使放电。

表 1 列出了 IEC 61000-4-2 标准规定的每种方法的测试级别范围。请注意,两种方法的每种测试级别的放电强度并不相同。我们通常在4级(每种方法的最高官方标称级别)以上对应力水平进行逐级测试,直到发生故障点为止。

器件级模型和系统级模型有一些明显的区别,表 2 列出了这些区别。

表 2 中最后三个参数(电流、上升时间和电击次数)需特别注意:

a、电流差对于 ESD 敏感型器件是否能够承受一次 ESD 事件至关重要。由于强电流可引起结点损坏和栅氧化损坏,8-kV HBM 保护芯片(峰值电流5.33A)可能会因 2-kV IEC 模型电击(峰值电流7.5A)而损坏。因此,系统设计人员不能把 HBM 额定值同 IEC 模型额定值混淆,这一点极为重要。

b、另一个差异存在于电压尖峰上升时间。HBM 的规定上升时间为 25ns。IEC 模型脉冲上升时间小于1ns,其在最初 3ns 消耗掉大部分能量。如果 HBM 额定的器件需 25ns 来做出响应,则在其保护电路激活以前器件就已被损坏。

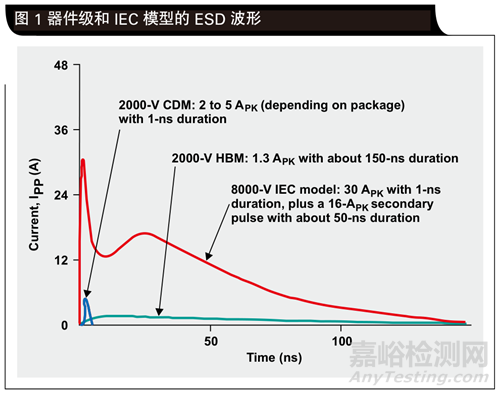

c、两种模型在测试期间所用的电击次数不同。HBM仅要求测试一次正电击和一次负电击,而 IEC 模型却要求 10 次正电击和 10 次负电击。可能出现的情况是,器件能够承受第一次电击,但由于初次电击带来的损坏仍然存在,其会在后续电击中失效。图 1 显示了 CDM、HBM 和 IEC 模型的 ESD 波形举例。很明显,相比所有器件级模型的脉冲,IEC 模型的脉冲携带了更多的能量。

3、TVS 如何保护系统免受 ESD 事件的损害

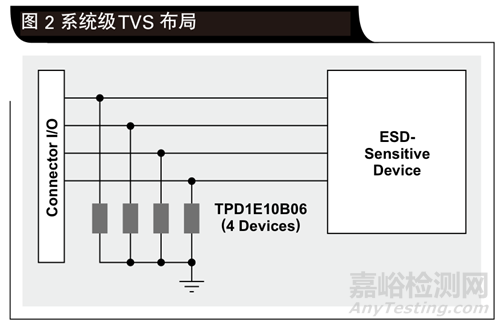

与 ESD 保护集成结构不同,IEC 61000-4-2 标准规定的模型通常会使用离散式独立瞬态电压抑制二极管,也即瞬态电压抑制器 (TVS)。相比电源管理或者微控制器单元中集成的 ESD 保护结构,独立 TVS 成本更低,并且可以靠近系统 I/O 连接器放置,如图 2 所示。

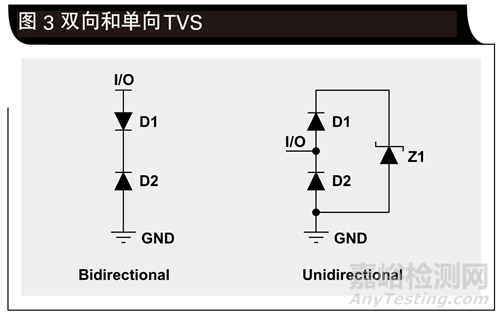

共有两种 TVS:双向和单向(参见图 3)。TI TPD1E10B06 便是一个双向 TVS例子,它可以放置在一条通用数据线路上,用于系统级 ESD 保护。

正常工作状态下,双向和单向 TVS 都为一个开路,并在 ESD 事件发生时接地。在双向 TVS 情况下,只要 D1 和 D2 都不进入其击穿区域,I/O 线路电压信号会在接地电压上下摆动。

当 ESD 电击(正或者负)击中 I/O 线路时,一个二极管变为正向偏置,而另一个击穿,从而形成一条通路,ESD 能量立即沿这条通路接地。在单向 TVS 情况下,只要 D2 和 Z1 都不进入其击穿区域,则电压信号会在接地电压以上摆动。

当正ESD电击击中I/O线路时,D1变为正向偏置,而Z1 先于 D2进入其击穿区域;通过 D1 和 Z1 形成一条接地通路,从而让 ESD 能量得到耗散。

当发生负 ESD 事件时,D2 变为正向偏置,ESD能量通过 D2接地通路得到耗散。由于 D1 和 D2 尺寸可以更小、寄生电容更少,单向二极管可用于许多高速应用;D1 和 D2 可以“隐藏”更大的齐纳二极管 Z1(大尺寸的原因是处理击穿区域更多的电流)。

4、系统级 ESD 保护的关键器件参数

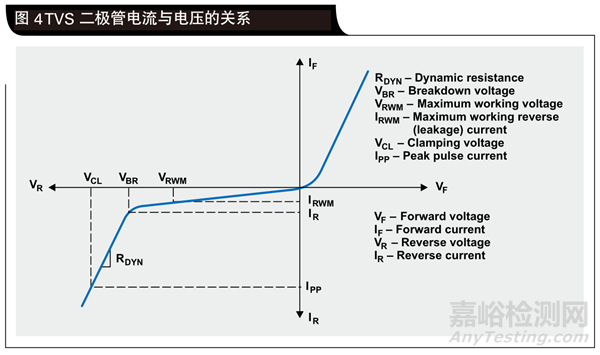

图 4 显示了 TVS 二极管电流与电压特性的对比情况。尽管 TVS 是一种简单的结构,但是在系统级 ESD 保护设计过程中仍然需要注意几个重要的参数。

这些参数包括击穿电压 VBR、动态电阻 RDYN、钳位电压VCL 和电容。

4.1、击穿电压VBR

正确选择 TVS 的第一步是研究击穿电压 (VBR)。

例如,如果受保护 I/O 线路的最大工作电压 VRWM 为5V,则在达到该最大电压以前 TVS 不应进入其击穿区域。通常,TVS 产品说明书会包括具体漏电流的VRWM,它让我们能够更加容易地选择正确的 TVS。否则,我们可以选择一个 VBR(min) 大于受保护I/O 线路 VRWM 几伏的 TVS。

4.2、动态电阻

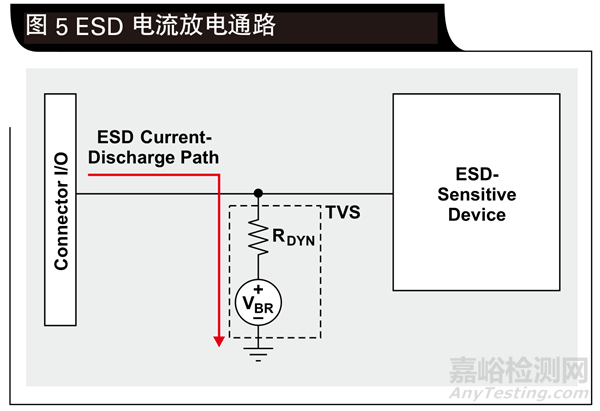

ESD 是一种极速事件,也就是几纳秒的事情。在如此短的时间内,TVS 传导接地通路不会立即建立起来,并且在通路中存在一定的电阻。这种电阻被称作动态电阻 (RDYN),如图 5 所示。

理想情况下,RDYN 应为零,这样 I/O 线路电压才能尽可能地接近 VBR;但是,这是不可能的事情。

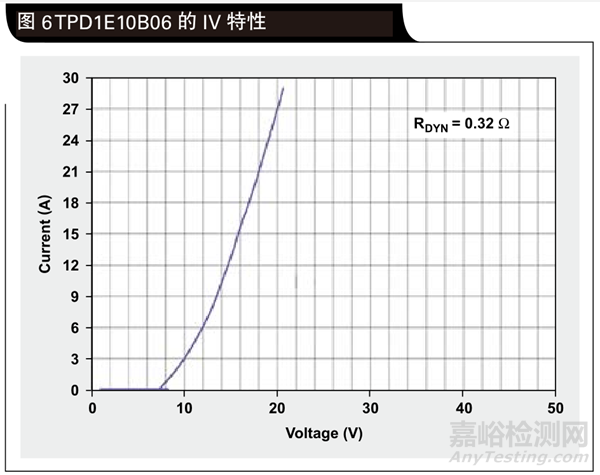

RDYN 的最新工业标准值为 1 Ω 或者 1 Ω 以下。利用传输线路脉冲测量技术可以得到 RDYN。使用这种技术时,通过 TVS 释放电压,然后测量相应的电流。在得到不同电压的许多数据点以后,便可以绘制出如图6一样的 IV 曲线,而斜线便为 RDYN。图 6 显示了 TPD1E10B06 的 RDYN,其典型值为 ~0.3 Ω。

4.3、钳位电压

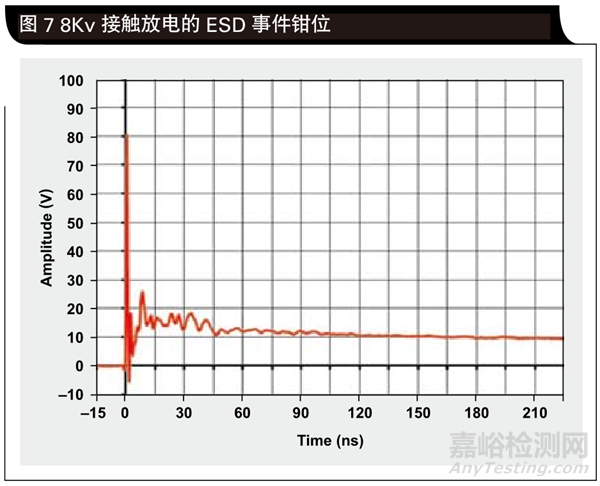

由于ESD是一种极速瞬态事件,I/O 线路的电压不能立即得到箝制。如图 7 所示,根据 IEC 61000-4-2 标准,数千伏电压被箝制为数十伏。

如方程式 1 所示,RDYN 越小,钳位性能也就越好:

其中,IPP 为 ESD 事件期间的峰值脉冲电流,而 Iparasitic 为通过 TVS 接地来自连接器的线路寄生电感。

把钳位电压波形下面的区域想像成能量。钳位性能越好,受保护ESD敏感型器件在ESD事件中受到损坏的机率也就越小。由于钳位电压很小,一些TVS可承受IEC模型的8kV接触式放电,但是“受保护”器件却被损坏了。

电容

在正常工作状态下,TVS为一个开路,并具有寄生电容分流接地。设计人员应在信号链带宽预算中考虑到这种电容。

结论

由于 IC 工艺技术节点变得越来越小,它也越来越容易受到 ESD 损坏的影响,不管是在制造过程还是在终端用户使用环境下。器件级 ESD 保护并不足以在系统层面为 IC 提供保护。我们应在系统级设计中使用独立 TVS。在选择某个 TVS 时,设计人员应注意一些重要参数,例如:VBR、RDYN、VCL 和电容等。

来源:电磁兼容之家

关键词: ESD