嘉峪检测网 2024-11-25 08:32

导读:本文对锡须生长模型进行研究

各阶段常见的典型失效机理

前段制程(FEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 栅极氧化物

2)热载流子注入(HCI)

3)负偏压温度不稳定性(NBTI)

4)表面反转(移动离子)

5)浮栅非易失性存储器数据保持

6)局部电荷捕获非易失性存储器数据保持

7)相变(PCM)非易失性存储器数据保持

后段制程(BEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- low k材质电介质/移动铜离子

2)铝电迁移(Al EM)

3)铜电迁移(Cu EM)

4)铝和铜腐蚀

5)铝应力迁移(Al SM)

6)铜应力迁移(Cu SM)

封装/界面常见的失效机理

1)因温度循环和热冲击导致的疲劳失效

2)因温度循环和热冲击导致的界面失效

3)因高温导致的金属间化合物和氧化失效

4)锡须

5)离子迁移动力学(PCB)--组件清洁度

本文对锡须生长模型进行研究

锡须可能导致灾难性的故障,尤其是在高精度的电子设备中,如航空航天设备、批量载人设备车辆、战斗机、导弹等。据报道,锡须在地球和太空产品的应用中都曾经导致了系统故障,迄今为止,有报道称至少有3次锡须诱导的短路导致在轨商业卫星完全失效。

2021年,因镀锡端子锡须可能会造成高压直流电正负极间短路,小鹏召回13399辆G3电动汽车。

在镀层和焊接表面上形成的锡须是一个巨大的可靠性风险,在几乎所有的操作环境中,从低湿度和低温(太空应用)到60°C/93%RH的条件,导电金属单晶都会随着时间从基底生长。导电晶体可以生长到足以接触相邻引脚的长度,或者断裂并转移到电路板和元件位置,导致现场设备故障。

关于当前锡须理论的全面讨论可以在JP-002中找到,多年来,锡须生长的机制一直在研究。但对于这些机制,尚未建立一个被普遍接受的解释。一些理论认为,锡须的生长是对镀锡层内应力释放机制(特别是“压缩”应力)的响应;其他理论则认为,锡须生长可能归因于锡晶粒结构的再结晶和异常晶粒生长过程。从冶金学的角度看,锡内应力是一个主要的因素。

在ULSI器件中,多种因素可导致镀锡层内产生残余应力从而引发锡须生长。这些因素包括:

1)电镀化学和工艺等因素,其中光亮镀锡工艺因其引入的残余应力较大,致使镀锡层更易形成锡须。

2)基底材料与镀锡层的相互扩散形成金属间化合物(如Cu6Sn5),改变晶格间距,进而产生应力,通过锡须形成来释放应力。

3)外部施加的压缩应力,如螺母或螺钉上的扭矩。

4)镀覆后的弯曲或拉伸操作,如电子元件引脚成型过程。

5)处理、探测等操作导致镀覆层和基底材料出现划痕或缺口。

6)镀覆材料与基底之间热膨胀系数不匹配。

7)腐蚀或氧化——目前在这一领域正在进行更多的研究工作。

由于所观察到的锡须生长极大程度地取决于诸如引线的几何形状、引线成分、温度、相对湿度、电镀添加剂、内应力、电流密度、电镀温度、镀后是否进行退火处理、是否存在镍底层等因素,能够预测锡须失效时间的通用模型迄今仍难以构建。

关于锡须形成的理论尚未达成普遍共识,仅知晓表面和次表面应力在这些单晶锡须结构的形成中发挥着重要作用,且铅的合金化具备将锡须形成最小化的能力。围绕该模型的争议依然存在。因此,强烈建议用户在针对其独特技术做出自身决策之前,查阅相关文献。

向锡中添加铅这一举措,已被证实能够降低锡须所带来的风险。其原因在于铅能够改变机械性能,具体表现为:铅能够提供更高的本征蠕变速率,降低屈服应力,同时减轻杂质对机械性能的影响。此外,铅在界面处发生偏析,这一现象不仅增加了晶界的迁移率,还提升了晶界和表面源在蠕变过程中对空位的吸收效率,改善了表面氧化物的连续性,并使金属间化合物的形态发生变化。但在RoHS(《关于限制在电子电气设备中使用某些有害成分的指令》)的要求中,明确新增了必须使用无铅焊料的严格要求。这一新增要求的提出,旨在进一步减少电子电气设备中含铅物质对环境和人体健康可能造成的潜在危害。

无铅焊料较有铅焊料更易生长锡须,其主要缘由包括:其一,无铅焊料的晶体结构及微观组织有别于有铅焊料,致使内部应力分布不均,进而增大锡须生长的概率;其二,无铅焊料的硬度普遍偏高,当遭遇外部应力时,难以通过塑性变形有效释放应力,由此促使锡须的形成;其三,无铅焊料的熔点相对更高,在制造及使用进程中所历经的热循环可能引发更大的热应力,从而对锡须的生长起到推动作用。

注:其他相关信息,可参考NASA关于锡须网站《http://nepp.nasa.gov/whisker/index.html》

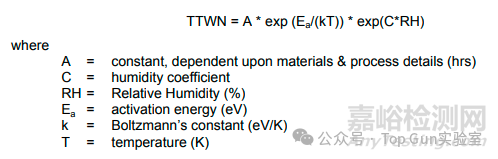

锡须成核时间模型(Time to Whisker Nucleation Model):

尽管锡须失效时间的模型尚未得以确立,但是一个前体模型,即锡须成核时间(TTWN),或者说锡须的孕育时间(以小时计),已经被提出。不过,在使用此模型时应当谨慎,以确保其适用性:

注:上述模型是从在铜合金(C194)引线框架顶部进行哑光镀锡,并在镀后24小时内进行150°C一小时镀后退火的样品上进行的各种实验中收集数据分析整理得出的。可能不适用于其他材料、工艺流程、镀液化学处理的样品。此外,此模型并未专门针对热循环导致的锡须生长机制进行研究。

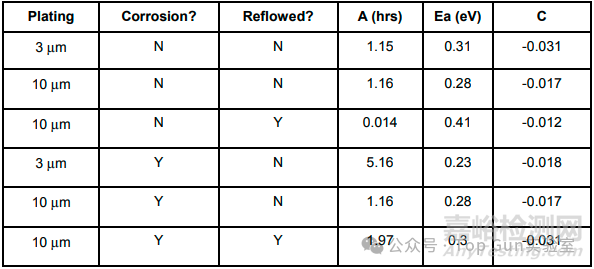

各种条件下锡须成核时间模型的值

因此,工业级芯片通常要求芯片封装后进行回流焊,回流焊的目的主要有如下两个:

1)通过回流焊释放应力,退火可以改变锡的晶体结构和内部应力分布,适当的退火处理可以减少锡层内部的应力,降低锡须生长的倾向;

2)回流焊可以激发有缺陷的样品,助于检测和排除早期不良品。

锡须成核时间预估示例:

目标:

计算加速条件下和正常使用条件下的加速因子(AF)。

假设条件:

1)正常使用条件为:30°C/40%RH

2)加速条件为:60°C/87%RH

3)表观活化能Eaa:0.41eV

4)A=0.014hrs

5)C=-0.012

AF计算公式:

TTWNaccel=A*exp(Eaa/(kTaccel))*exp(C*RHaccel)=0.014*exp(0.41/(8.62*10-5*333))*exp(-0.012*87)=7908.55hrs

TTWNuse=A*exp(Eaa/(kTuse))*exp(C*RHuse)=0.014*exp(0.41/(8.62*10-5*303))*exp(-0.012*40)=57204.77hrs

AF=TTWNuse/TTWNaccel=57204.77/7908.55=7.23

结论:由于温度和湿度的差异,从加速环境转移到正常使用环境,锡须成核时间(TTWN)值将增加到加速应力值的 7.23 倍。

来源:Top Gun实验室

关键词: 半导体器件