嘉峪检测网 2024-12-10 13:05

导读:本文对芯片封装测试流程进行详细介绍。

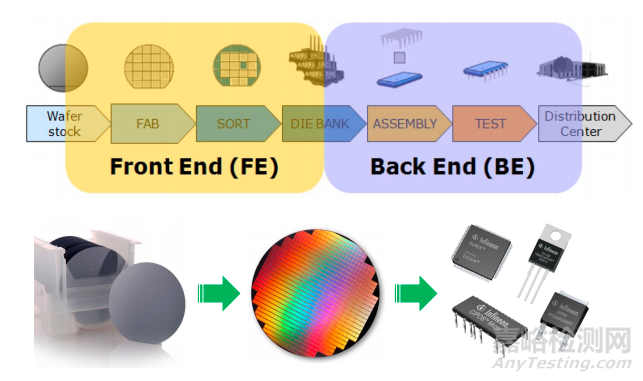

芯片封装测试环节,旨在将符合质量标准的晶圆,经过精密的切割、焊线及塑封工艺处理,确保芯片内部电路与外部器件间实现电气连接,为芯片提供必要的机械物理保护,并运用测试工具,对封装完成的芯片进行全面而严谨的功能与性能检测。获取IC芯片的过程涉及从设计到制造的复杂流程。鉴于其微小且薄的特点,若未施加适当保护,芯片极易遭受刮伤和损坏。

封测具有安放、固定、密封、保护芯片和增强电热性能的作用,也是沟通芯片内部世界与外部电路的桥梁——芯片上的接点用导线连接到封测外壳的引脚上,这些引脚又通过印制板上的导线与其他器件建立连接。因此,封测在集成电路领域中扮演着至关重要的角色。

从晶粒(Die)到成品芯片(Chip)

接下来,我们将对芯片封装测试流程进行详细介绍:

晶元测试

集成电路晶圆在进一步加工之前,必须经过严格的测试环节,以确保晶粒(Die)的功能完整性。测试将晶粒划分为三类:功能完好的Good Die、存在瑕疵缺陷的Defective Die以及功能完全失效的Fail Die。根据产品出货的分类要求,我们将选择符合要求的晶粒进行下一步的具体封装生产。这一过程被称为CP测试,全称为Chip Probing Test,即通过探针连接晶粒的Pad管脚进行测试,以确保其功能正常。这一步骤对于确保最终产品质量至关重要。

CP测试主要依赖于ATE测试机台(即Automatic Testing Equipment,简称ATE,自动化测试设备,用于为芯片测试提供所需的电源、信号和功能向量,并接收芯片的输出反馈信号以判断结果)、探针台(即Prober,它是一种高精度的机器平台,用于承载和移动晶圆,以便探针卡探针与晶粒Die的Pad管脚能够精确接触并导通)以及测试探针卡(即Probe Card,这是根据每颗芯片的电路和测试要求定制的测试板,用于实现ATE设备通道资源与芯片对应Pad的互通连接)等设备与测试组件。这些设备和组件协同工作,逐步完成晶圆上每颗晶粒Die的测试验证。对于存在问题的Die,通常会在其表面采用“打墨点(Ink)”等方式进行标记,以便于后续封装生产过程中的挑选和识别。

通过IC晶圆的CP测试,对功能正常的晶粒进行后续的封装生产,可以有效避免对缺陷芯片进行封装所带来的成本损失。尽管有时也采用“盲封”策略,即在不经过CP测试的情况下,对晶圆上的所有晶粒进行封装,并在后续阶段进行测试和筛选。然而,这种方法通常仅限于芯片流片后的初期工程批次晶圆,其目的在于尽快获得芯片工程样片,以验证流片芯片的成功与否,从而节省项目时间。在实际进入大规模量产阶段时,CP测试是不可或缺的步骤。

芯片封装工艺因最终成品芯片的封装形式不同而有显著差异。以常见的引线键合工艺焊球栅阵列形式封装(WB-BGA封装)为例,其生产过程涵盖了芯片封装的主要工艺步骤。

晶圆切割是一项极为精细且要求严格的工艺技术,旨在将经过CP测试后的晶圆分割为独立的晶粒。在这一过程中,首先需要对晶圆进行初步的品质检测,以确保其符合切割要求。随后,在晶圆的正面覆盖一层保护蓝膜,以防止在切割过程中晶粒受损。根据封装尺寸和散热需求的不同,可能还需对晶圆进行减薄处理,即通过机械研磨的方式减少其厚度。紧接着,利用金刚石刀片或激光切割技术,精确沿着晶圆上预先设定的沟槽(即晶圆划线,这些划线区域在晶圆制造过程中已预留,用于保护切割过程中的晶粒)进行切割。完成这一步骤后,即可获得独立的晶粒。晶圆切割工序对精度的要求极高,任何微小的工艺失误都可能对晶粒的质量产生直接影响。因此,这一过程需要依赖专业的生产设备——晶圆划片机来完成。全球范围内,知名的晶圆划片机制造商包括日本的DISCO和ACCRETECH,以及美国的Slicingtech等。而在国内,晶盛机电和中电科四十五所等厂商也在这一领域取得了显著的成就。

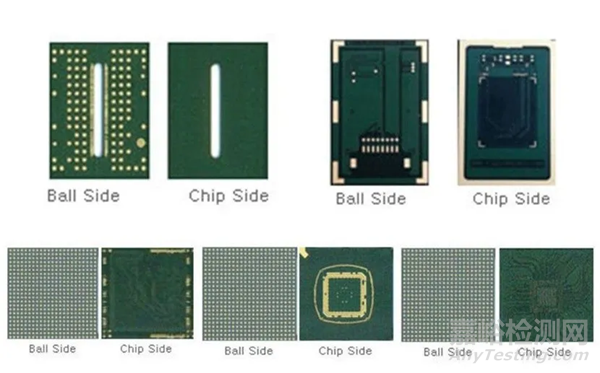

在制造最终芯片的过程中,封装基板(Substrate,简称SUB)发挥着至关重要的作用。它是一种特殊的印刷线路板(Printed Circuit Board,简称PCB),其关键功能在于将晶粒Die的Pad管脚扩展连接至封装后的Ball管脚。因此,必须根据每颗芯片的具体情况和封装尺寸等因素来设计和制造SUB。目前,行业内知名的SUB生产商包括日本的京瓷、中国台湾地区的南亚、欣兴电子和景硕等。在大陆地区,兴森科技、珠海越亚、深南电路和生益电子等企业也在积极努力突破高端芯片封装所需的SUB生产技术。

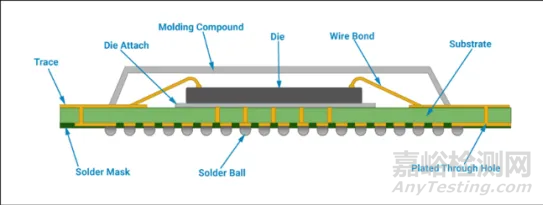

各种SUB正(Chip Side)反(Ball Side)面

Substrate构成了芯片封装的基础结构,类似于建筑的地基。随后,晶粒Die被精确地放置在Substrate的一侧,这一过程被称为Die Attach。晶粒与Substrate之间通过精细的引线键合技术实现连接。为确保芯片的稳定性和安全性,会在其上安装一个金属保护盖,这一过程称为Lid Attach。此保护盖通常采用散热性能优异的合金制成。在另一侧,芯片上会安装锡球,这一过程被称为Solder Ball Mount。随后,通过先进的回流焊工艺,确保锡球与SUB之间形成稳固的连接。至此,芯片封装的基本结构已完成。

封装完成后,芯片会经过严格的质量检测。其中包括使用X-Ray等技术手段,对封装芯片内部的结构进行详细检查,以确保封装质量。此外,还会进行Marking操作,通过激光打印的方式,在芯片表面印上芯片生产商的Logo、产品名称、生产批次等信息。在确保一切质量指标合格后,芯片将进入烘烤流程,即Baking过程。这一步骤的目的是排除芯片封装材料中的湿气和其他可能影响芯片性能的因素,确保芯片在后续的电学性能工作中表现出稳定可靠的特性。

经过这一系列精细的封装工艺生产流程,原始的晶粒Wafer Die最终转变为了成品芯片Chip,为后续的应用打下了坚实的基础。

封装结构

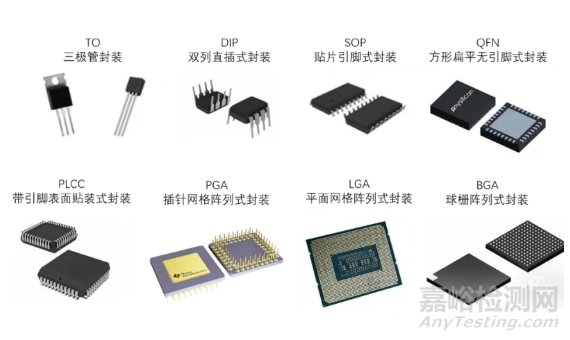

在传统Wire Bonding BGA封装方式之外,目前主流的是Flip Chip BGA,即倒焊封装BGA。此方式之所以能够实现更小的封装尺寸,原因在于将芯片倒装并与基板连接。这一技术首先在Wafer Die Pad上通过wafer bumping工艺形成金属凸点,随后通过这些凸点与下方的Substrate相连。对比前述方式,可清晰看出二者之间的显著差异。芯片的封装类型繁多,若按使用封装材料的不同进行分类,主要可分为塑封芯片、陶瓷封装芯片和金属封装芯片。其中,陶瓷和金属材质的封装主要应用于工作条件极为苛刻的航空航天和军事等领域,同时这些材质的封装成本也相对较高。若从封装结构进行分类,则更为多样,不同芯片种类和应用需求均需要不同结构的封装形式。

不同结构类型的芯片封装示意图

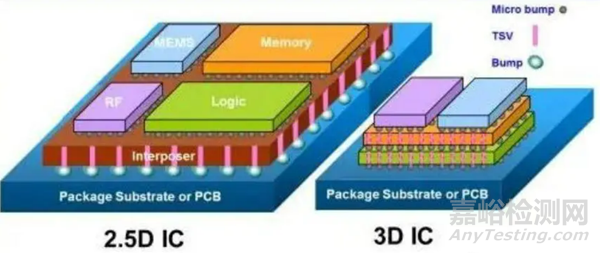

随着市场对高性能芯片需求的不断攀升以及芯片应用领域的日益扩展,封装技术亦在迅速演进。自初始的平面2D封装逐步迈向2.5D乃至3D封装,旨在通过技术的革新推动芯片集成度的持续提升。当前备受瞩目的人工智能大芯片,即AI SoC(System-on-Chip),因需将2至8颗,甚至更多颗高带宽HBM存储晶粒(此类晶粒统称为KGD,即已知确认的功能完好的晶粒,英文全称为Known Good Die)集成封装,故对封装技术提出了更高要求。为确保HBM存储颗粒与主芯片晶粒之间的高速、稳定互联带宽,先进的CoWoS 2.5D封装方式应运而生。

2.5D及3D封装

芯片终测(Final Test)

在芯片正式出货并交付给终端产品客户之前,为确保其功能和质量达标,必须经历一个至关重要的测试环节——终测(Final Test)。此举的必要性源于两方面原因。首先,CP测试虽能有效评估芯片性能,但受限于在Wafer层面通过Probing探针接触的方式,其测试的电源功率和频率均受到一定限制。其次,芯片在封装过程中,可能因工艺等因素造成一定程度的损伤。因此,对封装后的最终成品进行FT测试至关重要,它能有效识别并剔除潜在的质量问题。

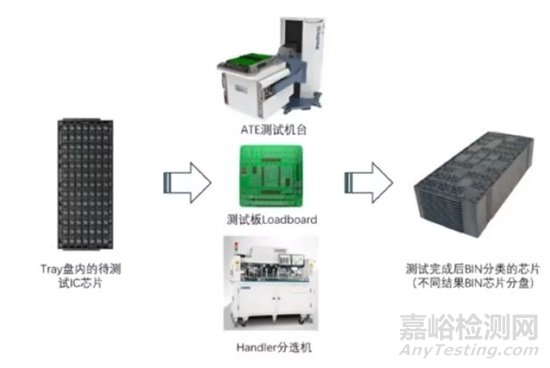

FT测试与CP测试在测试方法上颇为相似,同样依赖于ATE自动测试机台设备。除此之外,还需要测试版(Loadboard)和分选机(Handler)等辅助工具。这些设备和工具共同确保了FT测试的准确性和高效性,为芯片的最终出货提供了坚实的质量保障。

FT测试过程及相关设备测试件

系统级测试(SLT Test)

随着芯片尺寸、功能和封装技术的日益提升,其复杂性亦不断增长,这导致了CP及FT测试的成本显著增加,并面临着测试覆盖率受限的问题。特别是在某些对芯片缺陷率要求极为严格的特殊领域,如自动驾驶类芯片,对测试质量的要求更为严苛。为了有效降低出货缺陷率,即DPPM(百万片失效率),许多芯片在完成FT测试后,增加了额外的SLT测试(系统级测试)环节。

SLT测试的设计基于芯片的实际应用场景,通过精心打造测试板和制定测试流程,力求在测试过程中模拟出真实的芯片业务流。这种测试方法旨在确保芯片在最终出货给客户并应用于实际产品板之前,已经通过了更为贴近“实际应用场景”的严格检验,从而将DPPM缺陷率降低到更低的水平。这一举措不仅提高了芯片的质量,也增强了客户对产品的信心。

芯片封装与测试环节之间存在着紧密的关联,因此产业链中常将典型厂商称为封测厂。深圳市中科系统集成技术有限公司于2011 年成立,在先进封装领域深耕十余年,积累了大量的先进封装设计仿真及工艺开发经验。公司主营业务为:晶圆级封装、IC测试板设计加工、硬件设计开发以及先进封装一站式方案。公司于2021年被芯瑞微(上海)电子科技有限公司全资收购,目前作为国内优秀的先进系统级封装设计一站式服务综合服务供应商,产品广泛应用于航天、车辆、船舶、通信、电子、医疗等众多行业。

芯片封测是半导体集成电路产业链的重要环节,对集成电路芯片的物理外壳保护、功能完整性和性能可靠性至关重要。随着科技的日新月异,未来的封装测试技术将不断向小型化、高密度和高集成度迈进,例如采用3D封装、晶圆级封装等尖端工艺。这些创新技术使得芯片能在更紧凑的空间内实现更多元化的功能和卓越的性能,从而满足人工智能、物联网、5G通信、车载电子等多元化应用领域对芯片日益增长的需求。这不仅推动了半导体集成电路行业的蓬勃发展,更为整个科技产业注入了新的活力与机遇。

来源:Internet

关键词: 半导体芯片封装测试