嘉峪检测网 2024-12-22 09:40

导读:常见的ESD模型有:人体模型(HBM)、机器模型(MM)、充电组件模型(CDM)、国际电子工业委员会标准(IEC)、传输线脉冲模型(TLP)、快速传输线脉冲模型(VF-TLP)、人体金属放电模型(HMM)。

静电放电(Electro-Static Discharge)现象经常发生在我们周围,例如冬天脱羊毛衫出现的劈啪声、有时手触碰到金属把手会有触电的感觉,这些都是静电放电现象。通常这种放电现象对人体不会有什么影响,甚至绝大多数情况下我们都毫无感觉,但是对于集成电路芯片领域,静电放电就是一个不可忽视的重大问题,因为静电放电可以在短时间内产生几百甚至几千伏高压,虽然持续时间很短,但是足以给芯片的某个部位造成不可逆的热损伤。

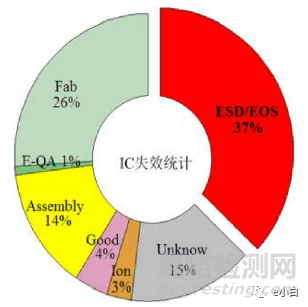

芯片ESD失效主要分成两种情况。第一种情况是不可逆热损坏,这种损坏会导致芯片功能失效,不能继续使用,最典型热击穿包括:金属熔断、介质击穿、PN结击穿。第二种情况是功能退化,功能退化会导致芯片性能下降,如芯片寿命降低、鲁棒性降低、性能参数退化等,但是功能退化不会使芯片直接失效,芯片仍然可以继续使用。美国国家半导体公司对IC产品的失效原因的调查数据如下图所示,结果表明:因静电放电(ESD)或电气过应力(Electricl Over Stress,EOS)产生的失效,约占失效IC产品失效总数的37%。

常见ESD模型

常见的ESD模型有:人体模型(HBM)、机器模型(MM)、充电组件模型(CDM)、国际电子工业委员会标准(IEC)、传输线脉冲模型(TLP)、快速传输线脉冲模型(VF-TLP)、人体金属放电模型(HMM)。

其中人体模型(HBM)、机器模型(MM)、组件充电模型(CDM)为芯片级测试模型,主要是模拟芯片本身的ESD防护能力。一个质量好的芯片,都需要有相应的ESD防护设计,芯片级ESD模型主要研究ESD防护设计与芯片核心电路的协同工作能力。

国际电子工业委员会标准(IEC)、人体金属放电模型(HMM)为系统级测试模型。系统级模型主要是研究一个成型的电子产品的ESD防护能力。一个质量好的电子产品,除了内部芯片需要有相应的ESD防护设计外,芯片外部还需要并联相应ESD/EOS防护器件作一级防护,泄放初期电流,通常这种器件为瞬态电压抑制器。

传输线脉冲模型(TLP)与快速传输线脉冲模型(VF-TLP)为器件级测试模型,主要研究ESD防护器件的性能。用于ESD防护的基本器件都需要进行TLP与VF-TLP测试来确定其ESD参数,评估其 ESD性能。

1.人体模型(HBM)

人体模型(HBM)主要是模拟人体与芯片接触过程中导致芯片携带静电的情况。人体在某种条件下携带了大量静电荷,随后与芯片接触,人体所带静电荷转移到芯片上,其中人体、芯片、地组成放电通路。下图是人体与芯片接触示意图。

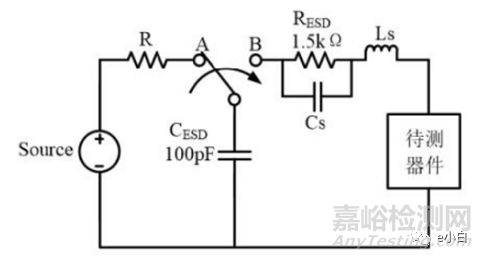

人体放电模型的等效电路如下图所示,主要由放电电容、1.5KΩ电阻、寄生参数与DUT(待测器件)组成,其中 1.5KΩ是模拟人体的寄生电阻。如图下图所示,首先开关拨向B,电源向100pF电容充电,这是模拟人体通过摩擦接触等情况使得自身携带静电荷变成静电源的过程。随后开关拨向A,电容开始放电,这是模拟人体,芯片,地构成放电通路进行放电的过程。在HBM模型下,由于人体的寄生电阻较大,因此放电波形的上升沿较缓,大约为10ns,峰值电流一般小于5A。

美国静电协会根据芯片在HBM情形下能够承受静电电压的能力划分了严格的ESD防护等级,如下表所示。一般合格的ESD防护设计需要使芯片的HBM等级达到4000V。

2.机器模型(MM)

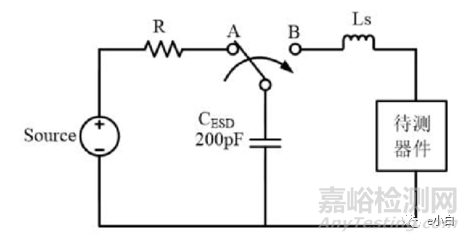

机器模型与人体模型类似,不同的是机器模型是模仿金属与芯片接触形成放电通路的模型。下图是金属模型的等效电路图,由于金属是导体,寄生电阻很小,因此相较于HBM的等效电路图,MM模型的等效电路图中没有了1.5KΩ的电阻。当开关拨向B时,模拟的是金属或者机器在某种情况下携带静电荷变成静电源的过程。当开关拨向A时,金属,芯片,地三者形成导电通路,静电荷从外部金属开始向芯片转移。由于金属的内阻很小,因此MM模式下,放电波形的上升时间很快,约为 6~8ns。MM模型下放电波形的持续时间与HBM模型下放电波形的持续时间相当,大约为100ns。峰值电流相比HBM模型明显增大,可以达到5A。

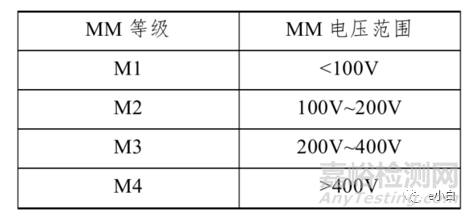

与HBM模型一样,美国静电协会也根据芯片在MM情形下能够承受静电电压的能力划分了严格的ESD防护等级,如下表所示。一般芯片合格的ESD防护设计应该使芯片的MM等级为400V。值得一提的是,在同等条件下,MM的防护等级约为HBM的十分之一。

3.充电组件模型(CDM)

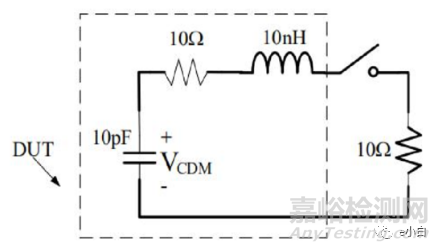

充电组件模型(CDM),主要模拟的是封装后的芯片在运输过程中芯片接触到其他物体或者感应出静电荷,自身成为静电源后,大量静电荷通过IO管脚从芯片内部流出产生的静电放电现象。该模型等效电路如下图所示,与HBM和MM不同的是,该模型是芯片本身作为DUT进行放电。CDM模式下,放电回路总电阻很小,放电波形的上升时间极短,约为0.2ns。脉冲持续时间也很短,大概为HBM模式下的十分之一到二十分之一。由于放电回路的寄生电阻很小,放电波形的峰值电流很大,能达到10至20A。

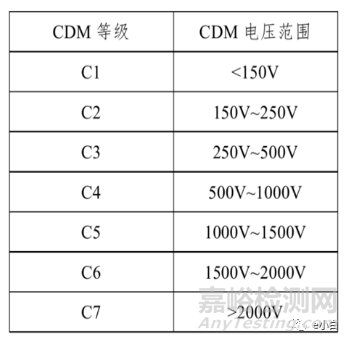

与HBM、MM模型一样,美国静电协会也根据芯片在CDM情形下能够承受静电电压的能力划分了严格的ESD防护等级,如下表所示。CDM模型的放电波形虽然峰值电流很大,但是持续时间很短,因此波形的总能量并不大,冲击力并没有HBM与MM模型强。在工业生产中,一般要求芯片的CDM等级为500~100V。

4.人体金属放电模型(HMM)与国际电子工业委员会标准(IEC)

HMM以及IEC均是系统级ESD模型,与之前讨论过的芯片级模型不一样,系统级ESD模型的测试对象主要是整个电子产品。

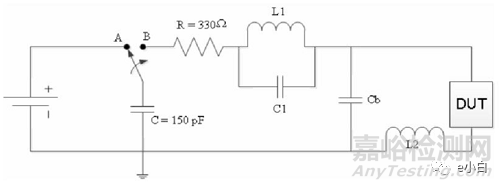

人体金属模型主要模拟带有静电荷的人体通过金属、机械等与芯片管脚相接触,发生电荷转移的ESD过程。HMM模型主要用来评价芯片在电子系统在ESD测试中的鲁棒性。下图是目前使用最多的HMM的等效电路图。当开关拨向A时,模拟的是人体携带静电荷成为静电源的过程,图中所示充电电容为150pF。当开关拨向B时,人体、金属、芯片、地形成放电通路,图中L1、C1、L2均为放电回路寄生参数。其放电波形的上升时间很短,大约为0.7ns,持续时间约为60ns。

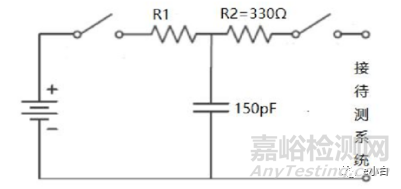

IEC模型主要是使用电子枪对待测系统进行ESD放电测试。测试模式主要有两种,分别为空气放电与接触放电。IEC模型的等效电路如下图所示,该模型的放电波形的上升时间与HMM放电波形上升时间相当,约为0.7ns,放电波形的持续时间约为80ns,峰值电流约为20A。

5.传输线脉冲模型(TLP)与快速传输线脉冲模型(VF-TLP)

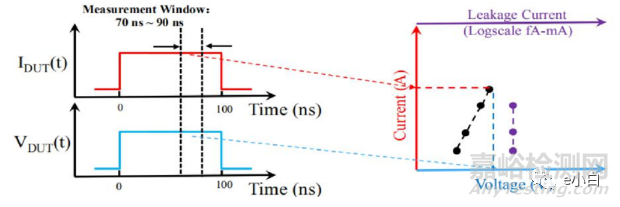

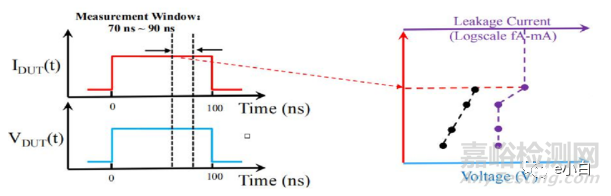

TLP(Transmission Line Pulse)与VF-TLP(Very Fast Transmission Line Pulse)测试技术是一种通过测量时域的电流电压来研究集成电路和器件ESD特性的测试方法,属于器件级的ESD测试方法。在TLP测试模式下,脉冲发生器产生一系列上升时间为10ns、下降时间为10ns、脉宽可调,幅值可调的离散电压方波。其中脉宽的调节范围为100ns~1000ns,不过在HBM模式下,脉宽一般设置为100ns,幅值的调节范围为0~1000V。方波在传输线上产生入射波和反射波,将入射波与反射波叠加,得到待测器件关于时间的瞬态I-V曲线。分别取出整个测量周期中70%-90%时间段内的电压值的平均值以及电流值的平均值作为TLP测试曲线的一个坐标点,如下图所示。

TLP测试曲线中除了有脉冲方波下的I-V曲线,还有一条漏电流线,该曲线主要用来实时监控器件的漏电流。其绘制方法与I-V曲线一致,每当一个TLP脉冲点绘制完成后,转换开关就会将电压源从脉冲发生器切换至直流供电,同样取一个周期内70%-90%的平均值绘制出来的点就是漏电坐标点,如下图所示。

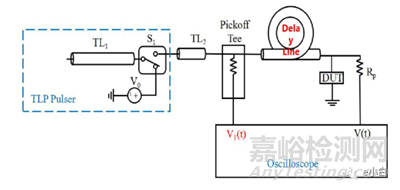

TLP脉冲发生器由长度为L的充电传输线TL1、开关S和高压电源V0组成,其原理图如下图所示。其中高压电源V0用来改变脉冲方波的幅度,TL1的长度决定TLP脉冲波的脉度。标准TLP的脉冲宽度为100ns。

VF-TLP与TLP原理大致相同,不同的是TLP的脉冲发生器产生的是上升沿10ns,脉宽100ns 的方波,用来模拟HBM模型。VF-TLP产生的是上升沿0.1ns,脉宽10ns的方波,用来模拟CDM模型。其原理图如下图所示。VF-TLP采用的是低损电缆线,用来降低寄生参数,图中延迟线的作用是将入射波和反射波分开,方便算出电流。

ESD模型总结

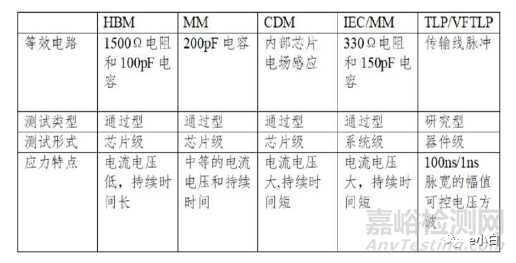

HBM的放电波形持续时间较长,携带的能量很大,可以直接打穿MOS的栅氧端或者源漏端。因此由HBM模型引起的ESD失效主要为MOS管的源漏击穿与栅氧击穿。虽然CDM模型放电波形的峰值电流较大,但是持续时间短,因此CDM放电波形所携带的能量并没有HBM模型那么大。由CDM模型引发的ESD失效点形状就小很多,多为针孔状的栅氧击穿。ESD模型总结比较如下表所示。

来源:e小白