嘉峪检测网 2025-01-10 19:14

导读:本文介绍了汽车自动驾驶及智能座舱计算芯片与车规级芯片AEC-Q100认证。

1、自动驾驶计算芯片

1.1 自动驾驶计算芯片简介

自动驾驶芯片是指可实现高级别自动驾驶的 SoC 芯片。CPU作为通用处理器,适用于处理数量适中的复杂运算。除了满足计算要求,还能处理复杂的条件和分支以及任务之间的同步协调。

评估芯片的性能,一般采用 PPA 即 Power(功耗),Performance(性能),Area(面积)三大指标衡量。智能驾驶领域,峰值算力成为衡量自动驾驶芯片的最主要指标。地平线在 2020 全球人工智能和机器人峰会提出了芯片 AI 性能评估方式 MAPS(Mean Accuracy-guaranteed Precessing Speed),地平线认为最真实的 AI效能实际上由三要素组成,分别为理论峰值计算效能、有效利用率、AI算法效率。(1)理论峰值计算效能,TOPS/W、TOPS/$,即传统理论峰值衡量的方法;(2)芯片有效利用率,把算法部署在芯片上,根据架构特点,用编译器等系统化解决一个极其复杂的带约束的离散优化问题,得到一个算法在芯片上运行的实际利用率,这是软硬件计算架构的优化目标;(3)AI算法效率,每消耗一个 TOPS 算力,能带来多少实际的 AI 算法的性能,它体现的是AI 算法效率的持续提升。

1.2 自动驾驶计算芯片的发展趋势

在自动驾驶等核心计算场景中,传统通用CPU由于计算效率低,难以适应AI计算要求,GPU、FPGA以及ASIC等AI芯片凭借着自身特点,在边缘端和云端有着优异表现,应用更广。从技术趋势看,短期内GPU仍将是AI芯片主导,长期来看,ASIC是终极方向。从市场趋势看,全球AI芯片需求将保持较快增长势头,云端、边缘芯片均具备较大增长潜力,预计未来5年市场增速将接近50%;国内芯片技术虽然基础较弱,但随着AI应用的快速落地,AI芯片需求快速放量为本土芯片企业技术和能力成长创造机遇。自动驾驶对算力、时延和可靠性要求严苛,目前多使用GPU+FPGA的解决方案,后续随着算法的稳定以及数据驱动,ASIC有望获得市场空间。

CPU芯片上需要很多空间来进行分支预测与优化,保存各种状态以降低任务切换时的延时。这也使得其更适合逻辑控制、串行运算与通用类型数据运算。以GPU与CPU进行比较为例,与CPU相比,GPU 采用了数量众多的计算单元和超长的流水线,只有非常简单的控制逻辑并省去了 Cache。而 CPU 不仅被 Cache 占据了大量空间,而且还有复杂的控制逻辑和诸多优化电路,相比之下计算能力只是很小的一部分。

随着自动驾驶汽车智能化水平越来越高,需要处理的数据体量越来越大,高精地图、传感器、激光雷达等软硬件设备对计算提出更高要求,因此在 CPU 作为通用处理器之外,增加具备 AI 能力的加速芯片成为主流。

常见的 AI 加速芯片包括 GPU、ASIC、FPGA 三类:

(1)GPU:适用于处理数量庞大相对简单的运算。GPU 拥有一个由数以千计的更小、更高效的 ALU 核心组成的大规模并行计算架构,大部分晶体管主要用于构建控制电路和 Cache,控制电路相对简单,GPU的计算速度拥有更强大的处理浮点运算的能力,更擅长处理多重任务,比如图形计算。

(2)FPGA:现场可编程门阵列,它是在PAL、GAL、CPLD 等可编程器件的基础上进一步发展的产物,是作为专用集成电路领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

(3)ASIC:一种为专门目的而设计的集成电路。是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。ASIC的特点是面向特定用户的需求,在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

“CPU+XPU”是当前自动驾驶 SoC 芯片设计的主流趋势。根据 XPU 选择不同,可以分为三种技术路线:CPU+GPU+ASIC、CPU+ASIC 以及 CPU+FPGA三类。

(1)“CPU+GPU+ASIC”,主要代表英伟达、特斯拉 FSD 以及高通 Ride。英伟达 Xavier 和特斯拉 FSD 采用“CPU+GPU+ASIC”的设计路线,英伟达Xavier 以 GPU 为计算核心,主要有 4 个模块:CPU、GPU、以及两个 ASIC芯片 Deep Learning Accelerator(DLA)和 Programmable Vision Accelerator(PVA);特斯拉 FSD 芯片以 NPU(ASIC)为计算核心,有三个主要模块;

(2)“CPU+ASIC”,主要代表 Mobileye EyeQ5 系列和地平线征程系列。

Mobieye EyeQ5 和地平线征程系列采用“CPU+ASIC”架构,EyeQ5 主要有 4个模块:CPU、Computer Vision Processors(CVP)、Deep Learning Accelerator(DLA)和 Multithreaded Accelerator(MA),其中 CVP 是针对传统计算机视觉算法设计的 ASIC;地平线自主设计研发了 Al 专用的 ASIC 芯片 Brain Processing Unit(BPU)。CPU、GPU 和 Neural Processing Unit(NPU)。

(3)CPU+FPGA,主要代表Waymo。与其余厂商不同,Waymo采用“CPU+FPGA”的架构,其计算平台采用英特尔Xeon12核以上 CPU,搭配Altera 的 Arria 系列 FPGA。

1.3 自动驾驶计算芯片的产业格局

目前各家发布的最新芯片平台大多可以支持 L3 或 L4 级的算力需求,英伟达相对领先,国产仍有一定差距。英伟达单颗 Orin 的算力可以达到 254TOPS,而 2022 年落地的车型中搭载 4 颗Orin 的蔚来 ET7 和威马 M7 其巅峰算力将超过 1000TOPS,高通骁龙 Ride 平台的巅峰算力预计在 700-760TOPS,Mobileye 也推出了面向高阶自动驾驶的 EyeQ6 Ultra,算力达到 176 TOPS。

我国车载计算类芯片总体处于较为初期发展阶段。目前在车载算力平台领域,CPU、GPU、FPGA和ASIC均有国内龙头企业实现自主研发产品,并且在大部分技术指标上与国际大厂实现对标,部分中控、高算力芯片产品已有成功的车规应用经验。但从全行业角度,国产车载计算芯片在产品可靠性、车规应用经验方面仍有一定差距,国产替代空间巨大。

长期看,本土计算芯片供应商有望满足本土整车大部分需求。自主品牌车厂在核心芯片环节加快发展多供应商策略,积极推进国产供应商的测试与定点,同时国内各汽车AI企业、消费芯片厂商、初创汽车芯片厂商积极投入布局研发,逐步实现在车上应用。

2、智能座舱计算芯片图片

2.1 智能座舱计算芯片简介

座舱域控制器以集中化的形式,满足汽车轻量化、智能化的诉求,支撑汽车座舱的丰富功能与强交互性。从硬件层面来看,座舱域控制器由一颗主控座舱计算芯片SoC以及外围电路构成,外围电路包括存储芯片(如LPDDR、NOR Flash)、通信芯片(如以太网交换芯片)、音视频数据接口以及相关处理芯片(如ISP、DSP、解串行芯片)构成。经操作系统与应用生态赋能之后,座舱域控制器融合了座舱内仪表显示、信息娱乐、导航、HUD、DOMS等各项功能,连接了显示屏、摄像头、麦克风、收音机等多个外设,是座舱空间体现科技感的直接载体。

座舱计算芯片SoC是智能座舱的核心,由处理器、存储器、系统控制、加密算法、通信传输等部分组成。

(1)处理器

座舱SoC的核心,通常包括CPU、GPU、VPU、NPU等异构处理器。1)CPU(Central processing unit)是中央处理器,其核的个数以及核的主频很大程度上决定了信息处理的最终性能。同一系列不同档次的芯片通常会通过CPU核的增减进行性能的分档,例如NXP i.MX 8系列芯片Quad、QuadPlus、QuadMax三款芯片的性能差异主要通过搭载0、1、2个Arm Cortex A72核心实现;2)GPU、VPU(Graphic processing unit、Video processing unit)等是专门对图像、视频信息进行处理、渲染的处理器,分担CPU的工作压力,提供更好的音视频体验;3)NPU(Neural-network processing unit,神经网络处理器)采用“数据驱动并行计算”架构,负责处理AI方面的计算需求。

(2)存储器

芯片内部的存储器用于储存未处理过的数据和已经处理过的数据,提高数据处理的效率,包括DRAM、SD、eMMC、NAND等,以及QSPI、SPI等数据传输接口。

(3)安全与系统控制

前者包括各类加密算法,后者包括电源管理、时钟等控制系统。

(4)通信接口

包括内部通信的PCIe、LVDS、USB、SATA、CAN、以太网等通用数据接口,以及与座舱显示屏、摄像头之间进行视频输入输出的DSI(显示屏信号接口)、CSI(摄像头信号接口)、HDMI、eDP、DP等。

座舱芯片的算力决定了座舱域控制器的数据承载能力、数据处理速度以及图像渲染能力,从而决定了座舱内屏显数量、运行流畅度以及画面丰富度,进而塑造了整个座舱空间内的智能体验。尽管域控制器由国内外多家厂商供应,但所基于的芯片平台有限,基本集中在高通、瑞萨、恩智浦、TI等芯片厂商,座舱芯片的集中度明显高于域控制器。

随着智能化程度加深,座舱计算芯片算力的要求也越来越高。根据IHS测算,2024年智能座舱对座舱芯片CPU的算力需求在89kDMIPS,算力需求相比2021年增长3倍以上。目前主要座舱芯片厂商所提供的座舱芯片算力具有明显差异,高通、三星最新芯片平台算力为80-150kDMIPS范围,传统汽车芯片厂商瑞萨、恩智浦、德州仪器CPU算力大致为25-50kDMIPS范围。

2.2 智能座舱计算芯片的发展趋势

随着汽车E/E架构沿着“分布式”“域集中式”“中央计算式”的方向演进,座舱芯片方案也将分三个阶段演进——“单芯单屏”“单芯多屏”“融合发展”。

(1)单芯单屏:信号传输以及成本方面存在劣势

分布式架构下,不同座舱电子设备由不同控制器控制,表现为“单芯单屏”。这样的解决方案在座舱功能贫乏的过去是合适的:a)不同屏幕之间不用考虑信息交互;b)对芯片的性能要求不高,成本可控;c)仪表盘与娱乐屏运行不同系统,“单芯单屏”解决方案易于实现。

随着消费者愈发强调车内体验感,液晶仪表盘取代机械式仪表盘,娱乐屏所承载的数据量加大,不同电子设备之间数据交互频次增多。“单芯单屏”形态难以满足市场需求。一是跨芯片信号传输存在延迟。智能化时代,座舱电子之间信息交互频繁,例如仪表盘中的行车信息就会与中控导航发生数据交互。为实现多屏联动,设备间需要进行高速率传输。在“单芯单屏”中,不同芯片之间通过CAN或LIN总线传输,信号传递速率遇到瓶颈。二是成本压力上升。为体现汽车“科技感”,仪表盘信息丰富度与娱乐屏内容流畅度大幅增加,这对单颗芯片的性能提出较高的要求,单颗芯片价格不可避免地上升。同时,HUD、流媒体后视镜等新的电子设备出现,抬高了座舱电子的单车成本。

(2)单芯多屏:顺应集中化架构的主流方案

单芯多屏,指的是用一个座舱SoC芯片完成对多个座舱电子设备信号的处理和控制。伟世通座舱域控制器SmartCore首次整合不同控制器,将全数字式仪表盘与中央信息显示屏的功能集成在一个芯片上,实现“单芯多屏”,顺应汽车E/E架构集中化趋势。

“单芯多屏”成为解决“单芯单屏”信号传输延迟、单车成本承压的主流方案。其一是解决信号传输延迟问题。根据Cerebras数据,芯片内数据传输速率可达到100 PB/s,是芯片间最快接口通信速率的10万倍。单芯多屏将芯片间通信转化为芯片内通信,传输速率有望提高。此外,从解决成本问题角度,芯片数量由多个减少至一个,虽然单颗价值量有所上升,但整体来看具有成本优势。

但芯片的集成引发了另一个问题——跨系统运行。一般而言,数字液晶仪表盘涉及车辆安全,需要满足ASIL-B标准,通常采用QNX或Linux系统;娱乐系统需要运行丰富的娱乐功能,通常采用Android系统。“单芯单屏”方案下,不同系统通过不同芯片支持,不存在跨系统问题;而“单芯多屏”方案中,跨系统运行所带来的计算效率的降低较为明显。

硬隔离、虚拟机技术的发展,有望解决这个难题。1)硬隔离(Hardware partition)是在不同系统之间对硬件资源进行分配,提前划分各系统所能访问的计算资源以及内存、外围设备等资源,各系统之间不得互相访问所属硬件资源。例如,恩智浦i.MX 8 QM采用硬件分区将SoC划分为仪表系统和娱乐系统,实现前者运行Linux系统、后者运行Android系统。2)虚拟机(Hypervisor)是在操作系统和硬件之间插入Hypervisor层,根据虚拟机对计算单元、内存等的调度,实现对硬件资源的动态分配。前文中提及的伟世通SmartCore采用的就是虚拟机技术。

(3)跨域融合:与自动驾驶芯片合二为一

中央计算式架构下,中央计算芯片承担了自动驾驶、智能座舱、整车控制三方功能,是TB数量级海量数据的枢纽,这要求中央计算芯片具备更大的数据吞吐能力以及更快的数据处理能力;更多的数据处理工作意味着会产生更多的功耗热量,这要求更精巧的硬件参考设计能力;ADAS系统、座舱系统、整车控制系统的复杂融合系统,要求具备更强的软件开发能力。

中央计算架构需要技术难度更高的软件、硬件能力支持,这或是制约整车架构进一步向更集中阶段演进的原因。当前座舱芯片与自动驾驶芯片处于独立发展阶段,当硬件算力、架构设计、软件开发能力进一步提高,汽车整车架构迈入“中央计算式”时,座舱芯片将与自动驾驶芯片有望实现融合发展。

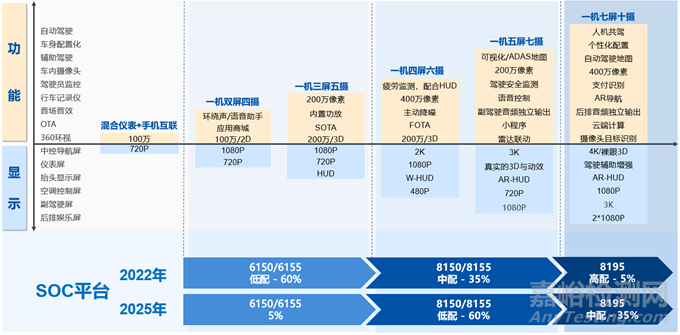

博世座舱芯片演进路径

2.3 智能座舱计算芯片的竞争格局

海外供应商格局趋于明朗,两大阵营分庭抗礼。

当前海外主要供应商可以划分为两大阵营:一是以恩智浦、瑞萨、德州仪器等为代表的“传统汽车芯片”厂商,在传统汽车MCU、ECU芯片业务之外,顺应智能化趋势布局座舱芯片领域;二是以高通、三星等为代表的“消费级芯片”厂商,切入汽车座舱领域,复用其在消费电子领域深厚的技术积累。

当下,传统汽车芯片厂商占有份额仍然较大。根据高工智能汽车研究院数据,恩智浦、瑞萨、德州仪器三家传统汽车芯片厂商是智能座舱芯片的主要供应商,这主要是由“中低端车型销量占比较大”的汽车销售结构决定的。传统汽车芯片厂商在智能化转型中节奏偏慢,除满足车规级安全外,性能不及消费级芯片厂商。瑞萨R-CAR H3采用16nm制程,而恩智浦i.MX 8系列、德州仪器Jacinto 7均基于28nm制程设计,CPU算力最高40kDMIPS。

消费厂商芯片在性能方面具有明显优势,高通几乎垄断高端座舱芯片市场。高通、三星最新款座舱芯片已采用5nm制程。高通骁龙8295在2024年成为智能座舱芯片主流标配。5nm工艺、CPU/GPU/AI性能大幅提升,相较前代8155 CPU算力提升2倍,GPU提升2-3倍,AI算力提升8倍,被广泛应用于奔驰E级、吉利银河E8、小鹏X9、蔚来ET9、小米SU7、极越01、零跑C10等多款车型。

消费厂商切入汽车座舱赛道具有天然优势。一方面,当前智能座舱的算力需求仍未超出智能手机的范围。罗兰贝格预计,未来5年内,高端手机芯片的算力仍能支持下一代座舱电子算力需求。另一方面,消费芯片厂商在手机等消费电子领域已形成规模优势,能够实现低成本开发。而新入局者在固定资产、研究开发投入等方面沉没成本较多,能否达到盈亏平衡点有赖于定点车型合作情况以及销售情况,初期成本较高。

我国座舱芯片处于初期发展阶段。从时间上看,我国座舱芯片市场发展处于初期阶段;从入局厂商看,我国市场聚集了汽车AI芯片企业、消费芯片厂商、初创汽车芯片厂商。其中,汽车AI企业如地平线、黑芝麻等,产品可支持座舱领域应用;消费芯片厂商如华为、全志科技等,在手机、电脑、智能家居、通信等领域广泛布局;另外,一批汽车芯片初创公司也纷纷入局,例如芯驰科技成立于2018年(2020年发布X9系列助力座舱智能化)、芯擎科技成立于2018年(基于7nm制程设计SE1000,公司预计2022年上车测试)。

国内座舱芯片竞争格局尚未确定。目前除小鹏等个别主机厂与座舱芯片厂商直接对接外,大多通过与座舱域控制器Tier 1厂商合作的方式塑造座舱的智能化。目前,已有几款芯片有落地场景,如华为麒麟990A搭载于北汽极狐αS、地平线征程2已经在长安UNI-K等多款车型中落地;芯擎科技绑定吉利汽车。另外,根据芯驰科技披露,芯驰目前已服务250余家客户,覆盖中国70%的车企,获得50余个定点项目。

经历2021年汽车芯片的供给紧缺,自主品牌车厂在核心芯片已采取多供应商策略,积极推进国产供应商的测试与定点。在不断扩大市场应用基础上,国产座舱SoC芯片与国际巨头的差距会逐渐缩小。

下表中梳理了目前主流智能座舱SoC芯片:

目前主流智能座舱SoC芯片对比

3、 智能驾驶与智能座舱计算芯片的准入门槛AEC-Q100

① AEC-Q认证是国际汽车电子领域的准入门槛

AEC即Automotive Electronics Council,是美国汽车电子委员会的简称。AEC由克莱斯勒,福特和通用汽车发起并创立于1994年,目前会员遍及全球各大汽车厂、汽车电子和半导体厂商,符合AEC规范的零部件均可被上述三家车厂同时采用,促进了零部件制造商交换其产品特性数据的意愿,并推动了汽车零件通用性的实施,为汽车零部件市场的快速成长打下基础。AEC-Q为AEC组织所制订的车用可靠性测试标准,是零件厂商进入汽车电子领域,打入一级车厂供应链的重要门票。

AEC-Q100是AEC的第一个标准,主要是针对车载应用的集成电路产品所设计出的一套应力测试标准,此规范对于提升产品信赖性品质保证相当重要。AEC-Q100是预防可能发生各种状况或潜在的故障状态,对每一个芯片进行严格的质量与可靠度确认,特别对产品功能与性能进行标准规范测试。

② 要求通过AEC-Q100标准的车用集成电路IC

单颗IC:控制类芯片、驱动类芯片、计算类芯片、存储类芯片、传感类芯片、通信类芯片、功率类芯片、电源类芯片、安全类芯片、模拟芯片等。

③ AEC-Q100:集成电路试验方法零件工作温度等级定义

▸等级0:环境工作温度范围-40℃~150℃;

▸等级1:环境工作温度范围-40℃~125℃;

▸等级2:环境工作温度范围-40℃~105℃;

▸等级3:环境工作温度范围-40℃~85℃。

④AEC-Q100车用IC产品验证流程

⑤ AEC-Q100测试项目分组

群组A--加速环境应力测试(PC、THB/HAST、AC or UHAST or TH、TC、PTC、HTSL)共6项测试

群组B--加速生命周期模拟测试(HTOL、ELFR、EDR)--共3项测试

群组C--封装组装完整性测试(WBS、WBP、SD、PD、SBS、LI、BST)--共7项测试

群组D--芯片制造可靠性测试(EM、TDDB、HCI、BTI、SM)--共5项测试

群组E--电性验证测试(TEST、HBM、CDM、LU、ED、FG、CHAR、EMC、SC、SER、LF)--共11项测试

群组F--缺陷筛选测试(PAT、SBA)--共2项测试

群组G--腔体封装完整性测试(MS、VFV、CA、GFL、DROP、LT、DS、IWV)--共8项测试

来源:Internet