嘉峪检测网 2025-02-15 20:06

导读:本文分析了超结MOSFET EMC问题产生原因。

采用电荷平衡理论的超结器件能够显著减少高压MOSFET的导通电阻,由于导通损耗与导通电阻成正比,导通损耗方面具有很大的优势。开关转换时段越短,开关功率损耗越低。由于MOSFET是单极器件,寄生电容是开关转换的唯一限制因素,若要降低开关损耗,需要降低寄生电容。

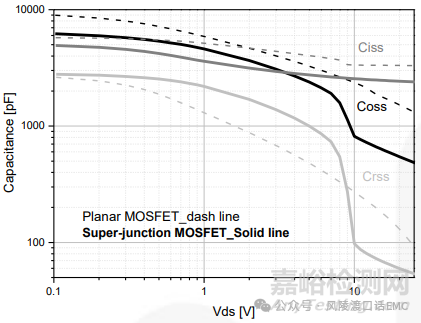

超结MOSFET的输入电容和米勒电容都显著降低,输出电容曲线相差不大,差别主要是更高的非线性程度,平面MOSFET与超结MOSFET的电容曲线对比如下图所示:

图1:平面MOSFET与超结MOSFET电容比较

超结MOSFET的CISS电容的线性基本保持,CRSS和COSS表现出很强的非线性,CRSS在约10V漏源极电压处迅速降低,电容非线性导致极强dv/dt与di/dt。快速开关降低开关损耗,同时也有负面效应,增加EMI风险、栅极振荡、较高的漏源极电压峰值,控制最大开关速度对于获取不带负面效应的超极结MOSFET极端性能来说非常的重要。

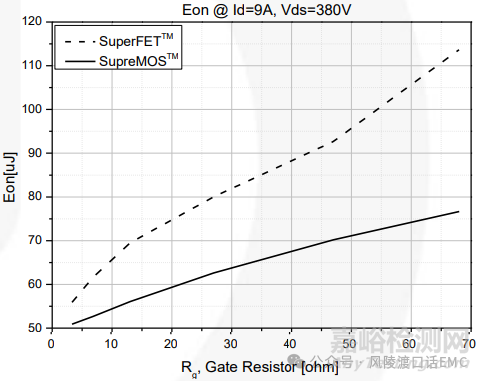

1、栅极电阻的影响分析

栅极驱动设计中的一个关键控制参数为外部串联的栅极电阻(RG),栅极电阻能够抑制漏源极峰值电压并能够防止功率MOSFET中导线电感和寄生电容产生的栅极振荡。还能够在导通和关断期间减缓电压和电流上升速度(dv/dt)和(di/dt)。

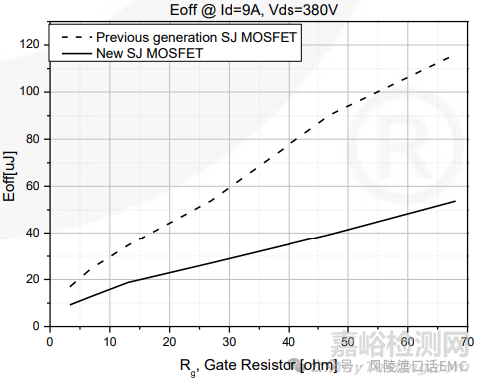

RG的选择优化非常重要,RG值过小会造成MOSFET开关关闭时漏源极间的dv/dt过高;RG值过大会增加损耗,并降低效率,根据器件选型选择合适的RG参数非常重要。

图2:栅极电阻与导通能量损耗(Eon)

图3:栅极电阻与关断能量损耗(E off)

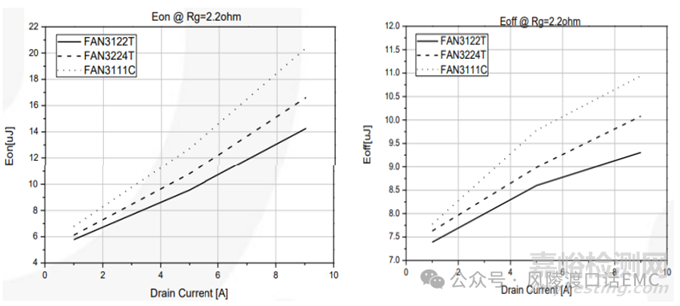

2、驱动IC电流驱动能力的影响

驱动器是控制电路和功率MOSFET之间的接口,驱动电路放大控制信号至所需要电平,驱动器的主要功能是控制MOSFET的开关状态,高功率应用中需要峰值电流,能为寄生电容快速充放电,从而提高MOSFET的开关效率,开关动作和功率耗散取决于输出驱动器的电流能力,而MOSFET栅源极介于阀值电平和米勒效应平台电压之间。

图4:不同串联电阻对损耗的影响(IC驱动能力较小时)

3、源极寄生电感的影响

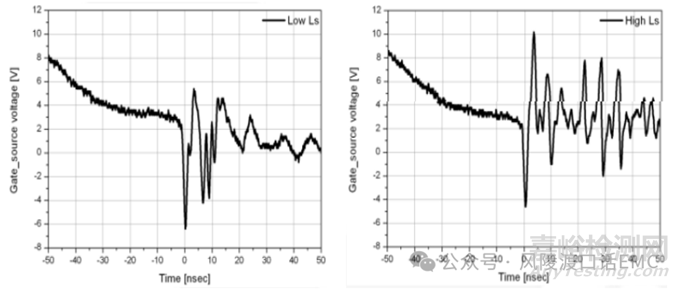

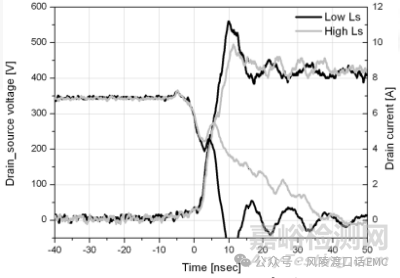

MOSFET源极寄生电感LS值较低时,尽管由于快速转换速度导致栅源极负电压和漏源极过冲电压会稍高,其关断损耗和栅极振荡都较低。MOSFET源极寄生电感LS值较高时,关断损耗和栅极振荡也较高。

超结MOSFET的极快开关速度可能导致开关过程中出现严重的电压和电流振荡,在实际应用中,主要包括元件引脚寄生电感、PCB布线寄生电感、振荡问题通常受控于杂散电感、而非杂散电容,尤其是在中低压电源中,减小开关振荡的最佳方式是最大限度地减少电感。

图5:LS值较低时VGS振荡波形与LS值较高时VGS振荡波形对比

图6:LS值对VDS和ID波形的影响

4、器件封装寄生效应

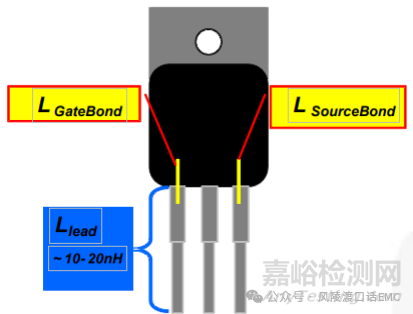

图7:插件MOSFET引脚寄生电感

封装对性能的影响有限,是因为内部栅极和源极焊接导线长度是固定的,而引线长度可以改变,以减少封装的源电感,MOSFET封装引线电感典型值为10nH。影响MOSFET开关过程产生寄生振荡的条件除外部布线的寄生电感、MOSFET寄生电容产生的寄生振荡之外,MOSFET内部Bonding线寄生电感、插件MOSFET引线寄生电感、与MOSFET引脚寄生电容也是产生寄生振荡的重要原因。

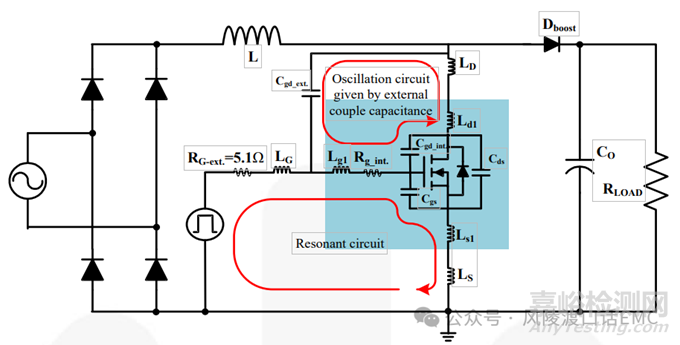

图8:Boost PFC MOSFET内外部寄生参数等效图

MOSFET开关速度提高时,MOSFET的漏源极产生振荡电压,原因是漏极引线寄生电感LD产生的。MOSFET关断时,漏源电压VDS免通过漏极寄生电感LD、CGD电容、栅极寄生电感LG形成振荡回路(理想情况下)。实际应用中寄生参数包括MOSFET管内部的寄生电感LG1、LD1、CGD(内部)、CGD(外部)、LD寄生电感构成的振荡回路。

栅极电阻很小时,振荡电路Q值变得很大,CGD和LG1之间产生很大的振荡电压,产生寄生振荡。由关断瞬间的漏极负电流,在LS和LS1电感上产生压降,并通过栅源电压产生振荡,寄生振荡导致栅源极击穿电压、EMI恶化、较大的开关损耗,严重导致MOSFET失效。

来源:风陵渡口话EMC

关键词: MOSFET