嘉峪检测网 2025-05-05 14:35

导读:本文介绍了EMC整改IGBT的EMI机理与抑制方法分析案例。

一、引言

独学而无友,则孤陋而寡闻。EMC是一个综合性学科,其涉及的知识面纵、广、深,仅仅靠公司内部团队的封闭式的项目交流,团队能力很难达到更高的level,也会阻碍EMC工程师们成长。目前很多企业中EMC工程师都处于疲于奔命的项目交付上,很难静下心来与公司团队外的大牛们进行沟通交流,使得EMC工程师只具备应付项目的能力,而缺乏了第一性原理的分析。

二、概述

PWM控制型IGBT工作在斩波模式,使得IGBT本身自带干扰源属性,自扰与互扰系统中的其他设备。随着近几年功率半导体器件的发展,像SIC、GAN等半导体器件的出现,提升开关速率降低了损耗,但却带来了EMI的巨大挑战。以三相AC380V输入驱动器的轻载低频运行为例,其整流母线电压为DC513V左右,Vce的turn on/off时间达到了ns级,产生dv/dt约为几KV/us ~几十KV/us,dv/dt在回路中产生的共模噪声电流为几十A甚至100A以上,严重干扰周围设备,仅从路径上去抑制,需要付出巨大的滤波成本,所以IGBT的EMI抑制一直是业界的关注点。

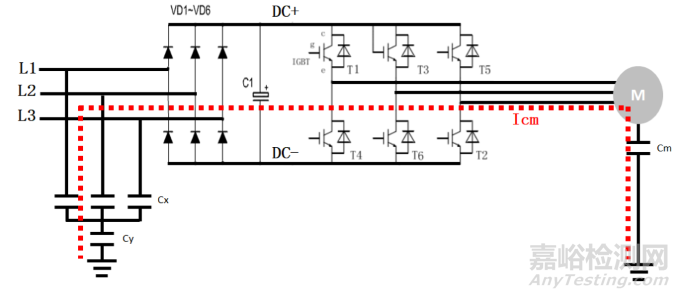

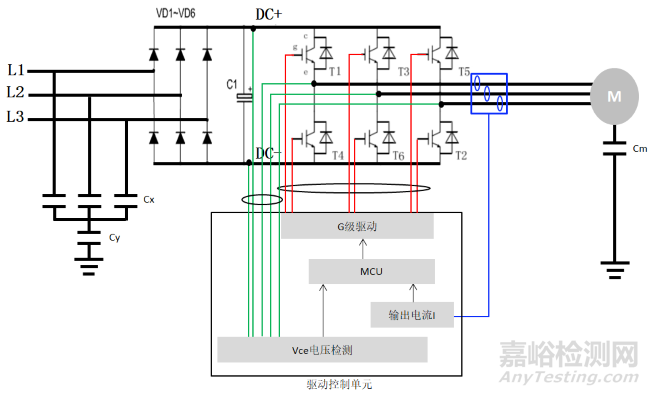

1. 驱动器共模噪声的回路示意图

参见图1

图1 干扰路径示意图

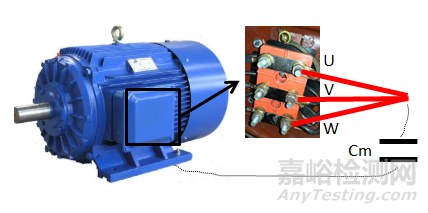

图2 Cm测量示意图

滤波电容:X电容Cx和Y电容Cy;

分布电容:以电机绕组与机壳地分布电容Cm为主,其他分布电容未画出。

共模噪声电流:Icm。

2. 驱动器噪声电流及场强估算

示例:Cx=1uf,Cy=0.1uf,Cm=10nf,Vdc=500V,Tr=50ns,电机线长度1m。

1) Icm估算

Icm = C回路*dV/dt

= 100A;

注:上式中C回路 ≈ Cm。

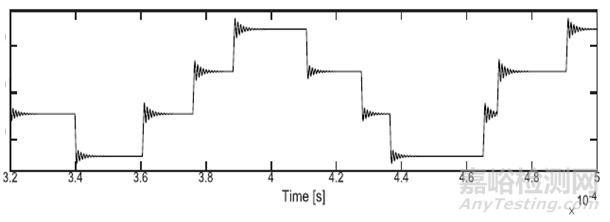

图3 Icm电流波形示意图

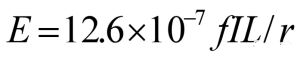

2) 3m远处共模辐射场强估算

≈90dB(uv/m)

其中 :

E:电场强度(V/m)

f :电流的频率(MHz)

L:电缆的长度(m)

I :电流的强度(mA)

r :测试点到电流环路的距离(m)

由估算结果可知,共模电流峰值达到了百安级,3m远处电场强度达到了90dB,在产品认证及实际应用中需要付出更多的抑制代价。

三、原理分析

1. 驱动器共模噪声机理分析[1-3]

(a) 共模电压等效简化电路

(b) Vcm共模电压波形示意图

图4 共模噪声机理分析

三相PWM脉冲之和不为0而形成的四电平阶梯波是产生驱动器共模干扰的本质原因。共模电压:图片 。

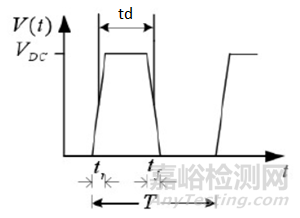

2. IGBT的Vce频谱特性

驱动器IGBT的Vce波形与频谱特性参见图5。

(a)Vce梯形波 (b)梯形波频谱

图5Vce梯形波频谱示意图

改变Vce的高频部分的频谱特性有二种方法:

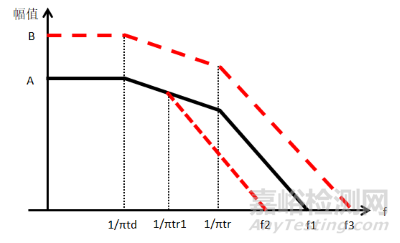

1) 改变幅值(图5:B→A,使得f3→f1偏移),示例图6[3];

图6 幅值对频谱的影响

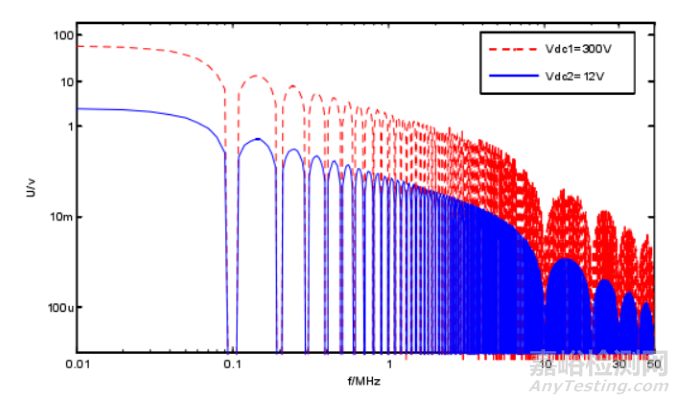

2) 改变turn on/off时间(图5:1/πtr→1/πtr1,使得 f1→f2偏移),示例图7[3];

图7 tr时间对频谱的影响

在实际应用中很难去改变幅值,所以把改变Vce频率特性的重任交给了turn on/off时间(也就是改变Vce的dv/dt)。

3. Vce的dv/dt研究现状

dv/dt设计离不开驱动电路,近些年围绕着驱动电路的研究进行简述说明:

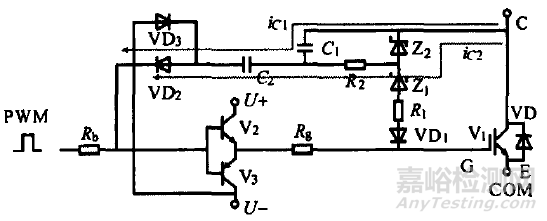

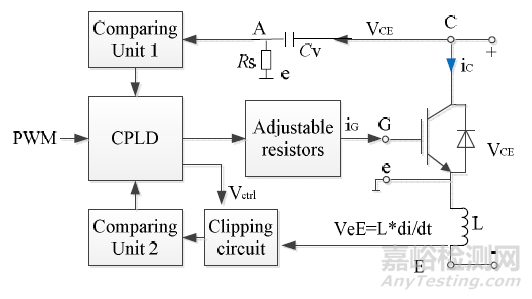

1) 有源门极控制型驱动电路,参见图8[4]。

图8 有源驱动电路示意图

有源驱动型在实际应用中turn on/off时间过长,改善了EMI的同时增大了损耗;

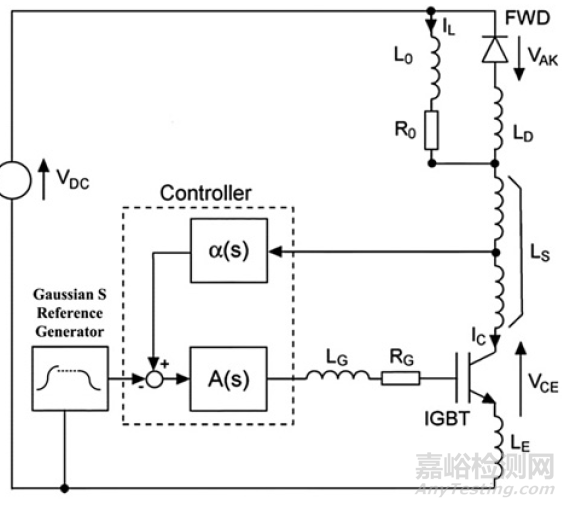

2) 高斯波控制型驱动电路,参见图9[5]。

图9 Gaussian S-shaping驱动电路示意图

高斯波控制使得Vce的turn on/off边沿高斯化,改善了EMI并权衡了损耗,但使得Vce波形阶梯式变化且控制较复杂。

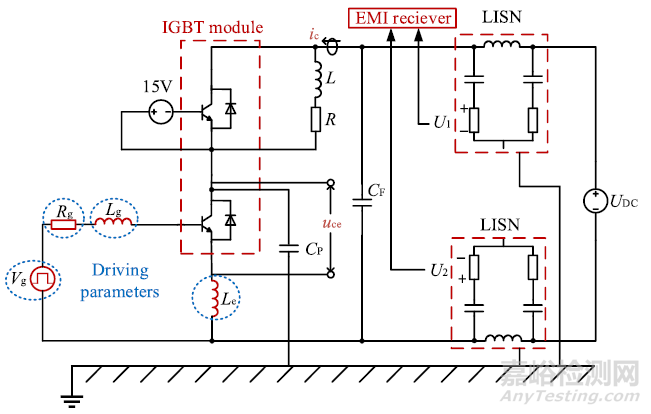

3) 驱动电路中各参数对dv/dt及EMI的影响,参见图10[6]。

图10 电阻电感驱动电路示意图

仅分析驱动电路电感和电阻参数对dv/dt的影响,没有从dv/dt动态调整角度进行说明;

4) 可调驱动电阻型驱动电路,参见图11[7],。

图11 可调驱动电阻的驱动电路示意图

可调驱动电阻电路通过采集管电压和管电流波形来实时调节驱动电阻,可获得较好的动态调节,但电流变化采集用电感的加入,会引入谐振风险;

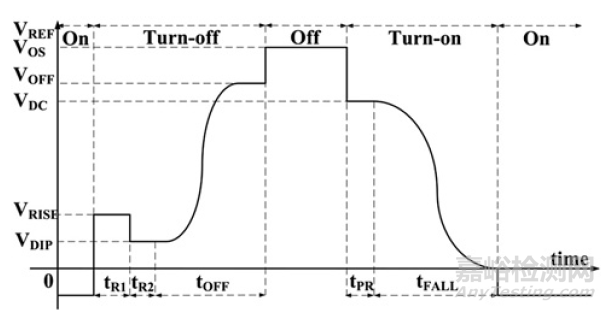

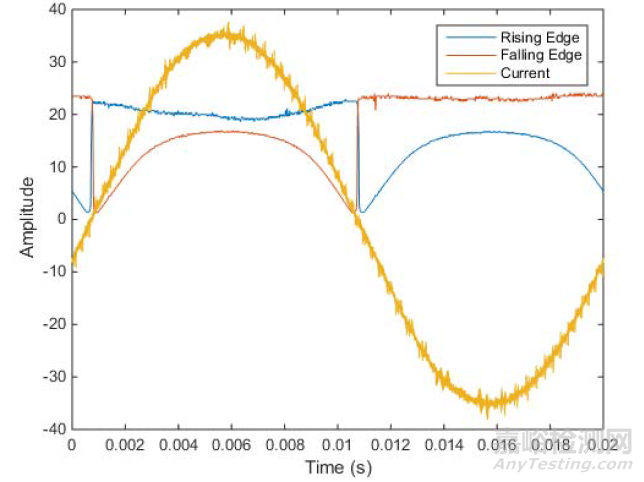

5) dv/dt驱动周期变化规律, 参见图12[1]。

图12 输出电流一个周期内的dv/dt变化

对dv/dt与输出电流的周期性变化进行了测试说明,但没有进行动态调节方法的说明。

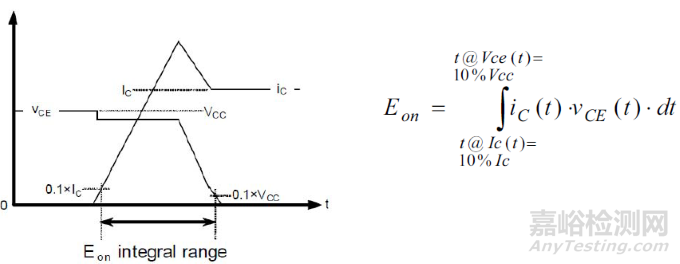

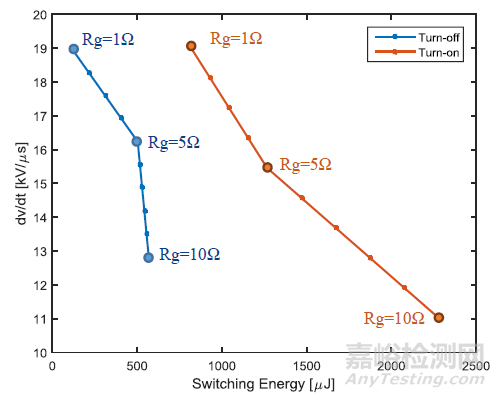

4. dv/dt与损耗的分析

IGBT模块的turn on与turn off计算方法相同,图13给出了开关瞬态电压、电流波形及turn on过程的损耗计算公式[8]。

图13 开关损耗示意图

为直观说明损耗与dv/dt关系,参见图14[1]。

图14 损耗与dv/dt关系

在实际产品设计中要权衡dv/dt与损耗的关系,驱动参数越大,turn on/off时间越长,带来损耗越大需要更大的散热成本。

四、dv/dt与EMI和开关损耗优化设计的新方法探讨

通过文献[1]和文献[7]对dv/dt与EMI研究的基础上,针对Vce边沿交错控制与dv/dt在线调整方法的分析说明,详细如下。

1. 运行过程中的dv/dt特性分析

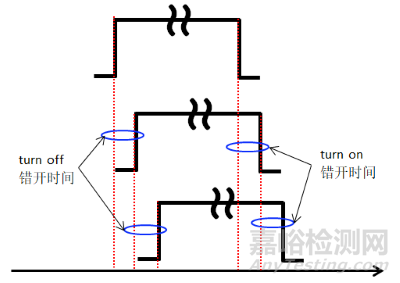

1)波形边沿叠加特性

驱动器类IGBT控制方式有无PG V/f 控制、带PG V/f控制、无PG矢量控制、带PG矢量控制等等不同的控制方式和术语描述,总结来说为三大类:VF、开环矢量、闭环矢量控制。不同的控制方式发波方式会有所差别。同时抓取上桥T1、T3、T5的Vce波形,来综合说明驱动器运行过程中的Vce的发波模式,参见图15。

图15 发波模式示意图

模式1:刚启动或0HZ运行时,三个管子的边沿(上升沿或下降沿)重叠在一起。

模式2:随着运行频率的增加,三个管子波形逐渐错开,两个管子的边沿(上升沿或下降沿)重叠在一起。

模式3:速度稳定时,三个管子边沿交错开,无叠加出现;

VF模式控制:模式1和模式2;

其他模式控制:模式2和模式3。

◆干扰影响分析

干扰电流峰值:把单管噪声电流记为Icm=C回路*dV/dt,所以,模式1峰值干扰电流相当为3*Icm、模式2峰值干扰电流为2*Icm、模式3峰值干扰电流相当为1*Icm。

◆干扰强度比较

因工作在模式1和模式2,所以VF控制下的噪声量级比其他控制方式下的更强,特别是0HZ或低频运行时。

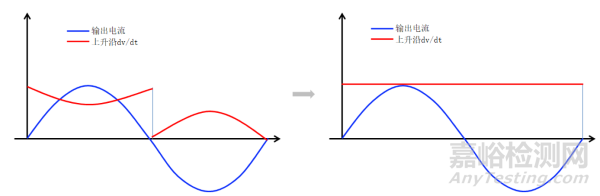

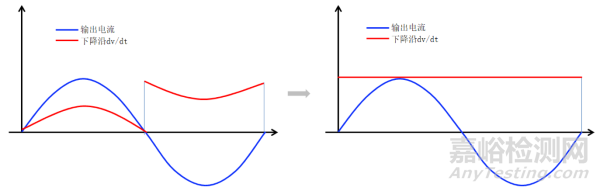

2)同一驱动参数下dv/dt随输出电流变化的特性

参见图12所示,turn on (下降沿)与turn off(上升沿)的dv/dt的特性总结如下:

◆上升沿与下降沿在电流过零点处的dv/dt最大;

◆上升沿的dv/dt在电流正半周比在负半周大;

◆上升沿的dv/dt在电流正半周内随电流的增大逐渐变小,电流最大时dv/dt最小;

◆下降沿的dv/dt在电流负半周比在正半周大;

◆下降沿的dv/dt在电流负半周内随电流绝对值变大逐渐变小,电流绝对值最大时dv/dt最小;

◆上升沿的dv/dt在电流负半周期内随电流绝对值变大而变大;

◆下降沿的dv/dt在电流正半周期内随电流变大而变大。

2. IGBT Vce噪声源抑制方法

经过以上分析,有以下四种抑制方法:

1)0HZ或低频不发波,或启动频率提高(如1HZ以上才发波)----各厂家已应用;

2)降低五段发波与七段发波的运行切换点,降低有效发波次数----各厂家已应用;

3)Vce边沿交错控制最小化dv/dt,使得干扰电流峰值最低,同时对损耗没有影响;

4) Vce边沿变缓设计

a) 固定参数设计----应用较多,一般负载越重开关损耗越大,与EMI互为矛盾点,需要权衡;

b) dv/dt在线调整控制,最优化EMI与损耗的折中设计。

3. Vce边沿交错控制

边沿交错控制的本质是增大各个管子开通关断的时间间隔,使得各个电压波形边沿不重叠,降低dv/dt,从而减小干扰。

1) 设计点:改变死区时间来完成边沿交错的控制,但要注意时间不宜过大,一般错开共模电流第一个波峰宽度就可以了,参见图3和图16所示。

图16边沿交错控制示意图

2) 负面影响:因死区时间的调节控制,可能带来驱动器输出电流的非正玄化,需要额外的手段进行正玄化的处理。

3) 应用场合:特定场合。

4. dv/dt在线调整控制

因电机负载的电感特性,使得IGBT开关动作时,电流不会立即降为零,需要等到CE两级的载流子逐渐消失后,才能彻底的关断,电感中的电流变化影响着IGBT的turn on与turn off时间。线调整控制的本质是找到dv/dt与输出电流的周期性变化规律,从而设计出适合的驱动参数,使得EMI与损耗最优化。实际测试中也发现dv/dt与驱动参数及输出电流大小等因素相关。

◆驱动器不接电机,dv/dt测量很稳定,在不同运行频率下测得的结果都一样;

◆驱动器接电机(空载与加载),dv/dt随电流的变化而变化。在相同的IGBT的g极驱动参数下,电流越大dv/dt越小。

1) 设计点:由变化过程中过零点为dv/dt最大点,保证过零点dv/dt满足EMI要求,再根据输出不同电流动态调整dv/dt,使得趋近于过零点的dv/dt。其驱动控制电路示意图参见图17,dv/dt的驱动参数设计方向参见图18。

图17驱动控制电路示意图

(a)上升沿dv/dt设计

(b)下降沿dv/dt设计

图18 dv/dt设计方向

dv/dt在线调整控制的优点:

◆dv/dt在整个周期内为满足EMI需求的最大值,大大减小了开关损耗,最优化EMI与损耗的设计;

◆不需要在IGBT的E级上串如电感,而引发的谐振风险;

G级驱动部分,有以下两种实现方法:

◆采用不同的驱动参数组合;

◆采用栅极电流控制芯片。

2) 负面影响:增加控制电路与电流检测电路,成本增加,控制稍复杂。

3) 应用场合:通用。

5. 应用案例调查

1) 边沿交错控制技术目前了解到还没有企业来做,未来特性场合下可能会有应用;

2) 不同驱动参数组合的动态调整,已经有实际应用(例:某公司的深海探测器的高压电源产品,解决系统自扰问题)。

3) 栅极电流控制芯片,在行业有应用,功率半导体驱动芯片厂家也已经有标准品或根据客户需求进行定制。如下图19为某厂家的官网信息展示。

图19栅极电流控制芯片

6. 总结

针对PWM控制型IGBT的dv/dt优化,提出了 Vce边沿交错控制方法和dv/dt在线调整控制两种设计方向,工程师可根据设计需求进行细节方案优化与方案落地。

五、思考与启示

1.三相PWM脉冲之和不为0是产生驱动器共模干扰的本质原因;

2.IGBT 的高频EMI抑制即为dv/dt抑制;

3.了解驱动器发波过程,避免边沿叠加产生更大的dv/dt;

4.权衡dv/dt与开关损耗,设计方案落地不能只考虑单一因素;

5.大道至简,从第一性原理分析;

6.善于总结,从实践中总结规律,返璞归真;

7.站在前辈的肩膀上来看问题,了解和洞察行业应用(落后就要挨打)。

六、参考资料

[1]. Victor Dos Santos, Trade-off between losses and EMI issues in three-phase SiC inverters for aircraft applications[C]. IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity (EMCSI).2017.

[2]. 郭彦杰, 电动汽车用 IGBT 及逆变器的电磁兼容性分析[J]. 高电压技术.2014(40): 1732-1737.

[3]. 龙海清, 电动汽车PWM驱动电机系统EMC研究[D]. 重庆大学 .2014.

[4]. 郑琦琦,基于IGBT有源门极控制的EMI抑制方法研究[J].电力电子技术.2016,(12):8-10+37.

[5]. Xin Yang, Investigation of the trade-off between switching losses and EMI generation in Gaussian S-shaping for high-power IGBT switching transients by active voltage control[J]. IET Power Electronics.2016,(9): 1979–1984.

[6]. Huazhen Huang, The Influence of Driving Parameters on Conducted EMI for an IGBT Module[J]. IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY.2020, (2)1 – 9.

[7].Yang Wen, A di/dt and dv/dt feedback-based digital gate driver for smart switching of igbt modules[C]. Asia-Pacific Conference on Antennas and Propagation (APCAP).2017.

[8]. Marco Honsberg, A 6-in-1 IGBT module performance evaluation platform determining the trade-off between dV_dt and turn-on loss of different IGBT _ FwDi chip setups[C]. European Conference on Power Electronics and Applications.2011.

来源:电磁兼容EMC

关键词: EMC整改