嘉峪检测网 2025-05-14 14:42

导读:在这里介绍一种主动型 EMI抑制技术---展频技术,它应用半导体芯片技术进行处理,被称为当今最先进有效的主动型 EMI 抑制方法之一。

前言

随着电子产品的运行速度和复杂程度的不断增加,数字信号的时钟频率越来越高,电路系统对于信号的建立、保持时间、时钟抖动等要素提出越来越高的要求。电磁干扰(EMI)也在不断增长,各种便携式无线产品的数量增加使得各系统之相的相互干扰亦随之提高,电磁干扰的问题也越来越严重。它会引起电路性能的降低,严重的话,可能导致整个系统失效。在实际操作中,相关机构颁布电磁兼容(EMC)的规范,确保上市的电子产品满足规范要求。

传统 EMI 防护技术

一般控制电磁干扰(EMI)发射比较常用的方法就是屏蔽,我们通俗的称为围堵。屏蔽是一种比较容易的降低干扰的防护技术,它将EMI 围堵在系统中,利用接地的屏蔽导体把辐射位置全部或部分围堵屏蔽,是对空间、成本、重量等因素较无限制的系统来是很有效的解决方案。但是对于大部分的系统,特别是便携式与掌上产品,屏蔽会增加产品的体积、重量和成本,增加制造流程自动化的困难度同而变相的增加劳动力成本。

另外用电阻(R)、电容(C)、电感(L)、磁珠(B)等元件所组成的滤波器来抑制EMI ,我们称之为被动型EMI 抑制技术。时钟信号常常是电路系统中频率最高和边沿最陡的信号,多数EMI问题的产生都和时钟信号有密切关系,这种低通滤波器用于降低由时钟信号所产生的 EMI 干扰被广泛使用,它主要是滤除级数较高的高频谐波以降低时钟信号的上升和下降时间。但这种技术在高速系统中不太适用,因为这种技术会降低关键的中止和激活时间,亦会增加信号的过高激、过低激以及振铃程度。过滤技术的难点是无法系统化,即在某个节点上的EMI 辐射的降低,并不能降低其它节点的辐射。

除此之外在PCB中增加POWER电源层和GND地层等 , 或通过PCB LAYOUT技巧降低EMI显然比较费时和增加大量的成本。随着电子系统的速度往高速、高复杂度和便携式发展,以上这些措施也就越来越难加以应用。

在这里介绍一种主动型 EMI抑制技术---展频技术,它应用半导体芯片技术进行处理,被称为当今最先进有效的主动型 EMI 抑制方法之一。

展频技术优势

展频时钟发生器SSCG(Spread Spectrum Clock Generator)是一种非常有效且低成本的解决EMI问题的方案,可以在保证时钟信号完整性的基础上应对更广频率范围内EMI问题。相比传统上使用铁氧体磁珠和射频扼流线圈抑制EMI,SSCG通过时钟内部集成电路调制频率的手段来达到抑制EMI峰值的目的。SSCG不仅调制时钟源,其它的同步于时钟源的数据、地址和控制信号,在时钟展频的同时也一并得以调制,整体的EMI峰值都会因此减小,所以说时钟展频是系统级的EMI解决方案, 这是SSCG相比其它抑制EMI措施的最大优势。另外SSCG功能可以由用户选择不同配置,可以打开或者关闭,以及设置不同的调制频率范围等,应用起来非常灵活。

展频技术原理

联系信号的时域与频域的数学方法叫傅里叶变换,由法国数学家傅里叶发现,任何周期函数都可以用正弦函数和余弦函数所构成的无穷级数来表示。用傅里叶级数表示一个信号时,这些正弦波函数和余弦波函数就代表了这个信号包含的频率成分。

如果一个周期性函数的周期是T,则它可以写成:

式中a0 叫直流分量,它实际是函数在一个周期内的平均值。

n = 1 的分量叫基波分量,它的频率与原来的函数的重复频率相同。n 为其他数的项叫谐波分量,例如 n = 2 的项叫做二次谐波,n = 3 的项叫做三次谐波。各项求解系数如下:

我们取谐波次数越高,傅里叶级数逼近原来函数的程度越好。

傅里叶级数中并不是所有项都存在的。这个函数中,除了a0 以外,an 项都不存在这是因为方波波形是个奇函数,而余弦函数是一个偶函数,因此不存在。我们还可以看出,正弦波的各项仅有的奇次数项。这是因为方波的占空比为1的缘故。它意味着如果我们的时钟信号采用占空比为1的脉冲信号,可以减少谐波的成分,同时也减少了导致干扰的机会。当谐波的成分足够多时,合成的波形就能够与原来的波形很接近。如果我们能根据需要,只采用适当的次数的谐波来合成原来的波形,就能够大大减少高次谐波的成分。而这些高次谐波成分往往是导致电磁干扰的主要原因。

需要注意的是,时域中周期性的信号对应频域中离散的频谱,时域中非周期性的信号对应着频域中连续的频谱。这意味着周期性的信号在频域中的能量更加集中,而非周期性的信号,在频域中的能量是分散在各个频率上的,因此在某个频率上的能量较小。这个概念具体到工程上面的应用,就是进行设备的电磁兼容设计时,要特别关注那些周期性的信号,如时钟信号,本振信号等,因为这些信号会产生最强的电磁干扰发射。所以,我们利用这种特性使时钟信号发生抖动,从而使频谱扩展散开,这样就能够减小频线的幅度,从而更容易的通过电磁兼容设计技术。

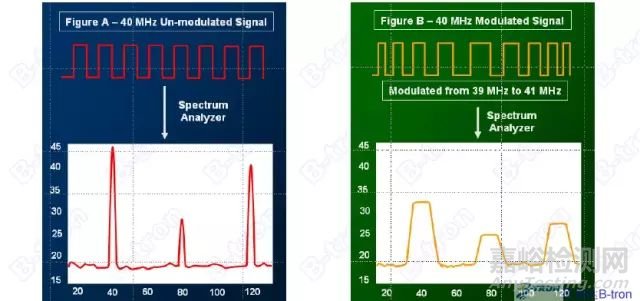

如下图以一个简单的40MHz 的频率为例:

展频技术不但对时钟振荡频率即基波有抑制作用,如下图所示 :

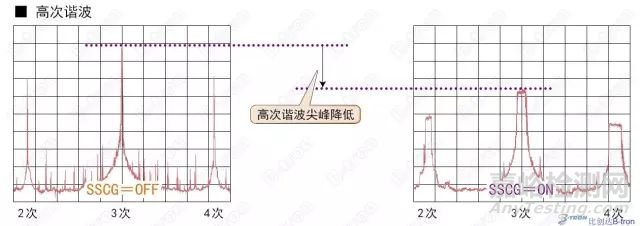

而且对时钟的高次谐波的峰值也有很强的抑制作用,如下图所示 :

展频技术应用案例

某行车记录仪测试 RE 时发现由时钟产生的倍频干扰很强。

增加展频方案于晶振的源头后干扰点得到了很好的抑制。

展频方案使用方法

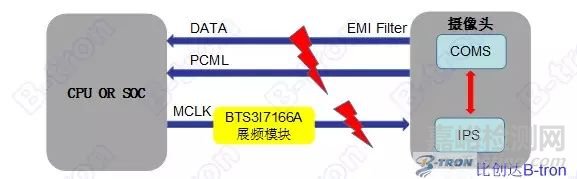

展频方案可以应用于汽车电子、GPS电子产品、笔记本、MID、机顶盒、手机、工业控制产品等等的产品当中,具体所应用的位置如下 :

方案1 :展频方案应用于晶振的源头来抑制由时钟倍频所产生的干扰

方案2:展频方案应用于单线时钟信号来抑制由时钟倍频所产生的干扰

BTS3I7166A 展频模块使用方法

BTS3I7166A 展频模块原理图

BTS3I7166A 展频模块 BOM 参数

BTS3I7166A 展频模块 DEMO BOARD

BTS3I7166A展频模块使用说明

1. 模块 VDD电源供电电压为 3.3V/2.5V,推荐使用 3.3V电源供电。

2. 芯片对时钟信号支持的频率范围是 10-80 MHz。

3. 在用于晶振时钟源的情况下,将机器本身的晶体及匹配的元件拆下贴在Y1、C5、C6、R6 位号处,模块中的 OUT 焊点接到主芯片的 XIN 脚即可,主芯片的 XOUT 悬空。

4. 在用于单线时钟信号的情况下,请将时钟信号输入焊接到上图所示位置,OUT焊点输出到需展谱的时钟信号脚。

5. R4 默认值为 47K ,客户可以根据机器测试的情况在 30K-200K 之间调整参数。

6. 关于芯片的封装和其他未尽说明可参考我司提供的 BTS3I7166A IC 规格书。

7. PCB Layout时展频IC电路尽可能紧靠主芯片,并且晶体尽量靠近 BTS3I7166A 展频IC, 晶体的走线尽可能短和BTS3I7166A 展频IC的输出线尽可能短。

总结

展频方案对于抑制 EMI 效果显著,它能减少旁路电容、扼流圈、磁珠以及屏蔽罩等其他抑制干扰组件的使用,有助于实现产品的小型化。如果在产品设计阶段就采用展频方案,更可节省测评时间和研究EMI 对策的费用。这种主动型的EMI 防护方案将会在今后得到更广泛的应用,谢谢。

来源:Internet