嘉峪检测网 2025-05-19 09:12

导读:本文介绍了DRAM的基本构造、控制电路的堆叠创新及3D DRAM的行业意义。

DRAM(Dynamic Random Access Memory)如同中转站,在CPU或GPU进行数据运算时,承担起临时存储数据的重任,其性能取决于处理器访问速度及数据单元排列紧密度。

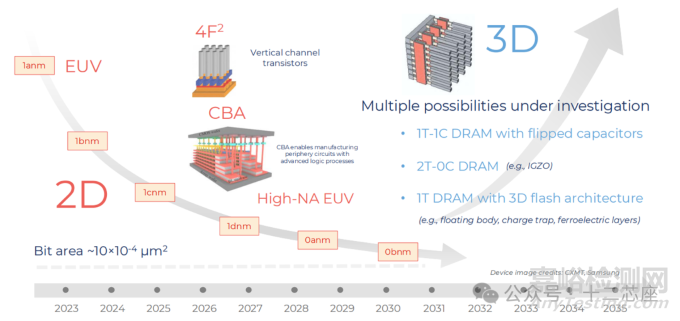

而目前3D DRAM 无疑是提高cell density 的新手段,对于3D DRAM这一概念,也有两种截然不同的做法,其中一种就是如今最为火热的HBM,不过,HBM是堆叠芯片(stacked-die)存储器,并非是像3D NAND那样的单片3D芯片,其介于2D和3D之间,也有人将它划分进了2.5D的范畴。

至于真正的单片3D芯片,为了提高存储密度,需要减少单层DRAM芯片的单元面积,但垂直电容器导致层非常厚,堆叠困难,部分方案尝试将电容器水平放置,也有的方案彻底取消电容器。

Fig1. 下一代动态随机存取存储器 - 技术路线图

DRAM的基本构造

存储数据的基本单位——存储单元(Cell)至关重要。单元面积越小,有限空间内集成的单元就越多,电信号传输距离也越短,低功耗效率和处理速度得以提升。每个单元由MOS晶体管和电容器组成,前者控制电流方向与电压,后者负责短暂充放电存储数据。

Fig2. DRAM的基本构造

为存储海量数据,DRAM将无数单元以棋盘格形式排列成阵列(Array),借助解码器(Decoder)指引,处理器可快速定位目标单元,位线(Bit Line, BL)连接源极并施加电压,字线(Word Line, WL)连接栅极控制电压,电容器与漏极垂直相连。

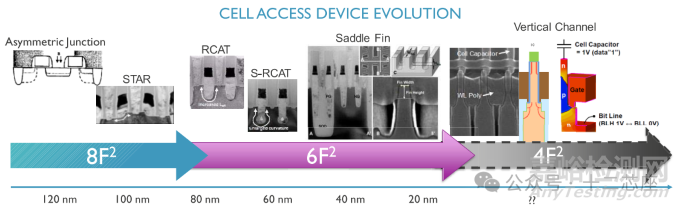

Fig3. Various cell access device options are shown.

Fig3. Various cell access device options are shown.

1.2D DRAM的演进

早期DRAM采用8F² RCAT结构,位线跨4格,字线跨2格,总面积8F²(F为最小特征尺寸),但源极无法直接与字线连接,需留白,单元实际占4格位线宽度。虽结构简单,位线与字线留白却限制存储密度提升。单元结构已从 8F2 单元演变为 6F2 单元,因为按照下图所示的设计规则,单元尺寸可降低多达 75%。这一变化带来了诸多难题,例如开路位线噪声以及因单元尺寸变小而带来的挑战。然而,这些问题通过引入低电阻材料、缩小存储节点电容器的介电层以及隔离技术得以解决。

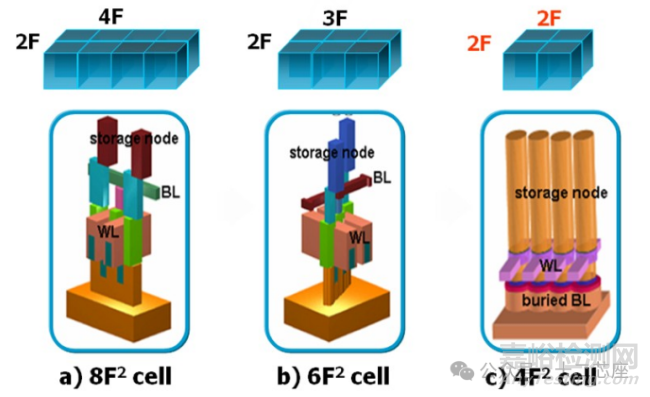

Fig4. from 8F2 to 4F2 cell.

自130纳米及以下制程起,6F² BCAT结构登场,单元布局优化为位线3格、字线2格,大幅提升单元密度。然而,随线路宽度缩小到10纳米级,物理极限致电流泄漏、信号干扰频发,平面棋盘格排列单元难以为继。

2.3D DRAM的崛起

为高效利用有限面积,竖起水平排列单元或垂直堆叠单元阵列成必然选择。4F²结构将源极、栅极、漏极转为垂直结构,下层源极接位线,其上栅极连字线,再往上堆叠漏极与电容器,减少电气干扰,面积缩约三分之一,如三星的垂直通道晶体管(VCT)DRAM和SK海力士的垂直栅极(VG)DRAM。

而3D DRAM则更进一步,让位线或字线之一竖直排列,晶体管和电容器横向堆叠,层层叠加,类似3D NAND,虽各家厂商在结构和堆叠技术上各有不同。

3.8F²、6F²、4F² 主要区别

8F² DRAM:

8F² DRAM 是传统的主流 DRAM 架构,采用折叠位线架构。其单元设计对称,位线对紧挨着,有助于实现可靠的检测与恢复操作。这种架构在可制造性和 DRAM 阵列操作方面表现出色,能够有效减少阵列噪声的影响,确保数据读取的准确性。然而,由于其单元面积较大,限制了存储密度的进一步提升,难以满足不断增长的存储需求。

6F² DRAM:

6F² DRAM 是一种改进的架构,单元面积比8F²减少了约25%。它采用开放位线架构,位线对由两根分列在位线检测放大器两侧的位线组成。这种设计可以在相同的芯片面积上集成更多的存储单元,提高了存储密度。然而,开放位线架构对阵列噪声更敏感,可能会影响数据读取的可靠性。此外,更小的单元尺寸也带来了更高的制造工艺要求。

4F² DRAM:

4F² DRAM 是一种新型的架构,通过将晶体管和电容器垂直堆叠,进一步减小了单元面积。这种架构不仅能够显著减少电气干扰,还能在有限的芯片面积上实现更高的存储密度。此外,垂直架构还能完全抑制row hammer干扰,提高存储器的稳定性和可靠性。目前,4F² DRAM 还处于研发阶段,但其在高密度存储和低功耗应用方面具有巨大的潜力。

Fig5. (a) 8F2, (b) 6F2, and (c) 4F2 design architecture.

控制电路的堆叠创新

在4F2和3D DRAM中,控制电路(周边电路)的垂直堆至关重要若能像堆积木般叠加这些电路,芯片面积将进一步缩小。但需分开制作绘制有DRAM单元阵列和控制电路的晶圆,再进行晶圆对晶圆(W2W)键合或混合键合(Hybrid Bonding°)

3D DRAM的行业意义

目前AI芯片市场常用的高带宽存储器(HBM)存在物理限制,随着芯片不断堆叠,发热和功率效率问题日益突出。行业正考虑基于3D DRAM重新设计下一代存储器结构,3D DRAM的突破和发展无疑将为存储器技术乃至整个半导体行业带来新的活力与变革。

来源:十二芯座

关键词: DRAM