嘉峪检测网 2025-07-17 22:23

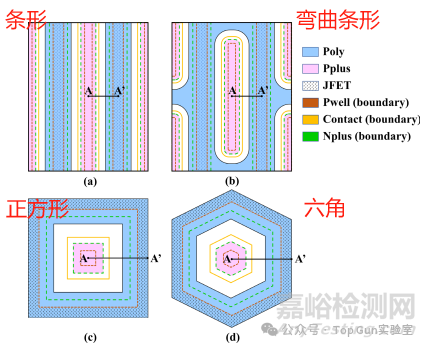

导读:对四种SiC MOSFET的元胞布局(条形、弯曲条形、正方形和六角形)的单脉冲雪崩能量进行测试,进一步对其进行仿真,分析其雪崩能量主要集中于器件哪一个位置,并在此基础上分析比较四种结构的雪崩能量的分布差异。

对四种SiC MOSFET的元胞布局(条形、弯曲条形、正方形和六角形)的单脉冲雪崩能量进行测试,进一步对其进行仿真,分析其雪崩能量主要集中于器件哪一个位置,并在此基础上分析比较四种结构的雪崩能量的分布差异。

元胞布局与UIS测试介绍

器件的雪崩能力是衡量SiC MOSFET可靠性的一个重要指标。通常采用非箝位电感开关(Unclamped Inductive Switch,UIS)测试器件的雪崩能力。

在过往的研究中表明,当UIS测试中Source pad的温度超过熔点即会发生UIS失效,而SiC MOSFET的雪崩可靠性与其内部元胞结构和参数有关。而且过往的研究还对非对称沟槽和双沟槽的SiC MOSFET的UIS特性,非对称沟槽结构的失效是因为金属层的热失效,而双沟槽的失效则是因为栅氧的高电场强度。除此之外,本文对不同元胞布局对UIS特性的影响。

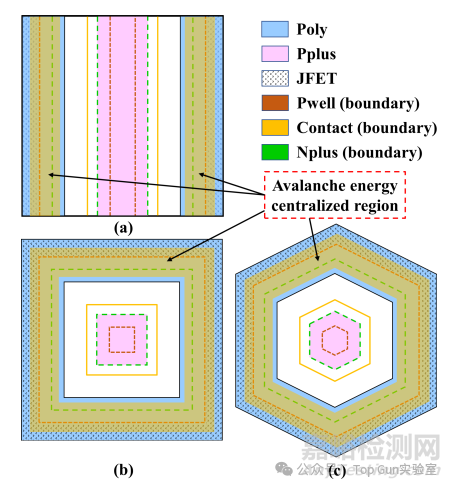

目前商用市场上主要的SiC MOSFET的元胞形状主要是条形、正方形、六角,其中条形又分为普通条形和弯曲条形。普通条形的Poly栅极并不像正方形和六角在有源区内部就相连,而是在芯片边缘相连,继而通过bus连接到 Gate Pad。这会导致栅电流传输不均匀,且芯片中间位置的元胞沟道延迟开启,影响器件开关特性。而弯曲条形通过相邻栅极之间的交替连接改善了栅极电流的均匀传输优化了开关特性。

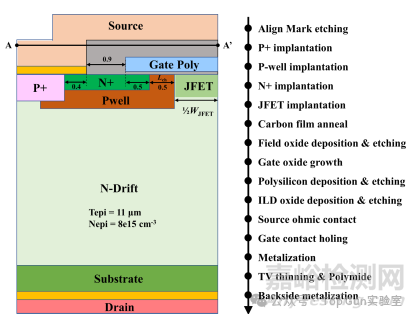

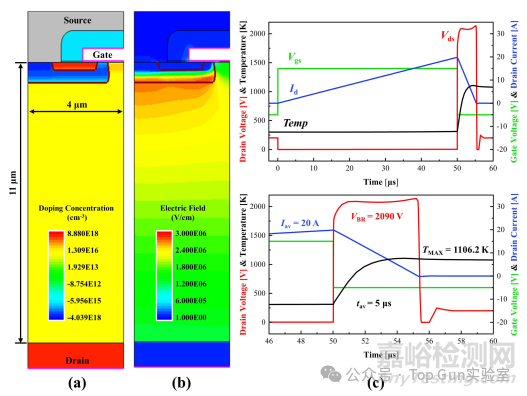

下图展示了上午A-A'元胞截面结构图和SiC MOSFET自对准制造工艺流程:选用了外延层厚度11um,浓度为8e15/cm3的外延片衬底。首先通过离子注入形成Pwell和Pplus,采用自对准工艺在多晶硅上生长0.5um厚的Spacer,然后进行Nplus源极离子注入,随后在有源区范围内进行JFET注入,随后沉积一层C膜保护,将之前离子注入在1700℃下退火30min激活。再生长50nm栅氧,并在其上沉积并蚀刻Poly栅,栅源之间形成0.9um的ILD。然后沉积Al层并蚀刻完成Source CT和Gate 的金属化,最后完成芯片背部的漏极金属化。)

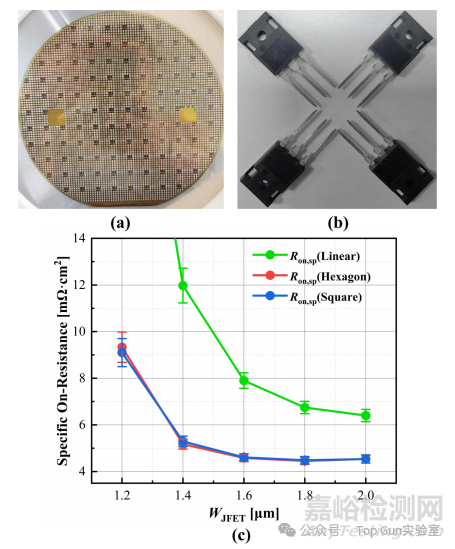

下图是成品晶圆图片和单管封装厚的图片。而条形、六角和方形元胞的Ron,sp也如下展示,方形和六角元胞具有相似的Ron,sp,并且明显低于条形元胞。这主要是因为方形和六角元胞具有相同的沟道密度,都比条形元胞的沟道密度高。特别是当JFET宽度小于1.6um时,器件Ron,sp随JFET宽度增加而减小的趋势,这是因为JFET较小时,通过增加JFET宽度而带来的JFET电阻的减小比元胞间距的增加更占优。但是当JFET宽度大于1.6um时,方形和六角元胞的Ron,sp不再增加,因为因JFET增加而导致的元胞面积的增加逐渐超过了JFET电阻减小的影响了。

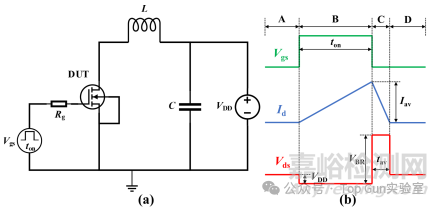

下图是UIS测试电路,被测器件DUT与电感串联,电容与高压源VDD并联。图b显示了UIS测试过程,分成了4个阶段:

阶段A,DUT不导通,VDS保持高压源VDD不变;

阶段B,栅极驱动电压VGS切换到高电平,DUT进入了导通状态,VDS下降的到0,漏电电流ID逐渐上升到所需的雪崩电流值IAV,IAV可以通过改变VGS的脉冲时间来调节;

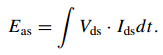

阶段C,VGS切换到负压,DUT关断,进入雪崩工作模式,VDS迅速上升到击穿电压VBR,因电感的存在,雪崩电流下降缓慢,并且储存在电感中的能量通过DUT缓慢释放。储存的能量在雪崩过程中通过热量的形式释放,这会在器件内部形成瞬时高温。阶段C中,DUT工作在高电压和大电流下,DUT单脉冲雪崩能量EAS由阶段C的雪崩电压和雪崩电流积分得到:

EAS较小时,IAV下降到0,DUT正常关断;但当EAS较大时,EAS产生的高温超过了DUT的耐受极限,IAV就会先下降再迅速上升,造成不可逆的雪崩失效。为了对比不同元胞形状的UIS,用EAS与有源区面积之比Eava作为比较值。

结果与讨论

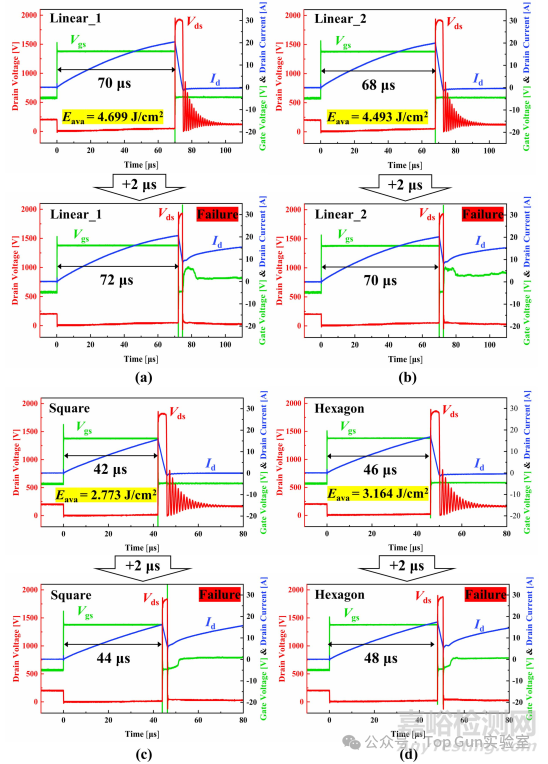

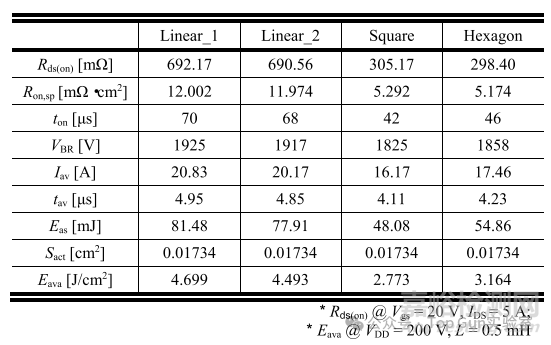

下图展示了其中元胞形状的器件在相同的测试条件下进行UIS测试。结果显示,条形和弯曲条形的Eava明显大于方形和六角元胞。而且,方形元胞和六角元胞的Ron,sp低于条形元胞器件的Ron,sp,尽管如此,条形元胞的雪崩可靠性仍是高于方形元胞和六角元胞的。

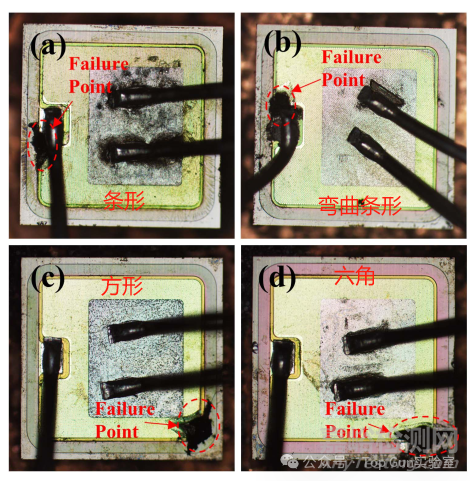

通过对四种元胞失效模块点测发现失效器件均呈三通状态。通过对失效模块塑封拆封发现,均可以观察到明显的烧毁点,这表明了器件失效是由热失效而不是栅氧击穿引起的。条形元胞器件的烧毁点靠近gate pad,而方形元胞和六角元胞的热失效点更靠近芯片角落。这里似乎彰显了雪崩烧点与元胞布局相关:方形元胞和六角元胞的元胞尺寸相较于条形元胞更小,所以方形元胞和六角元胞在相同有源区面积内,在芯片拐角处具有更高的元胞密度;雪崩能量在有源区内产生并传递,终端区域和gate pad不产生热量,器件进入雪崩状态后,芯片拐角处温度迅速上升,与芯片边缘存在较大温差,导致热烧毁。而条形元胞在gate pad区域因存在许多gate bus条,器件进入雪崩后,gate pad周围有源区温度迅速上升,与gate pad形成了较大温差,发生热烧毁。

为了进一步分析,利用TCAD对元胞进行仿真,其尺寸和掺杂分布尽量与真实器件保持一致。

器件仿真电路如前文所述,图b展示了器件雪崩模式1us后的电场分布,除了栅氧中心电场较高外,高电场主要集中的Pwell拐角。在雪崩过程种,器件的最高温度达到了1106K,超过了金属Al的熔点,导致了器件热烧毁失效。

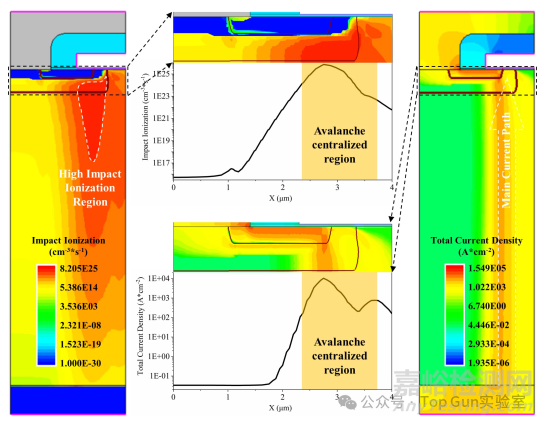

雪崩击穿强度一般在于碰撞电离和雪崩电流密度进行表征,器件在雪崩状态下的碰撞电离和雪崩电流密度如下图示。高碰撞电离和高雪崩电流密度都集中在了Pwell拐角附近。

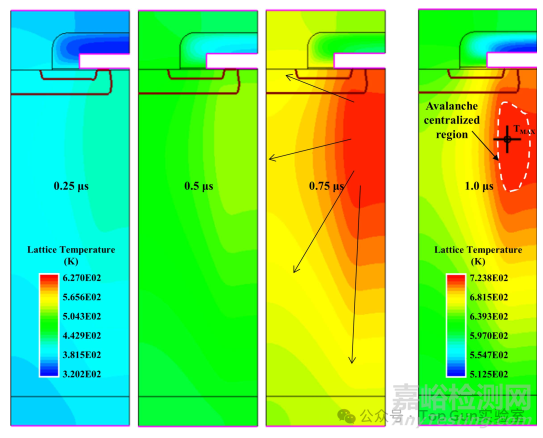

为了更清晰的展示雪崩状态下器件温度变化过程,下图展示了器件在雪崩1us后的温度分布。在雪崩状态下,器件首先在Pwell拐角处开始发热,虽然在JFET区域也存在雪崩电流,但是其碰撞电离和雪崩电流密度明显低于Pwell拐角处。

所以基于电场分布、碰撞电离分布、雪崩电流分布以及雪崩状态下温度分布,可以得到一个结论:SiC MOSFET在UIS测试下的雪崩能量主要集中在Pwell拐角处。

下图是元胞上具有Au的雪崩能量集中区域,条形、方形与六角元胞的雪崩集中区域所占面积比例为28.7%、44.2%和36.8%,其雪崩能量与元胞雪崩能量集中区域所占比例呈反比,雪崩能量集中区域比例越大,相应UIS能量密度越低。

总结

通过同样的工艺制作的四种元胞形状的SiC MOSFET,在相同的测试条件下进行UIS特性测试。结果表明,条形元胞的单脉冲雪崩能量密度是正方形元胞的1.69倍,六角元胞的1.49倍。

并且利用TCAD仿真确定了雪崩能量主要集中于Pwell拐角处,由此分析比较了条形、弯曲条形、正方形和六角元胞的雪崩能量分布差异,表明了雪崩能量密度与雪崩能量集中区域的比例呈反比,由此证明了条形元胞的UIS大于正方形和六角元胞。

来源:Internet