嘉峪检测网 2025-07-21 08:16

导读:本文主要简要介绍无源晶振匹配电容的计算公式。

Part 1

技术需求:计算无源晶振匹配电容的大小

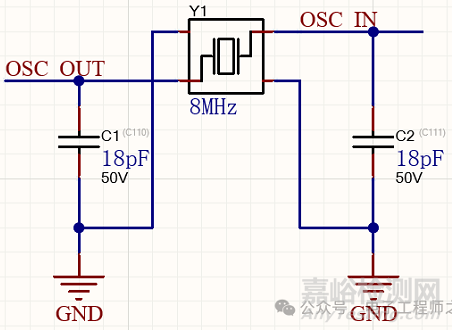

如下图所示,为一无源晶振的匹配电路,电容C1、C2为其匹配电容。那我们该如何计算该值呢?

且听我详细道来。

Part 2

一、匹配电容的计算公式:

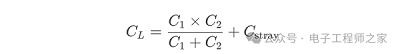

1. 基础公式

CL:晶振的负载电容(Load Capacitance),单位pF(规格书明确给出,常见12pF/18pF/20pF)。

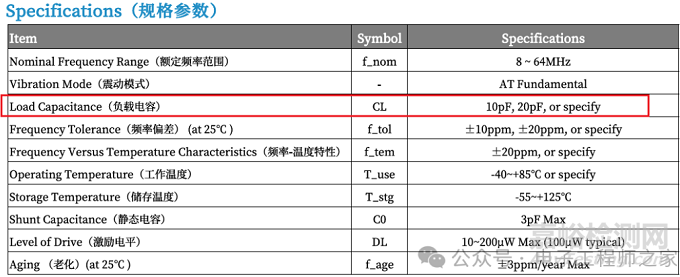

如下图所示为某无源晶振的规格书中有关负载电容的参数:

C1,C2:外部并联的两个匹配电容,单位pF。

Cstray:PCB寄生电容(包括走线、引脚等),通常 3pF~5pF(高频电路可达8pF)

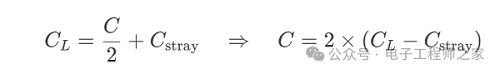

2. 电容对称设计(推荐)

若取 C1=C2=C,则公式简化为:

Part 3

二、计算步骤与示例:

案例需求

晶振负载电容 CL=12pF(规格书标注)

PCB寄生电容 Cstray=4pF(实测或经验值)

计算过程

1. 解算匹配电容值:

C=2×(12pF−4pF)=2×8pF=16pF

2. 选型:

选用 2个16pF电容(如NP0/C0G材质,精度±5%)

Part 4

三、关键设计规范:

1.电容选型要求

2. PCB布局要求

短走线原则:晶振到MCU的走线长度尽可能小,且对称布置,XTAL1/XTAL2长度差尽可能小,可采取类差分走线

铺地隔离:晶振下方铺铜(对寄生电容敏感的高速多层板可以隔层挖空),周围打地孔(间距≤λ/20,λ为晶振波长)

晶体晶振本体下方所有层原则上不准许走线,特别是关键信号线

优先表层布线,如需打孔,过孔附近必须要有回流地过孔

避开电源、数字信号线

Part 5

四、常见问题解决:

问题1:晶振不起振

原因:C1/C2过大导致增益不足 → 减小电容值(如20pF→15pF)

问题2:频率偏移

原因:Cstray估算错误 → 用可调电容校准(5pF~25pF范围)

问题3:发热失控

原因:电容ESR过高 → 换NP0材质电容(ESR<0.1Ω)

总结:匹配电容计算本质是CL=C/2+Cstray 的平衡过程,需结合实测迭代优化。

高频(>20MHz)场景建议使用π型匹配网络增强稳定性。

来源:电子工程师之家