一、产品失效案例分析

>> 1、失效现象:

经过电参数测试合格的产品2N**经过客户SMT(无铅工艺260±5℃)生产线贴装后,发现大量产品电参数失效,出现的现象是D、S间漏电,产品短路,失效比例超过50%。

>> 2、分析思路:

该产品芯片面积较大,且采用TO-252(D-PAK)表面贴装封装形式,产品组装时采用无铅工艺260±5℃,对产品的耐湿等级及气密性要求较高,封装时会碰到大芯片应力匹配等一系列问题。因此根据失效现象重点对产品离层进行调查研究。

>> 3、分析方法:

模拟SMT生产条件对同封装批次产品进行分析,采用超声扫描仪(C-SAM)对产品进行离层扫描。

>> 4、分析过程:

(略)

>> 5、分析结论:

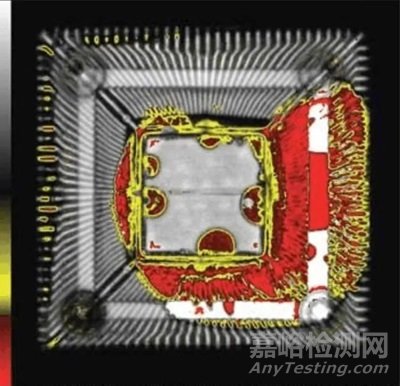

通过对经过SMT工艺试验的产品抽样进行超声扫描,发现产品载片区(PAD)与模塑料之间存在较为严重的离层现象,(详见图片1)

图1:红色区域为离层现象

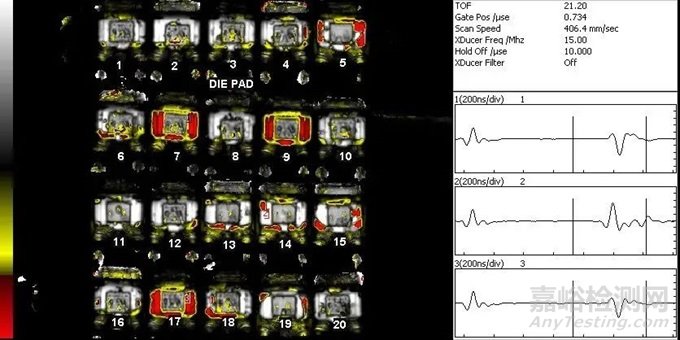

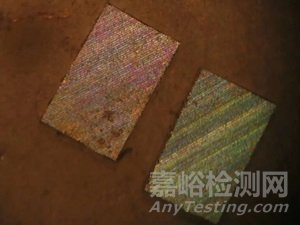

经过对失效产品进行解剖,发现失效芯片内部已对裂,详见图2、图3:

图2:红圈区域为裂纹

图3:芯片取下后呈断裂状

解剖结果与电参数失效项目完全吻合,表明产品经过表面贴装,在高温的影响下,芯片破裂导致电参数失效。这是一个非常典型的因封装未解决应力问题而引起芯片破裂最终导致产品失效的案例。

二、 芯片碎裂概述:

芯片碎裂是硅器件的一种失效模式,约占早期失效总数的1%,而对于薄芯片的MOSFET产品,芯片碎裂则占其失效的较大比例。虽然,通过改进封装设计、限制器件使用环境可以有效地防止芯片碎裂引起的器件失效,但即使在良好的设计、合格的制造工艺以及规范的使用环境下,依然存在着一定的芯片碎裂几率。随着器件可靠性级别和系统复杂程度的不断提高,十分有必要对芯片碎裂失效机理加以进一步的研究。

三、芯片碎裂的机理

芯片碎裂是由内外因素造成的,内因:芯片强度存在“脆弱”之处。外因:在外加条件(受热、通电热耗散)作用下,应力导致对芯片的剪切力。相对应力而言,芯片的强度差异影响非常微小,因此芯片碎裂主要是由应力造成的。

应力产生的原因随具体情况而不同:硅片前道工艺中的外延层淀积、扩散和离子注入、氧化、退火、淀积形成欧姆接触、金属内连、钝化层淀积:硅片后道工艺中的机械减薄(研磨、抛光)、化学减薄(湿法或者干法刻蚀)、背面金属层淀积;封装工艺中的划片、 装片、压焊、塑封等都将会产生或影响硅片/芯片的应力。其中,减薄、装片、压焊、塑封是产生芯片碎裂隐患的主要工序。更为严重的是,一般在工艺过程中观察不到碎裂现象,只有产品经过热固化或者器件热耗散时的瞬时加热,特别对表面贴装器件波峰焊接时的瞬间高温的作用下,由于芯片和封装材料热膨胀系数存在差异或者使用中受外界应力作用,芯片碎裂才会最终显现。例如:穿过结的裂纹可能导致短路或者漏电,(以上案例就是一个证明)。裂纹也可能全部或者部分截断电路。最为致命的是,裂纹引起的这些效应只有瞬间受热或者电流通过时才会显现,而标准的电性能测试则根本无法检测到这些失效。比较有效的检测手段是模拟器件使用环境,运用超声扫描仪(C-SAM)对产品进行离层扫描,如以上案例分析使用的方法,通过对离层的检测预防芯片的破裂发生。

四、离层的定义:

离层又叫分层,在电子封装中,是可靠性评价的一个主要方面。分层是塑封体内部各界面之间发生了微小的剥离或裂缝,一般在l~2 μm以上。主要发生的区域包括:封装树脂与芯片界面之间、封装树脂与(PAD)载片界面之间、封装树脂与引线框架界面之间、芯片与银浆(焊料)界面之间、银浆(焊料)与引线框架界面之间。(见下图)

五、离层的机理

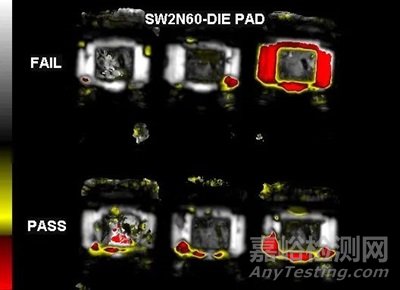

产生离层的工序是塑封工序,导致离层的因素主要为两个:一是芯片与封装树脂、芯片与装片焊料、引线框架材料与封装树脂等之间的热膨胀系数不匹配使产品瞬间受热时内部产生巨大应力,导致分层;二是封装树脂耐湿性差,产品吸湿。当封装体在环境温度剧变时,内部水分急剧汽化,当蒸汽压力大于封装树脂与芯片、载片以及框架表面之间的粘接力,以致于使它们的界面之间出现剥离现象,严重时还会导致封装树脂或芯片出现裂纹,此种情况一般在表面贴装器件波峰焊接时较为常见,俗称“爆米花”效应。见下图,红色区域表明有严重离层发生。

六、 离层的有效控制

离层在产生的同时对芯片表面形成较大的剪切力,当于剪切力大于芯片强度时,芯片的破裂就产生了。因此如何有效控制表面贴装MOSFET产品封装及波峰焊接过程中离层的产生,是降低产品上线早期失效的一个关键。为此国际JEDEC(电子工程设计发展联合会议)组织制订了《JESD22-A111》控制标准,可作为实际生产控制与检验标准。

(《JESD22-A111》全称为“Evaluation Procedure for Determining Capability to Bottom Side Board Attach by Full Body Solder Immersion of Small Surface Mount Solid State Devices” 中文解释为“评价决定表面贴装类产品浸入焊料性能的程序”)

同时正确地选用各种封装材料,特别注意选用低应力的高温装片焊料、选用低应力高耐湿性的塑封料、注意引线框架的选材和设计均是封装工艺工程师所需要重点研究的项目。

七、芯片强度

芯片强度是研究芯片碎裂的另一个重要参数。芯片强度各不相同,只有强度最低的才最容易碎裂失效。此外,强度分布范围很广,那些最“脆弱”的芯片碎裂时候的强度只相当于芯片平均强度的几分之一。因此只需设法将最“脆弱”芯片的强度提高或者予以剔除,就能从根本上提高芯片整体强度。下图给出了工艺应力与芯片强度的大致分布,两者重叠区域表示可能发生芯片碎裂。

硅和其它半导体材料属于高脆性材料,在材料完整无缺陷时,外加应力在样品上的分布是均匀的。它们在碎裂时是由于原子间的键发生断裂,因而它们的机械强度就决定于键的强度。在材料表面出现划痕后,外加应力时,出现应力集中现象。特别对于垂直于表面划痕的张应力,应力集中于裂纹的尖端。裂纹的扩展取决于裂纹尖端的应力分布。当其应力超过材料的应力强度因子时,裂纹就会失去稳定而发生扩展。因而对于脆性材料来说,表面划痕对材料的强度有很大的影响。尤其是对于半导体器件中的薄芯片,它的厚度很小,表面划痕的影响将更为严重。

八、表面划痕产生的原因分析与控制

表面划痕产生的原因之一:减薄(磨片):

硅片减薄,一般采用磨削法,是利用固定在特定模具上的尺寸适宜的金刚砂轮对硅片背面进行磨削,磨片引起的背面损伤(如图3)极大地影响了硅片的强度,尤其在硅片不同介质层的作用下,薄硅片很容易弯曲变形,产生了碎裂隐患。

改善手段:正确选用砂轮,砂轮磨料的粒度大小直接影响硅片亚表面的损伤程度。在细磨工艺后可采用湿法腐蚀工艺、常压等离子腐蚀、化学机械抛光等方法去除硅片背面的残留的晶格损伤层与残余应力,大大增强芯片强度,避免硅片因残余应力而碎裂。

表面划痕产生的原因之二:划片

芯片划片槽的断面往往比较粗糙,有少量微裂纹(崩角)和凹槽存在;同时有些地方划片时并未划透,装片时顶针向上顶使芯片“被迫”分离,致使断口呈不规则状。实验显示,划片引起的芯片边缘的损伤同样会严重影响芯片的碎裂强度。(见下图)

改善手段:改善划片工艺,尽可能地降低切割残余量,从而减少崩角产生的几率。

表面划痕产生的原因之三:粘片(装片)

粘片工艺包括装片机顶针从薄膜上顶起芯片,真空吸头吸起芯片将其粘结到芯片引线框架上。对芯片的损伤主要表现为顶针刺破蓝膜而损伤芯片。见下图:

改善手段:装片过程中,顶针的顶出高度、拾取高度、吸嘴的大小、顶针的选用等必须随芯片厚度、芯片大小不同而进行调整,同时对芯片背面顶针损伤进行有效质量监控,以防止顶针刺破蓝膜而损伤芯片。

结论

芯片碎裂已经成为表面贴装MOSFET 产品上线失效的主要模式之一,封装材料及工艺选配的不合理,在产品瞬间受热时产生的过大应力是造成产品失效的主要原因。而硅片减薄、划片、装片过程中对芯片的损伤是芯片碎裂的主要诱因。通过优化封装工艺,选配合适的材料与工艺,将热应力控制在安全范围内。以及通过改进研磨工艺,采用合理的划片技术,改善装片机的工艺参数,将有利于降低芯片的碎裂几率,从而进一步提高表面贴装MOSFET 产品可靠性。

来源:Internet

关键词:

芯片碎裂