嘉峪检测网 2024-10-06 10:08

导读:倒装芯片的静电损伤失效分析

静电放电ESD,对集成电路的危害巨大,会造成静电潜在损伤或者直接将集成电路的端口保护网络击穿,造成集成电路的失效。特别是对于倒装芯片,静电损伤是造成其失效的一大重要因素,这种静电损伤很难用扫描电镜显微镜直接找到,通过激光扫描显微镜对其进行失效定位可以快速准确的定位到损伤点。

样品为倒装芯片,视频输出端口输出异常,图像不显示。

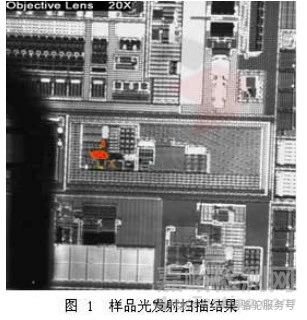

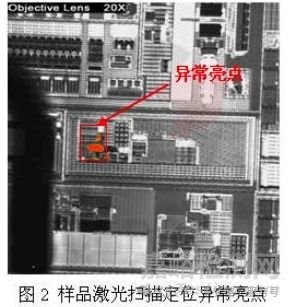

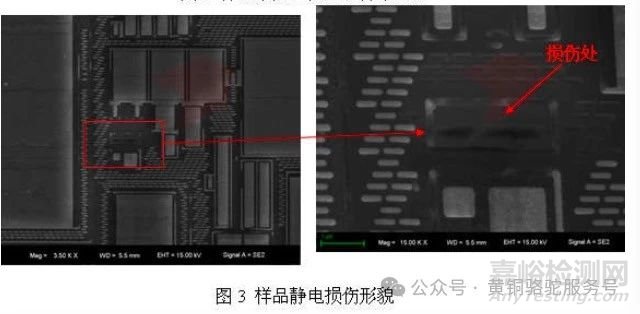

分析方法简述:电参数测试结果表明,样品的3.3v video IF supply端口对地端之间表现为漏电特性。对样品进行开封检查,表面未发现异常形貌。在漏电端口和vss之间施加电压,激光扫描显微镜下进行失效定位,可见样品芯片上存在异常亮点,该点在激光加热下,阻值发生变化,光发射显微镜的电源探测到该阻抗变化,并标记颜色。对存在异常亮点的芯片进行去层并用SEM放大观察,发现样品异常亮点附近存在静电损伤形貌。

通过激光扫描显微镜准确的定位了倒装芯片中的静电损伤点。对于衬底相对较薄的倒装芯片,无需对芯片进行任何处理,就可以直接应用激光扫描热激发技术进行失效定位,提高了失效分析的水平和效率。

倒装芯片一般都是静电敏感器件,在其贮存,运输和使用过程中,一定做好静电防护措施,避免静电对芯片造成损伤和击穿。其次,在芯片的设计层面,也可以通过电容保护,电阻保护,电阻-电容保护或者通过合理的布线技术,也可以增强芯片的ESD抵抗能力。

来源:Internet

关键词: 芯片