嘉峪检测网 2024-11-16 10:05

导读:本文介绍了芯片三维封装(TSV及TGV)技术。

一、半导体技术发展趋

以集成电路芯片为代表的微电子技术不仅在信息社会的发展历程中起到了关键性作用,也在5G通信、人工智能等前沿科技领域和无人驾驶、物联网等新兴应用领域扮演着至关重要的角色。

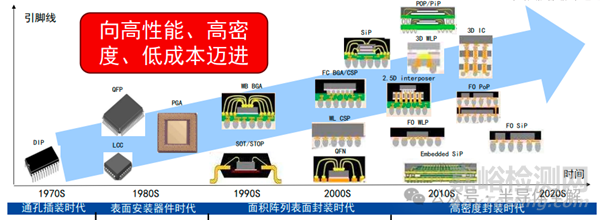

电子元器件逐步向着低成本、小型化、高度集成化的方向发展。这也要求集成电路技术(Integratedcircuit,IC)应该具有更高的I/O密度和更短的线宽、线距来提高芯片集成度。

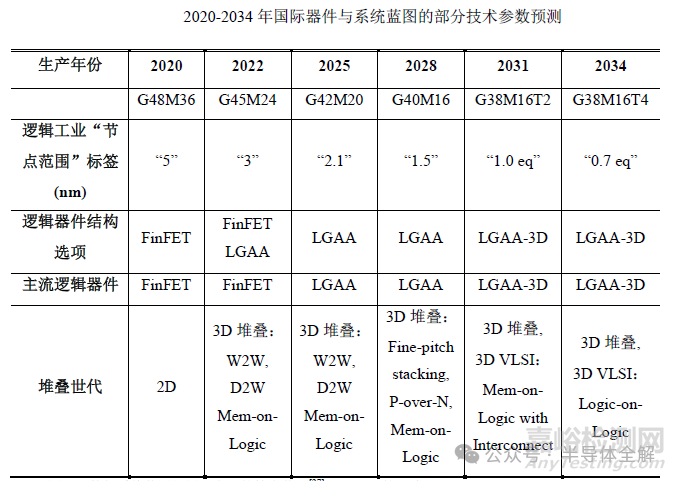

目前最前沿的光刻技术已进入到3-5nm阶段且后续尺寸缩小进展缓慢,芯片特征尺寸开始接近物理极限。过去微电子技术的发展历程,性能的提升很大程度上依赖于光刻技术的进步所带来的晶体管特征尺寸的减小。然而近年来随着技术节点的不断演进,晶体管的特征尺寸已逐渐逼近物理极限,想要继续沿“摩尔定律”缩减特征尺寸越来越困难。

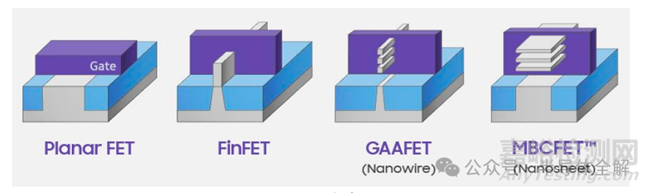

为了继续提升集成电路性能,半导体产业界近年来一方面继续减小晶体管特征尺寸,通过改进制造工艺来提升晶体管性能。

其中,鳍式场效应管(FinFET)及其衍生技术自22 nm技术节点以来在晶体管特征尺寸的缩减中扮演了重要角色。如图所示,相比于传统平面型晶体管,FinFET晶体管的栅极对沟道形成了三面环绕,从而增强了栅电压对沟道载流子的调控能力,减小了漏电流,提升了晶体管的电性能。

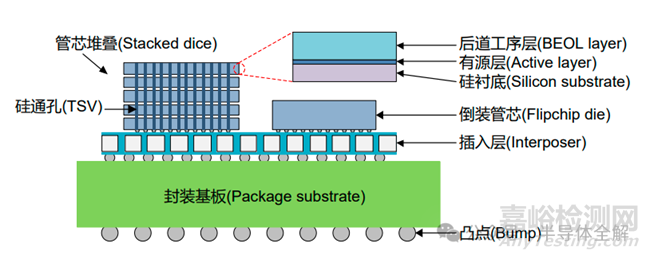

另一方面是采用新型封装技术来提升集成电路的整体性能,例如系统级封装(SiP)、三维集成(3-D integration)等通过将多层管芯(die)垂直堆叠,并使用硅通孔(TSV)实现管芯间的垂直互连,可大幅减小全局互连长度,从而减小延时和功耗,提升集成电路的整体性能。

接下来可以看下二维封装到三维封装的技术演变。

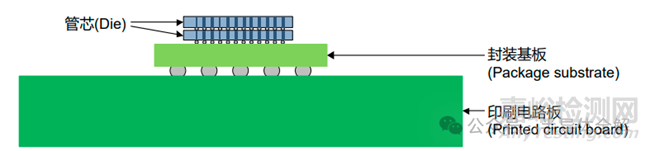

下图是传统二维封装方式:

下图是SIP(系统级封装)方式:

下图是三维集成封装方式:

其中,三维集成是非常有潜力的一种新型封装技术,近年来逐渐在实际产品中得到应用。

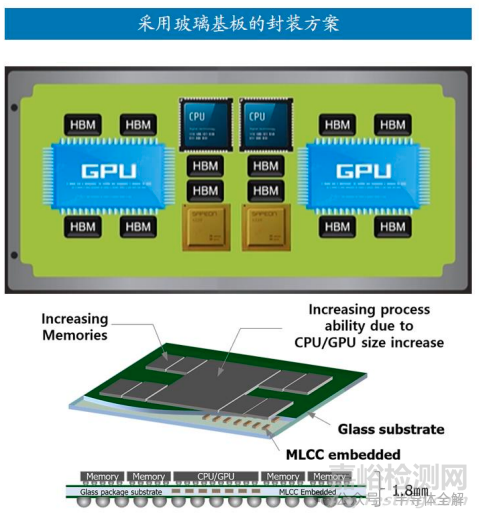

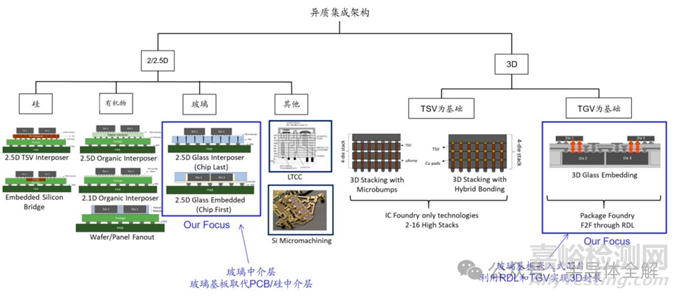

2.5D/3D先进封装技术是芯片系统关于延续摩尔定律的有效解决方案之一,该技术主要目的是通过在垂直方向上堆叠芯片以实现更高密度的集成。

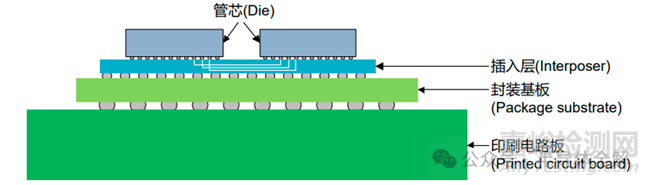

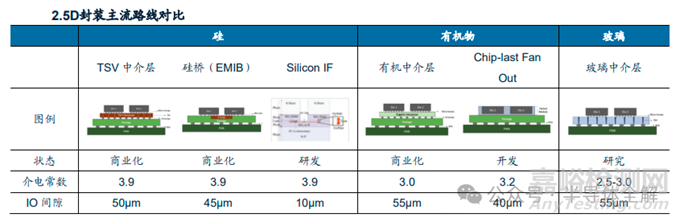

其中,3D封装技术与2.5D封装技术的差别主要在于3D封装技术是通过硅通孔(ThroughSiliconVia,TSV)或玻璃通孔(ThroughGlassVia,TGV)把所有芯片都垂直连接,而2.5D封装技术指的是将多个芯片平铺在中介层上,中介层上有再布线层,用于芯片间的水平互连,而中介层再通过通孔把芯片与封装基板相连,进而实现多个芯片的垂直互连,这种将多种不同材质、尺寸、功能封装到一个系统内的技术也被称作三维异质集成技术,其中实现中介层互连功能的关键工艺则是相应的通孔制备及孔金属化。

2.5D封装技术的关键之一是转接板为主要构成的中介层,目前转接板根据材料的不同有玻璃基、硅基、有机物三种类型,其中硅基转接板技术相对成熟,已经在实际生产中实现应用,然而硅基转接板在实际应用中存在高频损耗高和成本昂贵等问题,因此人们开始寻找硅的替代品。

现在硅基转接板最有潜力的替代者是玻璃基转接板,玻璃基转接板的优势在于它是绝缘体,高电阻不仅带来了更低的高频损耗以及更少的信号串扰,还可以避免制备介质层,降低了工艺难度;其次玻璃的热膨胀系数接近硅,这使得玻璃中介层与硅芯片构成的系统有着比有机中介层更高的热稳定性和机械稳定性,提高了可靠性;最后是玻璃表面光滑平整,这对于高密度布线而言是十分重要的。

二、先进封装技术

当前集成电路产品中很可能同时使用了三维集成技术和FinFET技术。

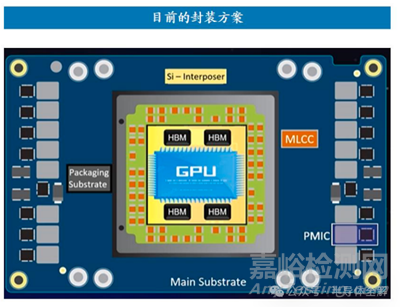

如图所示为当前一种典型的三维集成技术场景——高带宽内存(HBM),其中多层管芯堆叠之间的垂直互连由硅通孔实现,各层管芯的有源电路则可能是基于FinFET工艺制造。

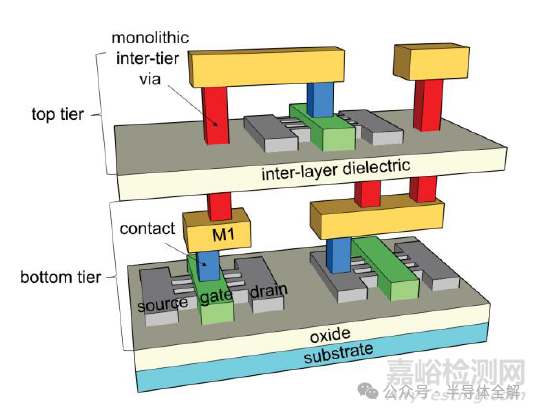

下图为新兴的单片三维集成(monolithic 3-D integration)技术,其中使用单片层间过孔来实现多层FinFET有源器件的互连,以实现更高的性能和更小的尺寸。其中,上下层Tier 之间由单片层间过孔(MIVs)实现互连。

另外,根据国际器件与系统蓝图(IRDS)的预测,3nm及以后技术节点的逻辑器件中将很可能同时使用这两类技术以满足性能需求,如表格所示。

由此可见,通过硅通孔实现垂直互连,每层管芯中的有源电路则可能是基于FinFET工艺制造,堆叠的管芯与倒装管芯之间通过插入层实现互连。

此外,在以印制电路板(Printed circuit boards,PCB)为主要构成的外界系统方面,提高集成度的方案是高密度互连技术(High Density Interconnection, HDI)。

这种技术通过通孔、盲孔、埋孔的共同作用实现多层布线以及层间互连,以此来满足器件小型化和高度集成化的需求。

孔金属化过程主要包括制备金属种子层和电镀填孔两个部分,其中金属种子层的作用是使不导电基板覆盖一层导体达到导电效果,金属种子层的连续性及完整性是孔导通两端、实现电信号互连的基础。

三、TGV工艺介绍

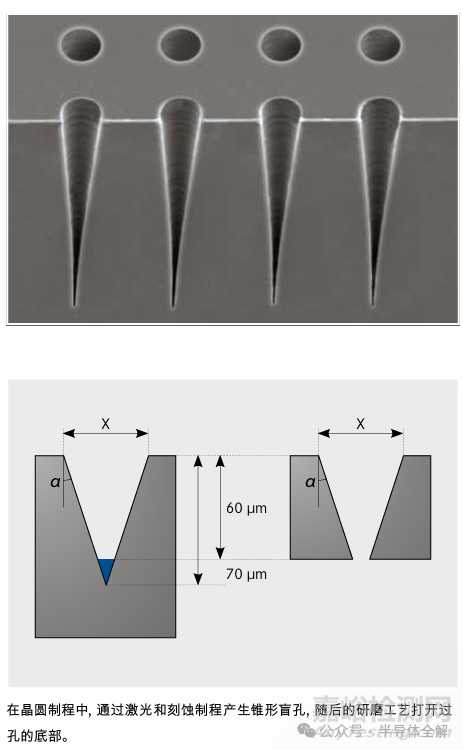

制备TGV玻璃通孔的方式很多,包括有喷砂工艺、超声波钻孔(ultra-sonicdrilling,USD)、激光诱导深度刻蚀(laserinduceddeepetching,LIDE)等方法,其中应用最为广泛的是激光诱导深度刻蚀的方法。

激光诱导深度刻蚀采用的超快激光光源,超快激光加工最显著的特征就是热影响区域小。对于传统激光而言,由于使用的激光脉冲宽度达到纳秒量级甚至更长,聚焦后的光斑为微米量级,因此在加工过程中,热扩散现象非常明显,严重影响加工精度。而超快激光的脉冲宽度非常窄,因此当超快激光作用在材料表面时,它的短脉冲时间意味着能量密度非常高,能够在非常短的时间内将能量局部集中在材料表面上。由于能量密度非常高,材料瞬间被加热到极高温度,于是材料就被以汽相形式蒸发,并且会带走部分材料内部的热量,使得周围区域的温度变化非常小,所以周围热影响区域很小。

该方法采用不同频率,不同聚焦类型的激光在玻璃上打出孔径在1μm以下的小孔,之后在以氢氟酸为主要构成的刻蚀液中湿法刻蚀特定时间来制备相应大小的TGV。

该方法目前可以制备的TGV侧壁垂直度和深宽比范围广,典型的TGV深宽比为1:10。此外,该制备方案还可以制备玻璃盲孔,经过金属填充后的玻璃盲孔可以实现信号屏蔽的功能,在特定器件上起到关键性作用。

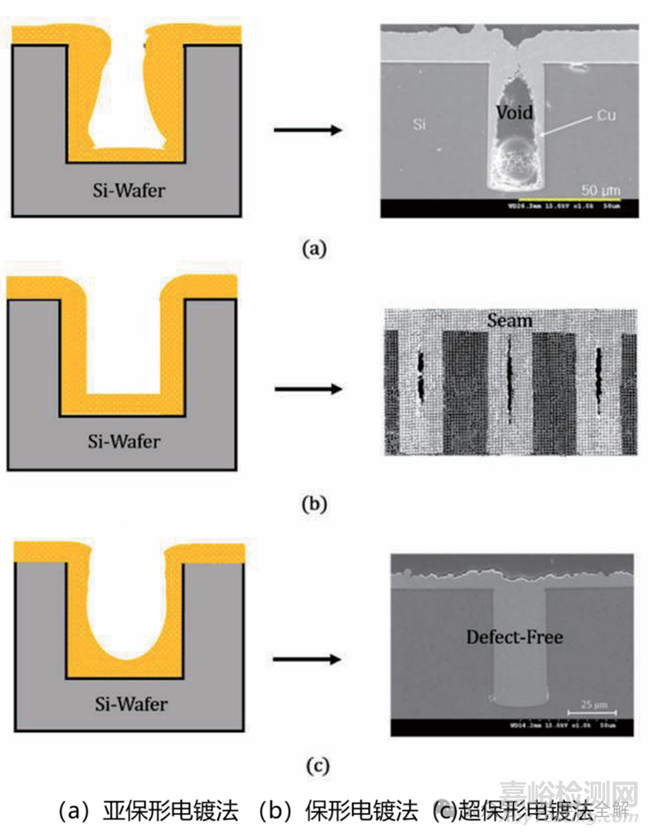

TGV的金属化主要包括有制备金属种子层和电镀填孔两个部分,其中电镀填孔主要与孔的形状、施加电流类型以及镀液内的添加剂成分有着较强的关联性。

制备金属种子层则是TGV实现三维互连的关键技术之一,一方面金属种子层是导电层进行电镀的基础,缺失了种子层的位置无法导电进行电镀。另一方面,因为交流电环境下电流具有趋肤效应,大部分电流都会通过种子层进行流通,因此一个完整连续的金属种子层对于TGV金属化而言十分重要的。

四、TGV金属化工艺

金属种子层制备方式包括物理气相沉积(Physical vapor deposition, PVD)、化学气相沉积(Chemical vapor deposition, CVD)、原子层沉积(Atomic layer deposition, ALD)、化学镀(Electroless plating)等,其中最常用于TGV金属化的是磁控溅射工艺,该工艺是PVD工艺的一种。

磁控溅射技术

典型的磁控溅射工艺需要先在基板上溅射Ti、Ta及其氮化物作为阻挡层,在阻挡电镀的Cu扩散至衬底的同时还作为粘附层加强Cu和玻璃间的结合力,这种方法在物件表面制备的薄膜均匀性好,沉积速率适中。

五、结论:

随着算力芯片领域,巨头积极投入研发。目前人工智能对数据中心和传输效率提出了更高的要求,尤其是对低功耗、高带宽的光模块的需求更加迫切,而高算力Chiplet芯片离不开Cowos、FOEB等先进封装平台。因此,随着AI芯片尺寸/封装基板越来越大,玻璃基封装被各大公司提上日程,期望玻璃基板能够构建更高性能的多芯片系统级封装(SiP)。

目前该技术标准主要由AMD、NVIDIA和海力士主推,英特尔认为基于玻璃基板、CPO将是先进封装 下一代主流技术。相比有机板和硅,玻璃基板的性能和密度均有提高,可以允许在更小的占用面积下封装更多的Chiplets,以此带来更低的整体成本的功耗,让未来数据中心和AI产品得到大幅改进。随着国家对半导体的重视,国内也有公司应用该技术。三维集成技术是一种非常有前途的芯片技术。

参考文献:

(1)闵球 三维封装集成电路中的电热特性分析研究[D].

(2)龙致远 电子互连微孔金属化方法及机理研究[D].

(3)王紫任 高速电路与电子封装中电连接故障对信号完整性影响研究[D].

(4)广发证券 半导体设备行业系列研究:玻璃基板从零到一,TGV为关键工艺[C].

(5)东方财富证券 Chiplet与先进封装共塑后摩尔时代半导体产业链新格局[C].

(6)华金证券 走进“芯”时代系列深度之六十七“25D、3D封装”[C].

来源:半导体全解

关键词: 芯片