嘉峪检测网 2024-10-27 18:19

导读:本文对BEoL阶段的与时间相关的电介质击穿(TDDB)模型进行研究。

前段制程(FEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- 栅极氧化物

2)热载流子注入(HCI)

3)负偏压温度不稳定性(NBTI)

4)表面反转(移动离子)

5)浮栅非易失性存储器数据保持

6)局部电荷捕获非易失性存储器数据保持

7)相变(PCM)非易失性存储器数据保持

后段制程(BEoL)常见的失效机理

1)与时间相关的电介质击穿(TDDB)-- low k材质电介质/移动铜离子

2)铝电迁移(Al EM)

3)铜电迁移(Cu EM)

4)铝和铜腐蚀

5)铝应力迁移(Al SM)

6)铜应力迁移(Cu SM)

封装/界面常见的失效机理

1)因温度循环和热冲击导致的疲劳失效

2)因温度循环和热冲击导致的界面失效

3)因高温导致的金属间化合物和氧化失效

4)锡须

5)离子迁移动力学(PCB)--组件清洁度

本文对BEoL阶段的与时间相关的电介质击穿(TDDB)模型进行研究

BEoL TDDB研究的对象:

1)low k材质电介质

2)移动铜离子

low k材质电介质

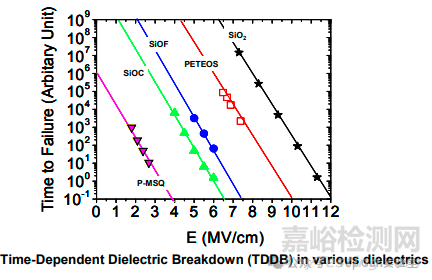

虽然与时间相关的电介质击穿(TDDB)是前段制程(FEoL)的一个关键可靠性课题,但TDDB不仅仅是栅氧化层的问题,如下图所示用于后端制程(BEoL)应用的不同电介质的TDDB寿命趋势与电场的关系。

注:

1)等离子体增强TEOS(PETEOS)的结果引用自参考文献[2];

2)SiO2 的结果是针对栅氧化层;

3)SiOF、SiOC 和多孔 MSQ(P-MSQ)是low k材质互连电介质的示例;

4)对于BEoL电介质,其电介质可靠性随着low k材质电介质常数的降低,击穿强度呈现下降趋势。

随着low k材质电介质引入到互连堆叠,BEoL TDDB也成为了关键可靠性课题。与传统的基于二氧化硅的BEoL电介质相比,low k材质能够显著改善RC性能(即减少电路延迟);但在漏电和耐击穿能力方面,比二氧化硅材质的栅氧化层要差得多。如上图所示,low k材质电介质通常表现出较差的TDDB可靠性特性。

相邻互连金属层之间的金属间电介质(IMD)间距正在接近几十年前使用的栅氧化层的物理尺寸。因此,讨论在电应力下电介质退化的物理模型类型很重要,特别是其与施加电场强度的相关性。

早期关于栅氧化层的工作表明,TDDB寿命模型与电场(E或1/E,参见前面关于栅氧化层TDDB的讨论以比较模型《FEoL TDDB模型》)呈指数关系。E模型将TDDB描述为键断裂模型,施加的电场可以拉伸硅-氧(Si-O)键,从而削弱它们并使它们发生热断裂。1/E模型遵循福勒-诺德海姆(F-N)传导模型,电子穿过电介质因加速导致电介质碰撞发生电离损伤。

在正常使用条件下的电场强度范围内,F-N传导不显著;同时,由于互连电极是金属(其少数载流子贡献可忽略不计),阳极空穴注入模型也不适用。因此,在较低电流下,low k材质的本征传导模型可参考普尔-弗伦克尔(Poole-Frenkel)或肖特基(Schottky)模型,TDDB寿命基于这些传导模型进行预估(建议遵循所谓的√E型模型)。

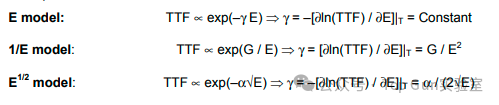

电场加速因子γ可用于表征在很宽电场强度范围内的TDDB数据,γ因子根据研究结果总结得出为一个经验值:不同模型中ln(失效时间)与电场的关系图的斜率。可使用下面列出的方程标识:

注:其中E是电介质中的电场,T是确定γ时的固定温度,TTF被视为TDDB测试的特征失效时间。G和α分别是1/E和√E模型中的场加速参数。

场加速因子随电场的变化可以从上述方程中预测。例如,E模型的场加速因子随电场恒定,其他模型预测观察到的场加速因子应随电场强烈变化。

low k材质电介质有多种形式,由于工艺和集成方面的原因,行业的趋势一直是采用基于氧化硅(SiOx)基质的材料。基于氧化硅的low k材质电介质已被证明在恒定电压应力下具有较差的耐电压击穿强度和明显更宽的失效分布,这些趋势归因于low k材质电介质中预先存在的缺陷,缺陷大致与low k材质电介质内的孔隙成正比。有趣的是,low k材质电介质TDDB仍然遵循在栅氧化层中发现的相同退化物理模型。即在105°C时,场加速因子γ≈4Naperians per MV/cm(约13eÅ的有效分子偶极矩)。

因low k材质电介质是通过有意在电介质中引入纳米级孔隙而获得的,所以材料的孔隙度是评估电介质电性能的一个重要特征。但从可靠性的角度来看,“孔隙”被认为是一个具有弱键的低极化率局部区域,在电应力下会引入电荷陷阱。渗流建模以及与孔隙成正比的缺陷假设可以解释low k材质电介质击穿强度的下降和更宽的失效分布。

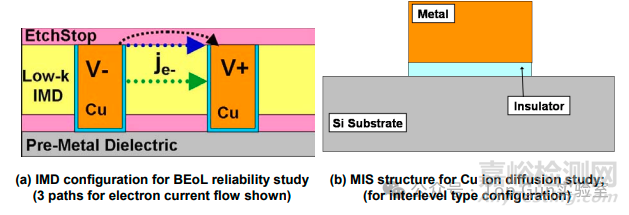

由于low k材质电介质的BEoL处理非常复杂,BEoL工序必然会改变low k材质电介质的局部特性,因此在使用先进的low k材质材料时,仔细评估其可靠性裕度是BEoL成功处理和集成这些新材料的必要部分。low k材质电介质的可靠性不仅仅会影响金属间的绝缘问题[下图(a)],还有金属层间和栅极-金属接触的几何结构也会收到影响。

另外,由于铜离子在电场下可移动,任何留下或允许铜离子进入电介质区域的缺陷都会使它们在金属电极之间漂移,并对TDDB可靠性产生不利影响,水汽的存在也会对互连可靠性产生负面影响。

使用E模型的low k材质电介质TDDB寿命预估示例:

目标:

使用E模型计算low k材质电介质在使用条件下因TDDB导致失效的加速因子(AF)。

注:外推的基础是从在加速失效的应力条件下获得的测试结构寿命数据得出的。

假设条件:

1)正常使用条件为:50°C芯片温度和0.3MV/cm的电场加速条件

2)加速条件为:125°C测试温度和4MV/cm的电场加速条件

3)电场加速参数/因子,γ:4Naperians per MV/cm

4)表观活化能Eaa:0.75eV

AF计算公式:

AF(TTFuse/TTFaccel)=exp[–γ(Euse–Eaccel)]*exp[(Eaa/k)(1/Tuse–1/Taccel)]

假设条件代入计算:

AF=exp[–4.0/(cm/MV)(0.3MV/cm–4MV/cm)]*exp[(0.75eV/8.62x10–5eV/K)(1/(273+50)K–1/(273+125)K)]=2.7x106*1.6x102=4.3x108

结论:因此,正常使用寿命将比观察到的加速应力寿命长约4×108倍。其中,2,700,000倍是由于电场加速引起的,因温度加速只有160倍。

注:从上述例子可知,电场加速因子远大于温度加速因子。因此,可在正常使用温度条件范围增大电场强度进行加速寿命测试试验。但加速寿命测试有一些必要的注意事项。

1)首先,在加速条件下(更高的施加电场和/或更高的温度)进行测试可能会导致新的失效模型,这些模型并非与接近正常使用条件下的相关失效一致(例如,low k材质电介质中的铜离子在高于200°C时明显变得可移动);

2)其次,在加速条件下高度活化的缺陷(例如,游离铜)的存在会极大地扭曲寿命预测,尽管在这种条件下检测到它们可以被视为进一步改进工艺的指标;

3)最后,测试结构的面积通常比实际器件中的互连面积小得多。

移动铜离子

如在影响器件功能的移动离子部分所提到的《移动离子失效模型》,在适度电场(≤1.0MV/cm)和温度(~100°C)条件下,锂、钠和钾之类的碱金属元素在SiO2之类的电介质中特别容易移动。

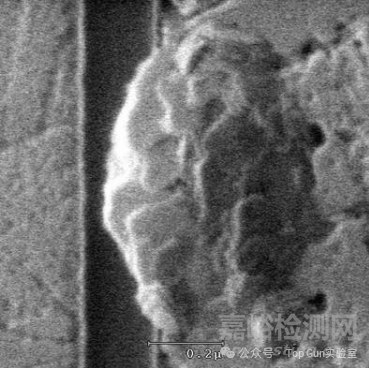

随着铜金属化成功集成到后段制程(BEoL)中,在电偏压下的移动铜离子是一个更严峻的问题。例如,沟槽/过孔金属阻挡层或沟槽电介质阻挡层对铜离子扩散的阻挡完整性丧失或者存在与铜相关的腐蚀缺陷,都可能导致BEoL的绝缘电介质可靠性大幅下降。通常,电场下的铜离子漂移导致互连的TDDB问题想比半导体器件中的表面反转(移动离子)更是一个问题。对于基于铜的互连金属,这种故障模型的机理是两个金属电极之间的局部low k材质电介质形成的金属短路桥,如下图所示。

注:在沉积覆盖电介质之前,对铜金属化进行化学机械抛光(CMP)和清洗可能会留下铜离子缺陷,这些缺陷未被阻挡材料完全与low k材质电介质隔绝。在施加的电应力条件下,铜离子可以穿过电介质区域发生漂移,导致金属间电介质(IMD)过早失效。严重的缺陷会对观察到的TDDB可靠性产生负面影响。

Cu+离子可以通过增加Si-O键的局部电场来催化正常的Si-O键断裂过程:Cu+离子将通过产生局部点缺陷对TDDB产生不利影响,这种点缺陷的产生在概念上类似于栅氧化层中的“空穴捕获”--增强Si-O键周围的局部电场,Si-O键断裂最终导致low k材质电介质失效。

对于铜离子导致low k材质电介质失效确切作用以及在何种浓度下铜离子漂移会驱动low k材质电介质击穿模型目前还没有达成共识。但很明显的是,充分遏制铜离子对于确保互连可靠性以防止电介质过早击穿和进行电介质可靠性评估至关重要。如果阻挡层的遏制铜离子失败,那么与大量铜离子漂移相关的大规模缺陷将以两种方式影响电介质的可靠性:

1)随着铜离子进入电介质并增加局部电场,有效电介质间距会逐渐减小;

2)铜离子漂移导致金属桥接缺陷,使两个电极短路。

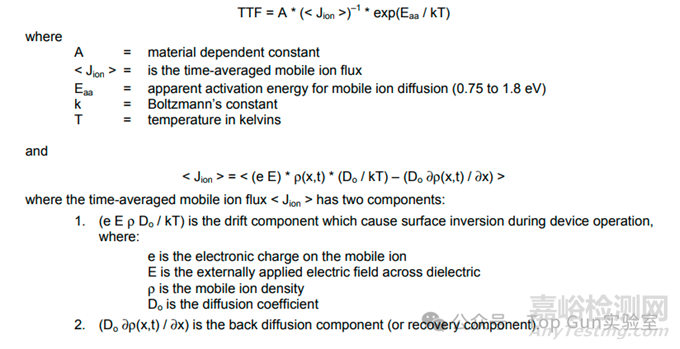

low k材质电介质中可移动铜离子的漂移最终桥接。可移动离子通量由电场强度和温度控制。因此,失效时间(TTF)的公式如下:

如果电场关闭并且对器件进行烘烤(即无偏压烘烤),则离子电流 Jion 有可能改变方向(反向扩散),器件可能会表现出一定程度的恢复,称为“失效烘烤恢复”;然而,在BEoL中,迁移的金属阳离子也很可能与来自阴极的电子重新结合,随后“沉积”形成永久短路通道,从而排除这种烘烤恢复的可能性。

将离子电流 Jion(x,t) 除以离子浓度 ρ(x,t),可得到离子漂移的净速度 Vion(x,t)。因此,失效时间的更明确表示为(电介质厚度)/ Vion(x,t)。

注:

1)首先,这个表达式是一个近似值。例如,如果发生了足够的金属沉积,那么在失效前的实际电介质间距可能小于标称电介质厚度,并且在应力期间的实际标称电场可能会随时间增加。

2)其次,公式对所有温度和电场都有效的假设是不正确的。例如,如果跳跃距离约为7Å,并且在电介质上施加0.2MV/cm的电场,公式在50°C时无效,但在250°C时有效。

通常,对于准确的加速因子确定和寿命预测,需要更复杂的漂移扩散表达式;然而,关于最有效的模型还没有明确的共识。

在《移动离子失效模型》研究中,Stuart发现Na的活化能为0.75eV,而其他所有物质约为1.1eV或更高。对于铜扩散到电介质中,不同的作者根据测试结构、测试方法和所用电介质的类型,估算出不同的Eaa值(范围从0.8eV到高达1.8eV。因此,对于本次讨论,铜离子漂移扩散的Eaa选择典型值1.0eV。

移动铜离子影响low k材质电介质TDDB寿命预估示例:

目标:

计算加速因子(AF),即AF=TTFuse/TTFaccel;通用模型(但不一定准确)。

假设条件:

1)正常使用条件为:50°C芯片温度和1.0MV/cm的电场加速条件

2)加速条件为:250°C测试温度和4MV/cm的电场加速条件

3)表观活化能Eaa:1.0eV

失效判据:[Cu+n]=1018个离子/立方厘米

AF计算公式:

AF(TTFuse/TTFaccel)=(Jion,use/Jion,accel)-1*exp[(Eaa/k)(1/Tuse–1/Taccel)]

AF=(Eaccel/Euse)(Tuse/Taccel)*exp[(Eaa/k)(1/Tuse–1/Taccel)]

忽略反向扩散,Jion≈~(eE)*(ρDo/kT)

假设条件代入计算:

AF=(4.0MV/cm/1.0MV/cm)((273+50)K/(273+250)K)*exp[(1.0eV/8.62x10–5eV/K)(1/(273+50)K–1/(273+250)K)]=4.0*0.6176*9.223x105=~2.3x106

结论:电场是一个低加速因子,温度是一个高加速因子。因此如果BEoL存在大量铜离子污染,电场低加速导致TDDB失效会造成芯片运行一定时间(较长的时间)失效。

相关文献:

1)R. Tsu, J.W. McPherson, and W.R. McKee, “Leakage and Breakdown Reliability Issues Associated with Low-k Dielectrics in a Dual-Damascene Cu Process,” IEEE International Reliability Physics Symposium Proceedings, 2000, pp. 348-353.

2)J. Noguchi, T. Saito, N. Ohashi, H. Ashihara, H. Maruyama, M. Kubo, H. Yamaguchi, D. Ryuzaki, K. Takeda, and K. Hinode, “Impact of Low-k Dielectrics and Barrier Metals on TDDB Lifetime of Cu Interconnects,” IEEE International Reliability Physics Symposium Proceedings, 2001, pp. 355-359.

3)E.T. Ogawa, J. Kim, G.S. Haase, H.C. Mogul, and J.W. McPherson, “Leakage, Breakdown, and TDDB Characteristics of Porous Low-K Silica-Based Interconnect Dielectrics,” IEEE International Reliability Physics Symposium Proceedings, 2003, pp. 166-172.

4) G.H. Haase, E.T. Ogawa, and J.W. McPherson, “Breakdown Characteristics of Interconnect Dielectrics,” IEEE International Reliability Physics Symposium Proceedings, 2005, pp. 466-473.

5)J. McPherson, “Determination of the nature of molecular bonding in silica from time-dependent dielectric breakdown data,” Journal of Applied Physics, Vol. 95, Issue 12, 2004, pp. 8101-8109

6)J. Kim, E.T. Ogawa, and J.W. McPherson, “A Statistical Evaluation of the Field Acceleration Parameter Observed During Time Dependent Dielectric Breakdown Testing of Silica-Based Low-k Interconnect Dielectrics,” IEEE International Reliability Physics Symposium Proceedings, 2006, pp. 478-483.

7)J. Suñe, D. Jimenez, and E. Miranda, “Breakdown Modes and Breakdown Statistics of Ultrathin SiO2 Gate Oxides,” Internation Journal of High Speed Electronics and Systems, Vol. 11, No. 3, 2001, pp. 789-848.

8)J.W. McPherson, R.B. Kamankhar, and A. Shanware, “Complementary model for intrinsic timedependent dielectric breakdown in SiO2 dielectrics,” Journal of Applied Physics, Vol. 88, Issue 9, 2000, pp. 5351-5359.

9)W. Wu, X. Duan, and J.S. Yuan, “A Physical Model of Time-Dependent Dielectric Breakdown in Copper Metallization,” IEEE International Reliability Physics Symposium Proceedings, 2003, pp. 282-286.

10)J. Noguchi, N. Miura, M. Kubo, T. Tamaru, H. Yamaguchi, N. Hamada, K. Makabe, R. Tsuneda, and K. Takeda, “Cu-Ion-Migration Phenomena and its Influence on TDDB Lifetime in Cu Metallization,” IEEE International Reliability Physics Symposium Proceedings, 2003, pp. 287-292.

11)M.M. Eissa, D.A. Ramappa, E. Ogawa, N. Doke, E. M. Zielinski, C.L. Borst, G. Shinn, and A.J.McKerrow, “Post-Copper CMP Cleans Challenges for 90 nm Technology,” Advanced Metallization Conference Proceedings, 2004, pp. 559-570.

12)F. Chen, K. Chanda, J. Gill, M. Angyal, J. Demarest, T. Sullivan, R. Kontra, M. Shinosky, J. Li, L. Economikos, M. Hoinkis, S. Lane, D. McHerron, M. Inohara, S. Boettcher, D. Dunn, M. Fukasawa, B.C. Zhang, K. Ida, T. Ema, G. Lembach, K. Kumar, Y.Lin, H. Maynard, K. Urata, T. Bolom, K. Inoue, J. Smith, Y. Ishikawa, M. Naujok, P. Ong, A. Sakamoto, D. Hunt, and J. Aitken, “Investigation of CVD SiCOH Low-k Time-dependent Dielectric Breakdown at 65nm Node Technology,” IEEE International Reliability Physics Symposium Proceedings, 2005, pp. 501-507. 13)N. Suzumura, S. Yamamoto, D. Kodama, K. Makabe, J. Komori, E. Murakami, S. Maegawa, and K. Kubota, “A New TDDB Degradation Model Based On Cu Ion Drift In Cu Interconnect Dielectrics,” IEEE International Reliability Physics Symposium Proceedings, 2006, pp. 484-489.

14)J.R. Lloyd, C.E. Murray, S. Ponoth, S. Cohen, and E. Liniger, “The effect of Cu diffusion on the TDDB behavior in a low-k interlevel dielectrics,” Microelectronics Reliability, Vol. 46, 2006, pp. 1643-1647.

15)S.-S. Hwang, S.-Y. Jung, J.-K. Jung, and Y.-C. Joo, “Study of Cu Migration-Induced Failure of Inter-Layer Dielectric,” IEEE International Reliability Physics Symposium Proceedings, 2006, pp. 673-674.

16)K.N. Tu, J.W. Mayer, and L.C. Feldman, Electronic Thin Film Science, Macmillan Publishing, New York, 1992, p. 46.

来源:Top Gun实验室