嘉峪检测网 2025-05-25 12:35

导读:本文介绍了半导体前端沉积工艺。

沉积工艺非常直观:将晶圆基底投入沉积设备中,待形成充分的薄膜后,清理残余的部分即可以进入下一道工艺了。

在半导体制程中,移除残余材料的“减法工艺”不止“刻蚀”一种,引入其他材料的“加法工艺”也非“沉积”一种。例如,Photo Process 中的光刻胶旋涂,也是在基底上形成各种薄膜;又如氧化工艺中 Silicon Wafer 的氧化,也需要在衬底表面添加各种新材料。那为什么要强调“沉积”工艺呢?

原因是半导体的微细化趋势。如今,市场对电子产品的性能和低电耗的要求越来越高,这就需要更加“微细”的半导体来做支撑。如果采用体积更小、耗能更低的半导体,就可以在电子产品中添加更多功能。想实现半导体的微细化,就需要由不同材料沉积而成的薄膜层,使芯片内部不同部分各司其职。金属层就是其中的一种。过去,半导体制造商曾采用导电性较高的铝做芯片的金属布线。但随着铝微细化技术遇到瓶颈,制造商就利用导电性更高的铜代替铝布线。但采用铜就出现了一个新问题,与铝不同,铜会扩散到不应扩散的地方(二氧化硅,SiO2)。为防止铜扩散,制造商们就必须在铜布线区形成阻挡层,即一种高质量的薄膜涂层。

1.介质薄膜

沉积材料主要有二氧化硅(SiO2),碳化硅(SiC)和氮化硅(SiN)等。

用作电路间的绝缘层,掩蔽半导体核心元件的相互扩散和漏电现象,从而进一步改善半导体操作性能的可靠性;

用作保护膜,在半导体制程的最后环节生成保护膜,保护芯片不受外部冲击;

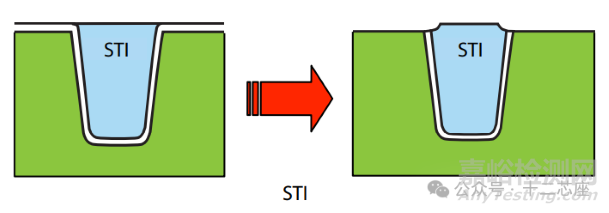

用作隔离膜,在堆叠一层层元件后进行刻蚀时,防止无需移除的部分被刻蚀。例如,浅槽隔离(STI,Shallow Trench Isolation)和金属层间电介质层(IMD,Intermetal Dieletric)。

2.金属薄膜

芯片底部的元件(晶体管)如果未经连接是起不到任何作用的。想要使不同的元件各司其职,必须将它们与其他元件和电源连接起来。元件的连接需要通过Ti、Cu 或 Al 等金属进行布线,连接金属布线和元件,还需要生成接触点(Contact)。

3.Others

除此之外,沉积工艺在晶体管的高介电性薄膜和用于多重曝光的硬掩模等方面应用范围也非常广泛。可以说,沉积在制造工艺中无处不在。随着半导体微细化发展,半导体需要更高质量、厚度更精准的薄膜。因此,过去以氧化工艺制作的高介电性薄膜,如今也开始以沉积方式制作。

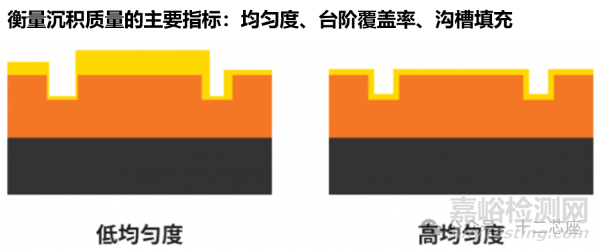

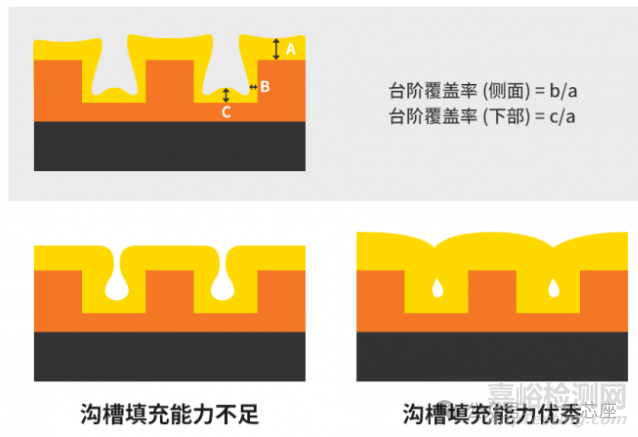

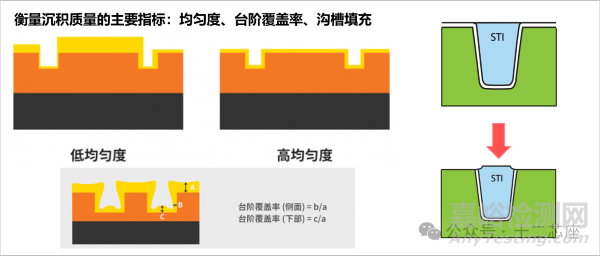

衡量沉积质量的主要指标:均匀度、台阶覆盖率、沟槽填充

1.均匀度(Uniformity)

顾名思义,该指标就是衡量沉积薄膜厚度均匀与否的参数。薄膜沉积和刻蚀工艺一样,需将整张晶圆放入沉积设备中。因此,晶圆表面不同角落的沉积涂层有可能厚度不一。高均匀度表明晶圆各区域形成的薄膜厚度非常均匀。

2.台阶覆盖率(Step Coverage)

如果晶圆表面有断层或凹凸不平的地方,就不可能形成厚度均匀的薄膜。台阶覆盖率是考量膜层跨台阶时,在台阶处厚度损失的一个指标,即跨台阶处的膜层厚度与平坦处膜层厚度的比值。台阶覆盖率越接近1,表明跨台阶处(底部或侧壁)膜层厚度与平坦处膜层相差越少,越远离1(即越小于1)表明跨台阶处的膜层厚度对比平坦处膜层厚度越薄。

3.沟槽填充(Gap fill)

沟槽填充是衡量沟槽(Gap)填充程度的一个参数。如图4所示,半导体表面有很多凹凸不平的沟槽,沉积过程中很难保证可以把所有沟槽都填得严严实实。沟槽填充能力差,就会形成孔洞(Void),会影响材料的致密性,从而影响薄膜强度,造成坍塌。如果说“等向性刻蚀”是没有方向选择性地移除了不该移除的部分,沉积工艺中的“沟槽填充能力差”即表明没有填充到该填充的地方。

Reference:

1.skhynix

2.Semiconductor Devices: Physics and Technology.

来源:Internet

关键词: 半导体