嘉峪检测网 2025-04-14 18:41

导读:本文介绍了电磁兼容整改芯片EMC问题案例分析。

1、问题现象描述

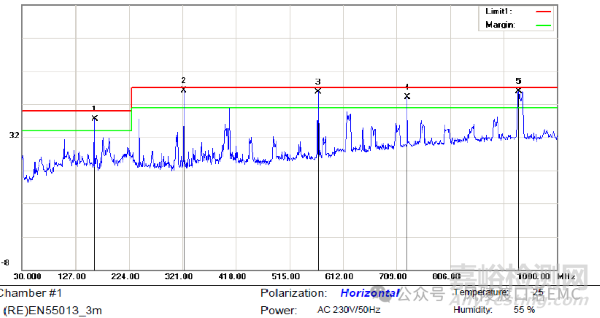

某款产品在3米法电波暗室进行辐射(RE)发射测试时,发现多个频点余量不满足6dB管控要求,具体测试数据如下:

图1:辐射发射测试数据

2、问题原因分析

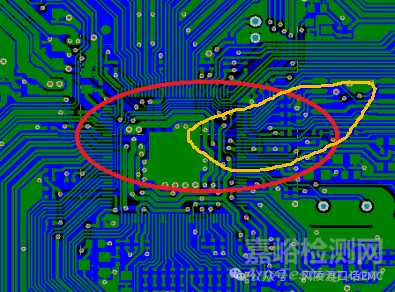

通过频谱分析仪近场探头分析定位到干扰频点来自于SPI Flash时钟信号的高次谐波干扰,深入分析发现SPI Flash时钟信号回流主芯片的参考地存在严重的分割情况,造成时钟信号回流面积变大,引起辐射发射测试超标。

图2:SPI Flash芯片PCB Layout图(修改前)

3、问题解决方案

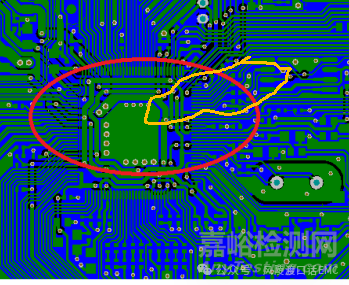

修改PCB Layout,调整SPI Flash时钟信号参考地平面,使之参考地平面保持完整性,并优化SPI Flash芯片其它信号布线,时钟信号两侧包地隔离串扰。

图3:SPI Flash芯片PCB Layout图(修改后)

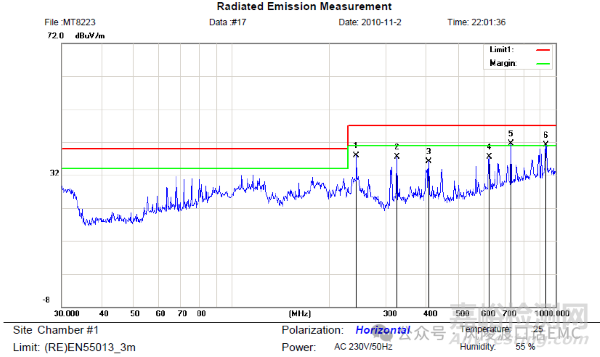

PCB Layout修改后,回板重新测试辐射发射,其结果满足6dB余量管控标准的要求,具体测试数据如下:

图4:SPI Flash芯片供电电源引脚频谱图

4、案例思考与启示

SPI Flash芯片时钟信号工作频率及高次谐波频率的辐射发射问题,在电子产品中是经常遇到。大部分工程师首先想到的是降低信号幅度,增加滤波电路,费了九牛二虎之力发现效果还不理想,往往是求解无门。即使是增加滤波电路勉强解决辐射发射问题,回头发现信号质量又不满足设计要求,被问题搞的焦头烂额,束手无策。

SPI Flash信号参考完整性的问题却容易被工程师们忽略,保持时钟信号参考完整性是解决辐射发射问题的杀手锏之一,本案例就深刻的诠释是参考完整性的重要性,且能够保证对策的低成本,还能够信号的高质量。

产生原因

• 芯片自身特性:芯片工作时会产生高频信号,如时钟信号、PWM脉冲信号及其谐波等,这些信号在环路中流动形成差模信号,若环路面积较大,信号频率较高,就会产生较强的辐射。此外,数据速率越高,寄生容性负载充电和放电越频繁,总平均电流增大,快速压摆率还会包含高频成分,导致发射加剧。

• 布局布线不合理:例如晶振距离板边太近,易导致晶振辐射杂讯;晶振下方有布信号线,会使信号线耦合晶振的谐波杂讯;滤波器件未按照信号流向排布,滤波效果变差。电源、地的布线存在地环路,或电源及对应地构成的回路面积较大;差分信号线对未同层、等长、并行走线,保持阻抗不一致;时钟等关键信号线未布内层,未加屏蔽地线或与其他布线间距不满足3W原则等。

• 滤波防护不足:接口信号的滤波、防护和隔离等器件未靠近接口连接器放置;电源模块、滤波器、电源防护器件未靠近电源的入口放置,电源的输入线较长,输入输出交叉走线。

• 屏蔽措施不到位:机箱没有屏蔽性能,或屏蔽层端接不良;屏蔽机箱上面的缝隙和空洞未处理好;整机钣金接地、钣金搭接未处理好。

测试方法

• 仿真测试:在产品设计初期,借助电磁仿真软件对芯片、PCB板等进行建模与分析,获取不同位置的频谱曲线及电场分布图。通过对比仿真与实测结果,优化仿真模型,提高仿真结果的精确度。

• 实测方法:将被测设备(EUT)置于电磁屏蔽暗室中,按照标准要求设置测试条件,使用场强探头、频谱仪等设备测量EUT在不同工作模式下的辐射发射情况。测试先用峰值检波器预扫,测试结果以准峰值为准。

解决措施

• 优化设计:在元器件布局阶段,合理安排强辐射器件或敏感器件的位置,如晶体、晶振等应远离单板拉手条、连接器,滤波电容靠近IC的电源管脚放置等。在PCB布线阶段,注意电源、地的布线处理,优化差分信号线对、关键信号线的走线方式。

• 采用低能量信号:尽可能对信号器件使用更低的电源电压,以减少通信信号中的能量,从而降低环境中的辐射能量。

• 使用抗辐射技术:如展频技术,通过改变信号的频率分布,降低单频点的辐射强度。

• 加强屏蔽和滤波:对强辐射晶振使用扩频手段;对网口、USB口等端口进行滤波;使用屏蔽电缆,处理好屏蔽层端接和屏蔽机箱缝隙等问题。

注意事项

• 仿真方法无法预测到谐波以及一些杂波的存在,实际测试时,频谱仪的读数可能会随近场探头位置以及角度的变化发生轻微偏移,导致测试结果存在一定的误差。

• 测试时要选择EUT辐射骚扰场强最差模式,因为EUT工作电流电压、负载情况、技术参数设置等均可能影响其辐射骚扰场强测试结果。

来源:Internet