嘉峪检测网 2025-05-07 18:57

导读:本文介绍了芯片设计中的LVS(Layout Versus Schematic)。

在集成电路(IC)设计领域,版图与原理图一致性检查(LVS,Layout vs. Schematic) 是确保设计准确性和制造成功率的关键环节。它用于验证芯片的物理版图是否与设计原理图保持一致,是实现电路功能正确性、保障产品质量的重要手段。

LVS检查通过提取和比对两种网表(netlist)—— 一份来自原理图设计,另一份从版图提取——来确保器件类型、数量、尺寸以及电气连接关系完全一致。这一过程涵盖了器件匹配、连通性验证、端口一致性等多个层面,能够有效发现诸如器件丢失、误连、短路、开路或几何误差等隐藏问题。特别是在现代SoC或多模块设计中,这种验证尤为重要,因为一个细微的不一致都可能导致芯片功能失效或性能下降。

此外,LVS流程往往还与寄生参数提取(Parasitic Extraction)和版图设计规则检查(DRC)紧密结合。寄生电容、电阻等参数对高频模拟电路或高速数字路径影响显著,而LVS确保其建立在正确的电气结构基础上,从而为后续时序分析、信号完整性分析打下坚实基础。

拥有一套完善且高效的LVS验证流程,不仅能够在设计早期阶段及时定位错误,避免问题流入流片阶段,还能大幅减少反复修改和返工所造成的时间和成本损失。对芯片设计企业而言,LVS不仅是验证环节,更是提升设计质量、优化流片成功率、加速产品上市周期的核心保障。

因此,LVS在现代IC设计流程中扮演着“设计闭环的守门人”角色。只有在LVS验证无误的前提下,设计才能进入Tape-out阶段,迈向晶圆制造。这一环节的严谨性直接决定了设计交付的可靠性与最终芯片的成败。

1.理解IC设计中的版图与原理图一致性验证(LVS)

在集成电路(IC)设计中,版图与原理图一致性检查(LVS,Layout versus Schematic) 是确保物理实现与设计意图一致性的关键验证步骤。通过对比版图与原理图,LVS不仅验证电路结构的准确性,还直接影响到芯片的功能正确性、可制造性和最终产品的可靠性。

1.1 LVS检查的核心组成部分

LVS验证通常包括以下关键环节,每一项都为最终设计的一致性提供不同层面的保障:

网表对比(Netlist Comparison):将从原理图生成的参考网表与从版图提取的实际网表进行比对,确认电路中所有器件、端口及其连接关系是否一一对应,防止电路逻辑结构发生偏差。

寄生参数提取(Parasitic Extraction):通过提取金属互连、电容、电阻等寄生参数,建立更为真实的电路模型,用于后续电路仿真与性能分析。例如,对于高速信号路径或模拟电路,寄生电容的影响可能导致信号失真或相位漂移。( “寄生参数” (Parasitic Parameters)是指在电路设计与制造过程中,非理想因素所引入的额外电气特性。这些参数不是电路设计者本意添加的,但由于物理结构、材料特性或制造工艺等原因而不可避免地存在。)

|

类型 |

解释 |

常见来源 |

|

寄生电阻 (Parasitic Resistance) |

导线、电极等非理想导体存在一定电阻,会导致电压下降、功耗增加 |

金属布线、电极接触、电源网络路径等 |

|

寄生电容 (Parasitic Capacitance) |

不同导体之间因空间距离过近而产生电容效应,可能引起信号延迟或耦合干扰 |

层间导线、晶体管栅极与衬底、金属层之间 |

|

寄生电感 (Parasitic Inductance) |

电流变化时在导线中感生出的感应电压,可能引发电源噪声、信号完整性问题 |

电源线、长导线、封装引脚 |

|

寄生器件效应 (Parasitic Devices) |

电路结构无意中形成了新的元器件,比如双极晶体管或MOS结构,可能引发 latch-up 等问题 |

CMOS结构中的寄生晶体管、PNPN结构 |

设计规则检查(DRC,Design Rule Checking):虽然DRC不直接比较原理图与版图,但作为辅助流程,它确保版图在物理实现过程中遵守代工厂的几何规则、间距规则和层次规则,是LVS之前的重要预处理环节之一。

LVS(Layout Versus Schematic)流程主要包括版图网表的提取与版图与原理图网表的比对两个核心步骤。其流程如图所示。

左侧流程:Layout路径(从GDS到版图网表)

|

阶段 |

步骤名称 |

输入 |

输出 |

使用工具 / 模块 |

关键说明 |

|

1 |

Layout (GDS) |

GDS 文件(GDSII Stream Format) |

布局物理数据(包含几何结构、图层、元件位置) |

IC版图设计工具(IC Compiler II、Virtuoso) |

- GDS 是IC行业标准的版图文件格式。 |

|

来源于IC布局工具(如IC Compiler II) |

- 记录IC物理实现的图层、形状与元件布局。 |

||||

|

|

- 在LVS中作为版图比对的输入数据。 |

||||

|

2 |

Extraction(版图提取) |

GDS 文件 |

版图提取网表(Layout Netlist) |

LVS 工具的 Extraction 引擎 |

- 提取逻辑连接关系和器件信息(如MOS、电阻、电容等)。 |

|

规则库(Rule Deck) |

(如Calibre、IC Validator) |

- 根据图层定义与规则库进行识别。 |

|||

|

|

|

- 可支持寄生参数提取(RC),但LVS中通常只关注拓扑结构。 |

|||

|

3 |

Extracted Netlist(提取网表) |

版图提取结果(电气连接+器件信息) |

Netlist 文件(Spice或SPF格式) |

LVS 工具 |

- 表示从物理版图还原出的电路结构。 |

|

- 供后续与原理图路径生成的网表进行结构比对。 |

|||||

|

- 是实际制造后电路结构的 “反向建模” 。 |

右侧流程:Schematic路径(从Verilog到原理图网表)

|

阶段 |

步骤名称 |

输入 |

输出 |

使用工具 / 模块 |

关键说明 |

|

1 |

Schematic (.v netlist) |

Verilog 格式的功能网表(Functional Netlist) |

原始设计意图网表 |

逻辑设计工具、EDA综合工具 |

- 用 Verilog HDL 描述电路的逻辑功能和模块结构。 |

|

由设计人员编写或由逻辑综合工具生成(如 Design Compiler) |

(如 Design Compiler) |

- 是 “行为级” 或 “结构级” 电路模型。 |

|||

|

|

|

- 通常不包含几何信息,仅描述逻辑功能。 |

|||

|

|

|

- 是设计者设计意图的起点。 |

|||

|

2 |

ICV Nettran(网表转换) |

Verilog 网表 |

Spice / ICV 格式的等效网表 |

IC Validator (ICV) 中的 Nettran 模块 |

-将 Verilog 网表转换为 LVS 工具能识别的格式(Spice或ICV格式)。 |

|

转换规则(Nettran Rule File) |

- 提取逻辑器件(如MOSFET、NAND门等)结构。 |

||||

|

|

- 生成具有器件及连线描述、与版图网表结构一致的形式。 |

||||

|

|

- 关键在于统一 “语法语义” 供LVS比对。 |

||||

|

3 |

Spice ICV Netlist(等效网表) |

转换后的 Spice 或 ICV 网表格式 |

原理图等效网表(Reference Netlist) |

LVS 工具读取该网表参与比对 |

- 结构上与从GDS提取出的Layout Netlist一致或接近。 |

|

(兼容布局提取网表) |

- 包含器件、节点、端口、子模块调用信息。 |

||||

|

|

- 用于与Layout网表进行逐一比对(器件、连线等)。 |

||||

|

|

- 是 “设计意图” 的结构映射形式。 |

中间部分:比对过程

1. LVS Compare(LVS 比对)

在这个阶段,工具会将“提取网表”和“原理图网表”进行逐一比对。

比对内容包括:

器件数量是否一致(如多少个NMOS、PMOS等);

器件类型是否一致;

网络连线是否一致;

器件连接方式、端口命名、子模块调用是否匹配;

等效性文件中定义的Cell匹配是否正确。

若比对全部通过,则称为LVS clean;否则将生成详细错误报告供调试使用。

最终输出:LVS 结果数据库

2. LVS Result Database(LVS结果数据库)

这是 LVS 工具生成的结果文件,包含:

比对是否通过(Clean 或 Failed);

不匹配的器件或网络详情;

等效点(Equivalence Point)文件;

错误日志及调试建议。

工程师可根据此数据库中的信息,定位设计或版图中的差异并进行修正。

在版图提取步骤中,工具从 GDS 文件中提取出所有器件及其之间的连接信息,生成版图网表。同时,工具还生成一个等效点文件(Equivalence Point File),用于在比对过程中标识版图与原理图之间的匹配点。

在比对步骤中,提取出的版图网表将与原理图网表进行详细比对。若两个网表完全一致,工具将输出通过(clean)结果;若存在不一致,则会生成包含错误详情的报告。

在比对过程中,工具主要进行以下方面的检查:

比较原理图与版图中的器件数量是否一致;

比较原理图与版图中的网络(Net)数量是否一致;

比较器件类型是否匹配;

生成比对结果报告。

若存在问题,错误报告将列出不匹配的器件、不正确的网络连接等信息,这对于工程师定位和调试 LVS 问题非常有帮助。常见问题如下:

|

问题类型 |

定义 |

成因 |

LVS报告中的表现 |

备注 |

|

Open(断开连接) |

设计中本应连接的两个或多个形状没有真正相交或接触,导致网络中断,形成浮空连接。 |

- 相同网络名的图形未接触或重叠 |

- 提取器将一个原理图网络识别为两个或多个版图网络 |

浮空连接可能导致芯片严重功能故障,是高优先级问题 |

|

- 版图布线错误或缺失 |

- 导致版图网络数多于原理图网络数 |

|||

|

- 自动布线遗漏 |

- 报告中列出 “断开的网络” 和其对应的多个版图网络名 |

|||

|

- 单元间Metal未连通 |

|

|||

|

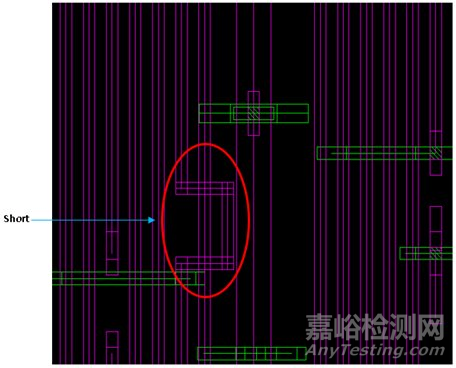

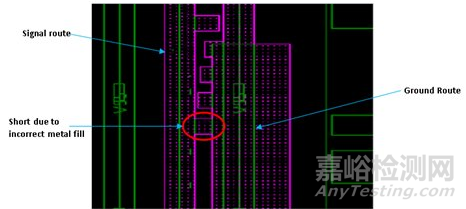

Shorts(短路) |

不同网络意外连接,导致原本应隔离的网络互相导通。 |

- 不同网络的图形重叠/交叉 |

- 提取器将两个原理图网络识别为一个版图网络 |

短路可能在功能测试前被忽视,但会在芯片烧毁或性能异常中暴露 |

|

- LEF缺失routing blockage |

- 导致版图网络数小于原理图网络数 |

|||

|

- 手动布线或金属填充出错 |

- 报告中列出 “合并的短路网络” 和合并前的网络名 |

|||

|

- 宏单元内部金属与外部布线冲突 |

|

|||

|

Missing components(器件缺失) |

LVS 流程中找不到设计中引用的某些单元,导致器件不匹配。 |

-GDS 或 Spice 文件未导入完整 |

- 报告中指出缺失某个单元(如ABC) |

需根据cell的实际功能决定是否必须包含 |

|

- Cell未在LVS使用列表中注册 |

- LVS 比较失败,提示 “Missing cells” |

|||

|

- 实例存在但未提供定义 |

|

|||

|

Missing global net connect(全局网络未连接) |

电源/地网络(PG net)未正确连接到单元的 PG 引脚。 |

- 未使用 connect_pg_net 命令连接PG网络 |

- 报告中出现大量 device mismatch 错误 |

在设计初始化阶段配置PG网络连接至关重要,否则大量器件都将匹配失败 |

|

- PG引脚名称未与设计网络名称对应上 |

- 多个单元VDD/GND引脚未连接 |

|||

|

|

|

1.2 核心验证参数

LVS验证不仅是比对结构,更关注以下几个核心参数,确保设计逻辑无误,制造可行:

器件匹配(Device Matching):包括晶体管、二极管、电阻、电容等器件的类型、尺寸、方向是否准确。如果在版图中器件未正确实例化或参数不符,可能导致LVS错误。

连线与互连(Wiring and Connectivity):确保所有信号线、电源线、地线的连接方式与原理图一致,避免短路、断路、串扰等问题,这对于复杂SoC或模拟IC尤为关键。

几何形状与尺寸(Geometry and Dimensions):检查器件布局的空间分布和形状是否合理,是否影响工艺流程或引入电气性能偏差。

1.3 所用工具与技术

为实现高效、可靠的LVS验证,业界常用以下先进的EDA工具:

Cadence Virtuoso:专注于模拟与混合信号IC设计,集成原理图编辑、版图绘制及LVS验证功能,适合高精度电路验证。

Synopsys Hercules:适用于大规模数字或混合电路设计,支持高并行性LVS流程,能快速处理复杂多层金属结构。

Mentor Calibre:被广泛用于先进制程的DRC/LVS/PEX流程,具备强大的定制化规则支持与高精度校验能力,是晶圆代工厂标准支持工具之一。

这些工具往往与流程自动化平台(如Cadence Innovus、Synopsys ICC)结合使用,实现全流程验证闭环,大幅提升设计效率与成功率。

1.4 面临的典型挑战

随着制程工艺演进至7nm甚至更先进节点,LVS验证面临的挑战也愈加严峻,包括:

• 多电压域、异构器件引发的跨层次比对复杂性增加。

• 高密度互连结构带来的连通性混淆与器件重构难度上升。

• 类比电路的器件对称性和匹配精度验证需求变高。

• 使用IP核或第三方模块时,黑盒/灰盒模型验证策略需要优化处理。

针对这些问题,设计团队必须采用模块化验证策略、层次化比对技术以及脚本自动化手段,提高LVS效率与准确性。

通过严谨执行LVS流程,设计团队不仅能够在Tape-out之前及时发现并解决设计偏差,避免流片失败,还能提高设计数据的可信度,为后续工艺仿真、电路优化提供坚实基础。LVS验证作为IC设计流程的核心环节之一,已经成为确保设计质量、提升良率、降低风险与缩短产品上市周期的重要保障手段。

2.LVS在半导体制造中的关键作用

在竞争激烈、技术迅速演进的半导体行业中,确保设计正确性和提升芯片良率已成为产品能否成功量产的决定性因素。版图与原理图一致性检查(LVS, Layout versus Schematic),正是实现这一目标的重要质量控制环节,其作用贯穿从IC设计验证到制造交付的全过程。

LVS检查通过将设计原理图中的功能描述与实际版图中实现的器件及其互连结构进行一一比对,确保版图忠实还原设计意图。它可以及时发现隐藏在复杂电路结构中的连线错误、器件缺失、参数不符或连接歧义等问题,这些问题若在制造阶段被发现,将会造成昂贵的流片返工和项目周期延误。

2.1 LVS对良率与成本的影响

LVS不仅是保障功能正确性的工具,更是控制制造成本、提高产品良率的核心手段:

降低缺陷率:通过在流片前发现版图错误,防止缺陷产品流入生产环节,有效减少芯片返修与报废,提高整体成品率。

控制制造成本:早期发现并修复问题,能够避免因逻辑错误或互连失误导致的多次流片,从而显著节省昂贵的晶圆成本、测试资源和工程人力。

提升产品一致性:LVS验证有助于确保各批次芯片在功能和性能上的一致性,减少因工艺波动带来的系统级问题,提升客户对产品稳定性的信任度。

支撑大规模量产:在先进制程节点和复杂SoC设计中,借助自动化LVS流程,可快速对多个模块或IP核进行统一验证,提升验证效率,支持更大规模、高复杂度的芯片稳定流片。

|

LVS检查的关键优势 |

对半导体制造的影响 |

|

提升设计完整性 |

降低制造成本 |

|

确保版图与原理图在器件、连线、网络结构上的一致性,避免功能性错误进入流片阶段 |

通过减少因设计错误导致的返工与流片失败,显著节省制造资源与时间 |

|

提高良率 |

提升产品质量水平 |

|

减少版图错误带来的器件失效,提升成品芯片的有效产出比例 |

确保电气连接正确性,保障芯片在功能、电气参数上的一致性和可靠性 |

|

降低缺陷率 |

增强企业市场竞争力 |

|

及时发现和修复潜在连接错误、器件不匹配等问题,从源头控制失效风险 |

缩短设计周期、提高一次通过率,加快产品上市速度,提升客户满意度 |

2.2 LVS与制造流程的协同价值

LVS不仅仅是一项独立的设计验证任务,更是半导体制造流程中与前后工序紧密耦合的桥梁:

|

步骤 |

名称 |

内容说明 |

目标 |

使用工具 |

注意事项 |

|

1 |

Design Specifications |

设计起点,由系统/架构工程师提供芯片目标参数,如功能、电压、频率、功耗、I/O要求等 |

- 明确功能需求(如增益、带宽、噪声) |

无工具依赖(文档或模板形式) |

- 规范需无歧义,避免设计返工 |

|

(设计规格) |

- 定义技术规格(CMOS工艺、平台) |

- 内容必须详细全面 |

|||

|

|

- 指导原理图和版图设计 |

|

|||

|

2 |

Schematic Capture |

使用EDA工具绘制电路连接图,实现功能模块 |

- 实现功能结构 |

Cadence Virtuoso、LTspice、Mentor Graphics |

- 管脚命名需统一一致 |

|

(原理图绘制) |

- 定义引脚连接与网络关系 |

- 保证连接正确、无悬空或短路 |

|||

|

3 |

Create Symbol |

将模块电路生成抽象符号(Symbol)以供系统层级调用 |

- 抽象电路模块以便复用 |

Cadence Virtuoso Symbol Editor |

- 端口顺序与原理图一致 |

|

(生成符号) |

- 用于更大系统中的层级集成 |

- 命名清晰、方向标识准确 |

|||

|

4 |

Simulation |

进行DC、AC、Transient仿真,验证电路性能 |

- 验证电路功能是否符合设计规格 |

Spectre、HSPICE、Eldo、LTspice |

- 使用PDK中提供的精确模型 |

|

(电路仿真) |

- 分析关键指标(增益、带宽、功耗、噪声、失真等) |

- 仿真数据需归档,便于评审和追溯 |

|||

|

5 |

Layout |

将电路转换为物理几何图形,准备制造 |

- 满足电气与工艺规范 |

Cadence Virtuoso Layout Editor |

- 遵循Foundry工艺规则(线宽、间距) |

|

(版图设计) |

- 考虑面积、寄生、电源分布等 |

- 考虑匹配、寄生、电容电阻效应 |

|||

|

6 |

Design Rule Check (DRC) |

自动检查版图是否违反工艺设计规则 |

- 检查版图与工艺规则是否一致 |

Mentor Calibre DRC、Cadence Assura、Synopsys ICV |

- 报错必须修复直至DRC通过 |

|

(设计规则检查) |

- 避免制造错误 |

- 是后续步骤的前置条件 |

|||

|

7 |

Extraction |

提取电路中的RC寄生,生成带寄生的网表 |

- 获取真实性能影响因素 |

Calibre xRC、Assura RCX、ICV |

- 模型需准确反映金属、电介质、过孔等 |

|

(寄生参数提取) |

- 为LVS与仿真准备输入 |

- 可选择提取层级控制仿真效率 |

|||

|

8 |

Layout vs. Schematic (LVS) |

比较提取网表与原理图网表的一致性 |

- 验证功能一致性 |

Calibre LVS、Assura LVS、ICV LVS |

- 常见问题:短路、开路、器件漏绘、网络不一致 |

|

(版图与原理图对比) |

- 检查器件、连线完整性 |

- 调试需结合报错提示与物理版图 |

|||

|

9 |

Post-Layout Simulation |

使用PEX网表进行仿真,评估寄生影响 |

- 验证寄生对性能的影响 |

Spectre + PEX Netlist、HSPICE + Extracted Netlist |

- 若性能下降需调整版图或重新布局 |

|

(布局后仿真) |

- 判断是否仍满足规格要求 |

- 是验证制造一致性的重要环节 |

与DRC(Design Rule Check)协同:先执行DRC确保物理规则合规,再通过LVS验证功能一致性,构建完整的制造准备验证链条。

与寄生参数提取(PEX)集成:在LVS完成器件与连接一致性验证之后,通过PEX提取寄生元件,进一步提升后仿真精度,优化性能预测。

与工艺模拟与测试反馈闭环联动:部分代工厂会将实测缺陷反馈到设计端,并通过LVS工具溯源问题根本原因,优化设计规范,形成制造质量提升闭环。

2.3 应对先进制程挑战的LVS发展趋势

随着芯片设计进入7nm、5nm甚至更先进节点,LVS验证面临更高复杂度和更严苛的性能要求。为应对挑战,LVS正呈现以下发展趋势:

• 支持异构集成与多芯粒(chiplet)架构:验证跨芯片模块互联一致性,确保整体系统可靠运行。

• 增强AI辅助诊断与可视化调试能力:借助机器学习自动识别典型错误模式,提升调试效率。

• 强化对模拟/射频/高速IO等复杂器件结构的建模与对比能力:增强匹配度与灵敏度。

• 与数字孪生建模、PPA协同优化集成:让LVS结果参与性能功耗面积(Power, Performance, Area)决策过程。

总 结

LVS不仅是确保IC设计质量的防线,更是提升制造良率、优化成本结构、缩短项目周期的战略性技术手段。通过将LVS深度嵌入整个芯片开发和制造流程,半导体企业能够在降低风险的同时,充分发挥设计潜力,打造高性能、高可靠性、高性价比的芯片产品,从而在激烈的市场竞争中稳占优势。

参 考:

1.What is Layout vs. Schematic (LVS) check, and why is it essential?

2.Layout versus Schematic (LVS) Debug

3.VLSI Design Quick Guide

来源:芯片技术与工艺

关键词: 芯片