嘉峪检测网 2025-06-28 15:59

导读:综合分析确认,CPLD 芯片的 Bank0 和 Bank1 I/O 区域发生了严重的过电击穿,导致VCCIO0、VCCIO1 及核心 VCC 对地短路。

故障现象确认: 电路板上出现3.3V电源对地短路故障。通过在板热点定位技术,确认故障源为CPLD芯片失效。

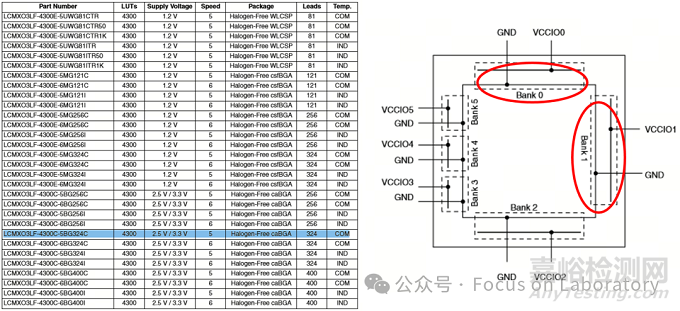

拆解后阻抗测试: 将失效CPLD芯片解焊取下后,对其电源引脚进行对地阻抗测量:

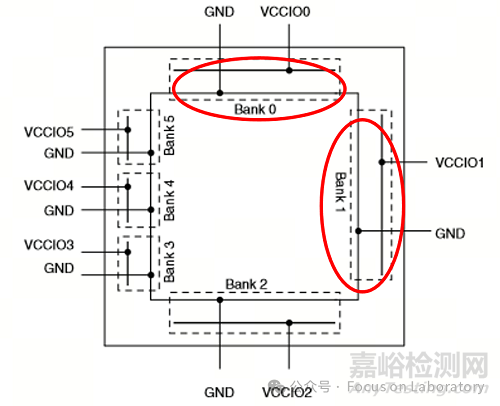

短路确认: VCC(核心电源)、VCCIO0 和 VCCIO1(I/O Bank 0 & 1 电源)引脚均呈现对地短路状态。

阻抗正常: VCCIO2、VCCIO3、VCCIO4 和VCCIO5(I/O Bank 2, 3, 4 & 5 电源)引脚对地阻抗测量结果正常。

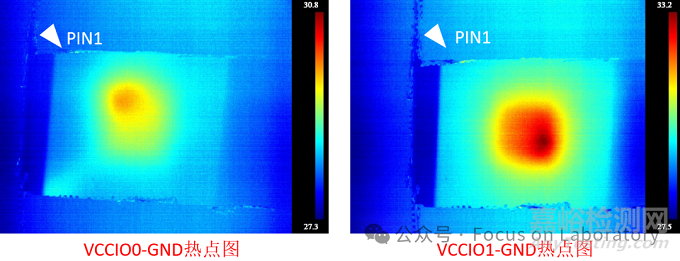

单体热点测试:对取下的故障芯片单独进行热点定位测试。

当对 VCCIO1 引脚加电时,观察到的热点分布形貌,与对 VCCIO0 引脚加电时观察到的形貌一致。更重要的是,上述 VCCIO0 和 VCCIO1 加电产生的热点形貌,与故障发生时整机(电路板)上电时的热点形貌完全吻合。

当对 VCC(核心电源)引脚单独加电时,产生的热点形貌(表现为基板走线发热)与整机上电时的热点形貌不一致。

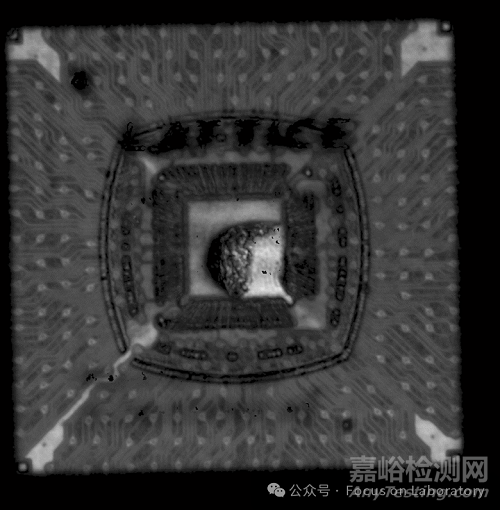

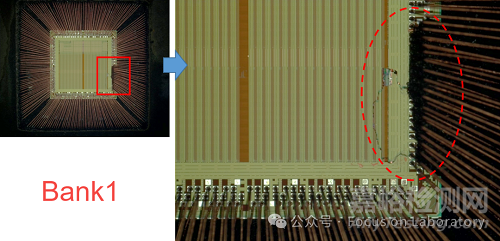

声学扫描 (CSAM):对故障芯片进行超声扫描检查,发现Bank1 区域存在大面积的分层现象。该分层区域的位置与单体测试和整机测试中观察到的异常热点位置高度匹配。

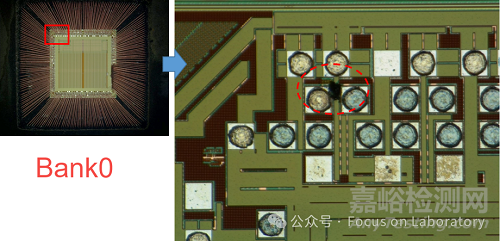

开盖与内部检查:对芯片进行化学开盖后实施内部目检。观察发现,在Bank0 和 Bank1 区域(即对应 VCCIO0 和 VCCIO1 的 I/O 区域)的热点位置,存在明显的电性过应力烧毁形貌(如熔融、碳化等)。这些物理损伤的位置精确对应于之前热点定位和声扫发现的异常区域。

结论与建议:

综合分析确认,CPLD 芯片的 Bank0 和 Bank1 I/O 区域发生了严重的过电击穿,导致VCCIO0、VCCIO1 及核心 VCC 对地短路。

由于烧毁区域损毁严重,仅凭现有形貌无法明确判断击穿的根本诱因是源于 VCCIO 电源网络本身的问题,还是由连接至 Bank0/Bank1 的某个 I/O 端口引入的异常信号/电压所致。

注:本案分析只定位到故障现象,因为是零星问题,故没有进一步深入分析找根因。

如需进一步精确定位根因: 建议针对 Bank0 区域的失效相关管脚进行 P-lapping(精密剖面研磨) 分析。通过此方法可以精确暴露并确定具体失效管脚的定义,进而追踪其连接线路,为最终查明失效的根本原因(如外部过压注入、ESD 事件、内部缺陷等)提供关键证据。

来源:Internet