嘉峪检测网 2025-08-17 19:32

导读:硅通孔(TSV)与玻璃通孔(TGV)介绍。

TSV TGV

——从“把芯片叠起来”到“把玻璃变成芯片高速公路”

“如果把摩尔定律比作一条越走越窄的高速公路,TSV 和 TGV 就是正在修建的立体高架桥。”

——IMEC 3D 集成项目总监 Eric Beyne,2024 IEEE ECTC

一、为什么今天的芯片“必须”打洞?

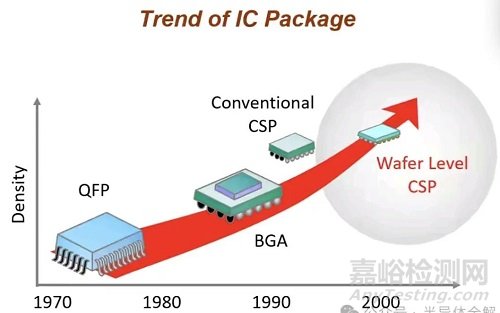

1. 算力需求爆炸

• 训练 GPT-4 的 1.8 T 参数模型需要 25 万颗 A100 并行,功耗 50 MW——传统 2D 封装已无法承受 I/O 数量与互连长度的指数级增长。

2. 物理极限逼近

• 5 nm 以下节点继续微缩,晶体管成本不降反升,3D 集成成为“More than Moore”的核心赛道。

3. 先进封装成为第二摩尔定律

• Yole 2024 报告显示,3D 封装市场 CAGR 18%,2028 年将达 290 亿美元,其中 TSV & TGV 占 42% 价值量。

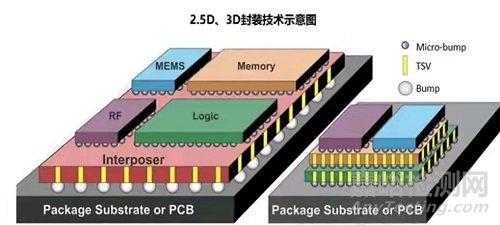

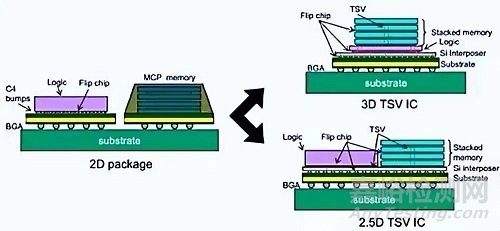

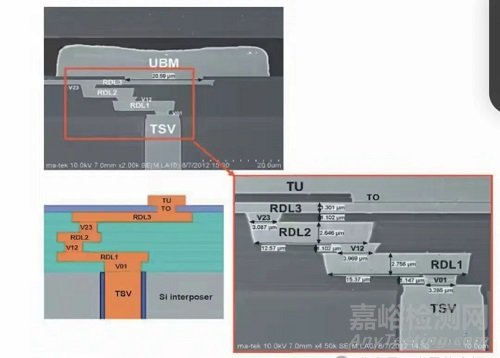

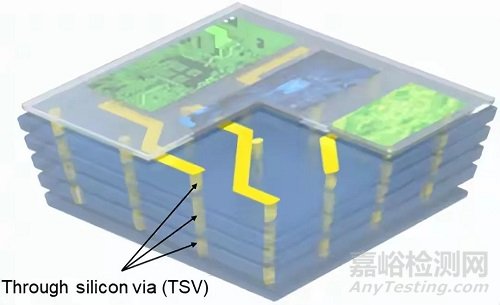

二、TSV:硅片里的“垂直地铁”

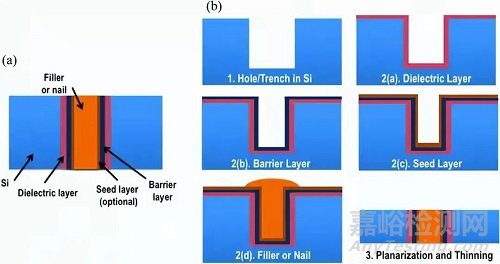

2.1 结构剖面

• 典型尺寸:孔径 5–20 µm,深度 50–200 µm,深宽比 10:1–20:1

• 四层三明治:SiO₂ 绝缘层 → Ti/Ta 阻挡层 → Cu 种子层 → Cu 填充柱

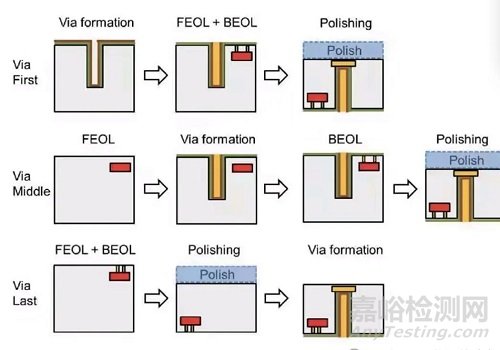

2.2 三种工艺流“谁先用刀打孔”

• Via-First:FEOL 前打洞,可高温退火,成本低,但限制后续晶体管工艺。

• Via-Middle:晶体管完成后、BEOL 之前,平衡热预算与对准精度,主流用于 HBM

• Via-Last:BEOL 后打洞,兼容最成熟节点,但深孔刻蚀难度最大,CoWoS-S 采用。

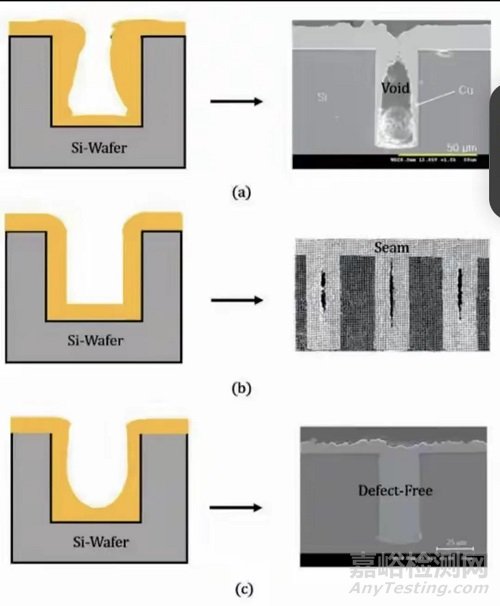

2.3 金属填充的四重奏

• Sub-conformal:空洞多,早期研究品。

• Conformal:留一条中心缝,主流量产。

• Super-conformal:无缝,但电镀液添加剂昂贵,用于高频射频器件。

• Bottom-up:完全无空洞,电镀时间缩短 30%,台积电 SoIC 已导入。

2.4 可靠性“三座大山”(质量风险)

• Cu-Si CTE 差异 16.5 → 2.6 ppm/℃ → 热循环 1000× 后微裂

• 应力诱发载流子迁移 (SM)——斯坦福大学 2023 发现 200 ℃ 下 MTTF 下降 3×

• 漏电路径:SiO₂ 击穿 < 4 MV/cm 时,tdDB 模型预测 10 年寿命需厚度 ≥ 0.5 µm

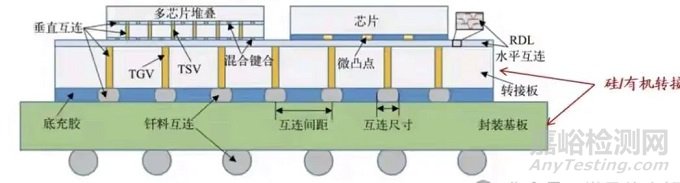

三、TGV:玻璃基板上的“光之桥”

3.1 材料优势

• 电阻率 10¹⁴ Ω·cm,比 Si 高 8 个数量级,RF 损耗 < 0.1 dB/mm@60 GHz

• CTE 3.3 ppm/℃,与 Cu 差距缩小 5×,减少热应力

• 透明性 → 激光一次性钻孔 1000 孔,产能提升 10×(LPKF Vitrion 5000 数据)

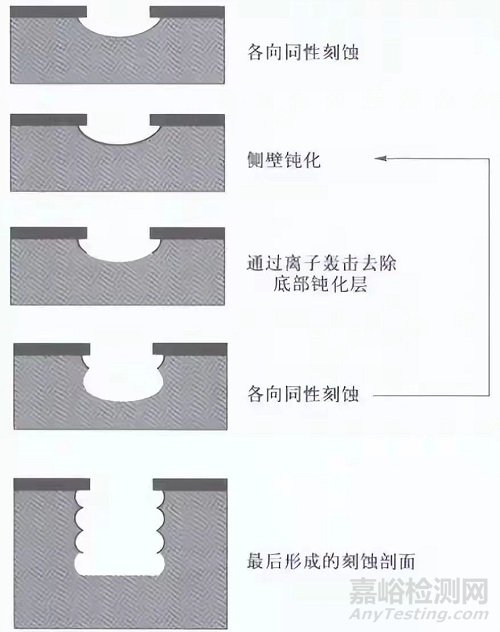

3.2 Bosch工艺

Bosch工艺,也称为交替侧壁钝化深层硅蚀刻工艺,是一种用于制造高深宽比微结构的先进技术,广泛应用于微机电系统(MEMS)和深硅刻蚀领域。Bosch工艺的影响可以从多个方面进行考虑:

3.3 应用落地

• 高通 2024 发布的 Snapdragon X Elite RF 模组:TGV 玻璃转接板集成 IPD 滤波器,厚度减 30%,插损降 1.2 dB。

• 三星电机 2025 路线图中,TGV 用于 RDL-Interposer,替代 CoWoS-R 的昂贵硅中介层,目标成本下降 40%。

四、TSV vs TGV:一张图看懂选择逻辑

• 当信号 > 40 Gbps、功耗 > 200 W:优先 TSV,热膨胀匹配 + 细间距。

• 当频率 > 60 GHz、成本敏感:优先 TGV,低损耗 + 大尺寸玻璃。

• 两者混合:AMD MI300 采用 TSV 堆叠 HBM + TGV 玻璃桥接 I/O,整体封装厚度从 2.5 mm 降到 1.7 mm。

五、质量与可靠性的“暗礁”

5.1 TSV 典型失效模式

• 微裂检测:IR-LST(红外光致发光)扫描,可发现 < 5 µm 裂纹,D0 提升 15%。

• Cu pumping:热循环后 Cu 柱凸出 0.5–1 µm,导致 RDL 剥离——采用 TaN 扩散阻挡层 + 低应力 Cu 电镀添加剂,失效概率降低 80%。

5.2 TGV 特有挑战

• 激光热损伤:孔壁出现 2–3 µm 重铸层,介电强度降低 20%,需 CO₂ 激光 + 湿法蚀刻复合工艺。

• 玻璃-金属结合力:PI 增粘层 + Ar 等离子体处理,剥离强度从 0.3 N/cm 提升到 1.2 N/cm(Fraunhofer IZM 2024 数据)。

六、未来展望:硅-玻璃共封装

1. 0.5 µm Pitch TSV:IMEC 已演示 0.5 µm 直径、深宽比 25:1 的“TSV-last”工艺,预计 2027 年用于 3 nm + 3D V-Cache。

2. TGV 光电共封装:Intel 2025 计划用 TGV 玻璃做 CPO(Co-packaged Optics)基板,单通道 200 Gbps,功耗 < 5 pJ/bit。

3. 可持续制造:玻璃可循环熔化 5 次,碳足迹比硅低 35%,符合欧盟 2030 半导体绿色制造路线。

结语

从“在硅片上挖深井”到“在玻璃上雕光路”,TSV 与 TGV 代表了半导体产业向第三维度的集体迁徙。它们不仅是先进封装的基石,更是 AI 算力持续指数级增长的物理前提。下一次,当你看到 H100 的 80 GB HBM3 以 3.2 TB/s 吞吐时,别忘了——那其实是成千上万根“硅铜地铁”与“玻璃光桥”在并肩工作。

参考文献

[1] Yole Développement, 3D & Advanced Packaging Technology Market Monitor, 2024.

[2] IEEE ECTC 2024 Keynote, “Scaling 3D Integration beyond 1 µm Pitch”.

[3] IMEC, “Reliability of Cu TSV in 3 nm Technology Node”, 2023.

[4] Intel, “Co-Packaged Optics with TGV Glass Substrate”, OFC 2025.

来源:芯芯有我