想象一下,芯片内部有一个隐秘的“自杀开关”。一旦被意外触发,它就会强制芯片内部形成一条低阻通路,相当于在电源(VDD)和地(GND)之间直接“短路”。巨大的电流将汹涌流过这条通路,远远超过芯片设计所能承受的负载。这就是闩锁效应(Latch-up),一旦启动,就会造成:

- 电流激增: 流经芯片的电流瞬间飙升。

- 电压崩溃:芯片的电源电压因巨大电流被拉低。

- 功能瘫痪:芯片完全失去正常工作能力。

- 热失控:巨大电流产生的热量可能导致芯片内部局部甚至整体熔化烧毁。

本质:闩锁效应是CMOS结构内部寄生可控硅(Parasitic Silicon Controlled Rectifier, SCR)被意外触发导通的结果。这是CMOS工艺(将NMOS和PMOS晶体管做在同一芯片上)天生的结构所带来的不可避免的“副作用”。

二、闩锁效应的失效机理

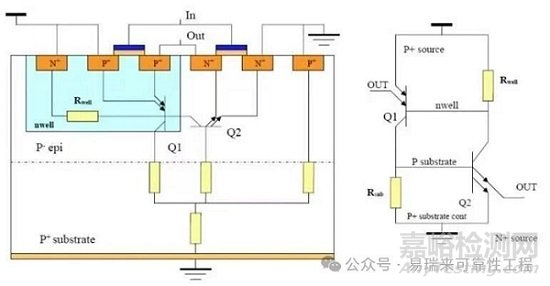

让我们从CMOS器件的微观层面深入理解这个“幽灵开关”。在一个典型的CMOS反相器结构旁边,存在着由寄生晶体管和寄生电阻构成的隐藏结构,它们共同组成了一个

寄生的可控硅器件(SCR)

寄生四层结构(PNPN):CMOS工艺在硅衬底上形成N阱(N-well)和P衬底(P-substrate)。这自然地形成了一个由P+源漏区(在N-well中)、N-well、P-substrate、N+源漏区(在P-substrate中)串联而成的PNPN四层结构(如下图)。这正是SCR的典型结构。

寄生双极管:在这个PNPN结构中,隐含了两个双极晶体管:纵向PNP管 (Q1); 横向NPN管 (Q2)

寄生电阻:N-well本身具有一定的电阻(Rnwell),P-substrate本身也具有一定的电阻(Rpsub)

触发过程:

1)干扰出现:一个来自外部的“刺激”(干扰)出现。例如:

• 输入端或输出端受到一个超出电源轨的电压过冲(EOS)或静电放电(ESD)。

• 电源电压发生快速瞬变(dI/dt或dU/dt过大)。

• 芯片暴露在辐射环境(如宇宙射线)下产生大量载流子。

• 高温环境降低寄生晶体管的开启阈值。

2)基极启动:这个干扰(如注入电流)使得Q1或Q2的基极-发射极结被正向偏置,或者直接注入足够的少数载流子进入基区(衬底或N阱)。

3)正反馈形成:一旦其中一个寄生晶体管(比如Q2)开始导通,它的集电极电流会增加。这个电流流过对应的寄生电阻(Rnwell),产生压降。这个压降会正向偏置另一个寄生晶体管(Q1)的发射结,导致Q1导通。Q1导通后,其集电极电流流过Rpsub,产生的压降又加强了Q2的导通。这个过程互为因果,迅速放大。

4)闩锁形成: 在极短时间内,正反馈使得两个寄生晶体管都进入深度饱和导通状态。此时,电源VDD通过P+区->PMOS的寄生路径(主要是Q1)->衬底->Q2->N+区到达地GND,形成一条非常低阻的通路。巨大电流开始流通。

5)状态维持:一旦进入这个导通状态,整个寄生SCR可以自我维持导通,即使触发源已经消失。此时唯一的停止方法是切断电源(断电重启)。如果电流过大或持续时间过长,芯片就将因过热而永久损坏。

总结关键点:

- 元凶是CMOS工艺固有的寄生PNPN结构(SCR)。

- 触发需要外部刺激来开启其中一个寄生双极管。

- 致命的正反馈回路导致电流雪崩式增长。

- 一旦建立,自维持且只能断电解除。

三、器件闩锁效应的内因

虽然闩锁由外部刺激触发,但CMOS器件本身的结构和材料特性决定了其固有的闩锁敏感性(Latch-up Immunity/Susceptibility)。主要内部因素包括:

晶圆衬底电阻率(P-sub Resistivity)

P型衬底的电阻率越高,其寄生电阻Rpsub越大。这意味着同样的触发电流流过它时,产生的压降更大,更容易使横向NPN管(Q2)的基极-发射结正偏导通。因此,高阻衬底会显著降低CMOS器件的闩锁耐受能力。

N阱电阻率 (N-well Resistivity)

与高阻衬底类似,N阱的电阻率越高,Rnwell越大,同样的阱电流产生的压降越大,更容易使纵向PNP管(Q1)的发射结正偏导通。高阻N阱也不利于闩锁防护。

N阱深度 (N-well Depth) & P+到阱边缘距离

P+扩散区(PMOS源漏)离N阱边缘越近,纵向PNP管(Q1)的基区(N阱)宽度就越窄。对于双极管,基区越窄其电流增益(β)通常越高。β值越高,维持闩锁所需的电流越小,正反馈越容易形成和维持,器件抗闩锁能力越差。

N+到衬底接触距离 (N+ to Sub Contact Spacing)

N+扩散区(NMOS源漏)到最近的P+衬底接触孔的距离越远,则衬底电流流回地的路径上,寄生电阻Rpsub的有效值越大。这使得衬底上更容易积累电位差,导致横向NPN管(Q2)的基极-发射结正偏,抗闩锁能力下降。

器件版图布局的紧凑程度

随着工艺尺寸不断缩小(摩尔定律),NMOS和PMOS管之间的距离越来越近。这相当于缩短了寄生SCR内部各区域的物理距离。其后果是:

寄生双极管的基区宽度(WB)变窄 → 电流增益β增大→ 更容易发生闩锁。

衬底或阱内电流流向接触孔的路径电阻增大 → Rpsub/Rnwell增大→ 触发电压/电流降低 → 更容易被触发。

因此,工艺节点越先进(尺寸越小),芯片本身固有的闩锁风险相对越高,对设计防护的要求也越严格。

制造工艺波动(Process Variation)

掺杂浓度不均匀、结深偏差、接触孔质量等工艺波动,会影响寄生电阻和晶体管增益,导致不同批次甚至同一芯片上不同区域的闩锁阈值存在差异,增加预测和控制的难度。

四、如何抑制闩锁效应

从CMOS器件内因出发如何提升其抗闩锁能力呢?这就需要从芯片的设计、制造工艺、测试等多个环节协同发力。

1)芯片设计层面(Design Level)

增加阱和衬底接触(Guard Rings):这是最核心的设计手段。

环绕式接触:在关键电路(如I/O驱动器)周围的N阱和P衬底中,密集布置大量的接触孔(Contact)。N阱接触孔连接到VDD(通常通过低阻金属线),P衬底接触孔连接到GND。

作用原理:大大降低Rnwell和Rpsub的阻值。当有触发电流试图在衬底或阱中形成正偏压时,就近的接触孔能迅速吸收这些电荷(通过VDD或GND泄放),有效压低寄生晶体管基极的电位,阻止其开启或削弱正反馈强度。这就像在火药桶周围设置了高效的泄洪渠。

采用保护环结构(Double Guard Rings):

针对高风险区域,采用N+/P+双环结构,进一步提升电荷抽取能力。

加大关键间距:

• 增加PMOS P+ 到 N阱边缘的距离:加大Q1的基区宽度,降低其β值。

• 减小NMOS N+ 到 P+衬底接触的距离:减小Rpsub。

• 确保N阱接触靠近PMOS器件:减小Rnwell

优化电源/地网络:

使用宽金属线、多层金属布线、足够的通孔,确保电源和地网络的阻抗极低,有助于全局电荷泄放。

使用SOI (Silicon-On-Insulator) :

SOI晶圆在顶层硅和衬底之间有一层埋氧绝缘层(BOX)。这层绝缘层彻底物理隔离了NMOS和PMOS器件,从根本上消除了寄生PNPN结构的存在。因此,SOI工艺具有超强(甚至免疫)的闩锁抗性,但成本相对较高。

布局隔离 (Layout Isolation):将易触发部分(如大型I/O缓冲器)与高敏感核心逻辑区用保护环或隔离区物理分开。

2)制造工艺层面(Process Level)

降低衬底/阱电阻率 (Low Substrate/N-well Resistivity):

通过精确控制掺杂浓度,使用略低阻值的衬底材料,或在阱下增加埋层(Buried Layer)形成低阻通路(需要特殊工艺如BiCMOS),减小RRpsub和Rnwell。

增加阱深度与结深:

在可行范围内,增加N阱深度和P+结深,加宽Q1的基区,降低其β值。但这可能与先进工艺的微缩化趋势冲突。

优化注入及退火工艺:确保掺杂分布均匀、结轮廓陡峭,控制好寄生参数。

3)测试与筛选层面(Test & Screening Level)

闩锁触发测试(Latch-up Test):通常在晶圆级或封装级进行。依据JEDEC (JESD78) 等标准,对芯片施加特定的电压/电流应力,如:

• I-test: 向引脚注入电流(±100mA)同时抬升/降低电源电压(如VDD+25%/-25%)。

• VDD overvoltage test: 施加过高的电源电压。

测试过程中严密监测电源电流。如果电流持续异常增大(超过指定阈值或无法恢复),则判定样品发生闩锁,该批次可能存在设计或工艺问题。

筛选标准:测试条件需覆盖芯片规格书规定的应用范围(电压、温度)。只有通过严格闩锁测试的芯片,才被认定为可靠。

五、如何避免应用CMOS器件时的闩锁效应

对于负责器件选型和系统设计的工程师来说,需要从“外部应用”角度来规避闩锁风险:

1)器件选型:

核心指标:确认其闩锁特性。理想的情况是明确标注符合JESD78标准(例如,注明通过了Class I, II等级别的测试,通常Class I/II要求更严格),并提供最小触发电流ITRIG和最大维持电流IHOLD(参数值越大越好)。

安全选择:对于高可靠性应用(如工业控制、汽车电子、医疗设备),优先选择明确标注“Latch-up immune per JESD78 Class X”或“SOI工艺”的器件。

警惕:如果数据手册中关于闩锁的信息模糊不清或缺失,务必向供应商(FAE)确认。规避风险不明的器件。

2)系统应用设计注意事项:

“数据手册是圣经”:务必严格遵守数据手册推荐的:

- 最大工作电压/瞬时电压上限:任何引脚上的电压不要超过其规定的绝对最大值(通常VSS-0.3V ~ VDD+0.3V是一个常见边界,需仔细核对)。超压是强触发源!

- 电源电压范围:保证应用电压(VCC/VDD/Vin等)在允许范围内,避免过压或欠压。

- 最大输入/输出电流: 避免驱动能力超限导致内部结过载

。

- 工作温度范围:避免器件在超温下运行。

采用推荐/必需的防护电路:

- 系统限流:在外部电源和芯片之间加入熔断保险丝(Fuse)或可复位保险丝(PTC)。一旦发生闩锁导致电流剧增,保险丝会及时熔断或阻值剧增,切断电源通路,保护芯片不被烧毁。

- 芯片电源:尤其对于从外部取电或易受干扰的接口板,在靠近芯片电源引脚处并联去耦电容(滤除高频噪声)和TVS管(吸收大浪涌)。遵循“入口处防护”原则。

- 电源稳定性:保证系统电源稳定、纹波小,避免剧烈的上电/掉电速率(dV/dt)。必要时为敏感芯片配置独立的LDO稳压器。

- 接地良好: 确保整个系统的接地网络阻抗低且设计良好,设计短而粗的地线(减小阻抗),单点接地或采用星型接地策略以降低回流路径阻抗差异,避免因地弹(Ground Bounce)等问题引入潜在触发。

- 输入端:必要时在可能引入干扰的信号线(如长线接口、按键、与继电器或电机接口处)串入限流电阻或在信号线对地加钳位二极管。

- 上电/掉电顺序:复杂的多电源系统中,不同电源轨的上电/掉电顺序可能引起闩锁。如果器件手册有要求,使用电源管理IC或时序控制电路保证符合顺序。

- 热插拔设计:除非芯片明确支持(有内部保护),否则尽量避免对带电插拔部件(如接口卡、模块)在系统运行中进行插拔操作。

- 热管理:避免芯片长期工作在高温环境,因为高温会降低寄生管的触发阈值,更容易发生闩锁。良好的散热设计和温度监控是必要的。

ESD防护不容忽视:

良好的ESD防护不仅保护端口,也降低了触发闩锁的风险。确保生产、组装、维修过程中人员接地及设备符合ESD安全规范。关键外接端口应有ESD保护器件。

仿真分析: 如果条件允许,使用EDA工具对关键信号路径的完整性(信号噪声、振铃)和电源分布网络(阻抗、噪声)进行仿真,识别潜在的电压过冲风险点。

六、结语

闩锁效应是CMOS技术发展道路上必须跨越的一道屏障。通过深入理解其内部寄生SCR机制,利用先进的设计规则、工艺改进、严格的测试筛选,以及在系统应用层面(限流、浪涌保护、热管理)的综合防护措施,现代半导体工业已能极大地驯服这个“开关幽灵”。对于工程师而言,选择符合可靠标准的器件,并严格遵循设计规范和应用限制,是保障电子系统长期稳定运行的基石。

来源:易瑞来可靠性工程

关键词:

闩锁效应

失效分析

![Wang: [图片] Wang: CMOS闩锁效应及失效分析](/uploads/ad/weixin20151213185125.png )