嘉峪检测网 2025-03-09 09:45

导读:相信搞硬件的兄弟一般都见过芯片电源引脚一般会放一个电容,为社么这个电容一般是100nF呢?

1.前言

相信搞硬件的兄弟一般都见过芯片电源引脚一般会放一个电容,而且这个电容一般是100nF,而且芯片电源引脚旁的电容内一般还叫做去耦电容也就是Decoupling Capacitor,这事儿在设计里太常见了,但是为啥老选100nF呢,是拍脑袋拍出来的?还是30年经验的老师傅传承下来的?其实这事还真不是随便拍脑袋决定出来的。这背后有物理原理、工程经验和实际场景的综合考量。今天我们就掰开揉碎讲讲,尽量说得明白点。

2.去耦电容是干啥的?

咱们先说清楚去耦电容的工作到底是个啥?芯片比如MCU、FPGA啥的工作时,内部晶体管不停开关,每次开关都得从电源往外拉出来电流。这电流可不是慢慢来的,而是跳得特别快,像一阵阵“脉冲”。但是电源线和PCB走线又都有寄生电感,所以反应没那么快,电压就容易抖一下,这就是“电源噪声”。去耦电容就相当于个小“水库”,紧挨着芯片放着,瞬态电流不够时它赶紧补上,让电压稳住,顺便把高频噪声压下去。

3.为啥选100nF?

选100nF可不是玄学,100nF这值在大多数场景下都“刚刚好”。为什么这么说呢?我从几个角度给你讲讲原因:

1. 频率响应够用

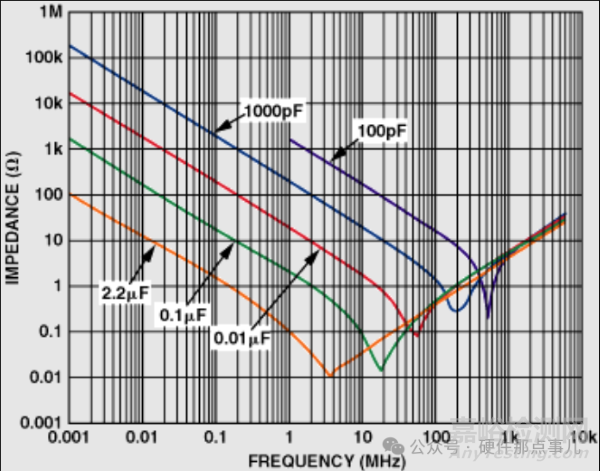

一般来说芯片开关产生的噪声频率一般在几十MHz到几百MHz之间,这个跟芯片实际的时钟频率和开关速度有关。这意味着去耦电容得能快速响应这个范围的波动。而电容的阻抗(Zc = 1/(2πfC))跟频率f和容量C反着走。频率高时,电容阻抗低,能吸高频噪声;频率低时,阻抗高,作用就弱了。

而一般100nF电容的表现可谓是恰到好处:

在10MHz时,100nF的阻抗大概是0.16Ω,够低,能吸掉大部分噪声。

到100MHz时,阻抗降到0.016Ω,更好使。

再高点(比如1GHz),寄生电感开始捣乱,但这频率已经超出很多芯片的主要噪声范围了。

相比而言10nF电容在100MHz时阻抗0.16Ω,还行,但在10MHz时就1.6Ω,有点不够用。而1μF电容在10MHz时阻抗0.016Ω,很好,但低频时太强,高频时封装寄生电感又拖后腿。所以咱们就能得出来一个结论:100nF的频率覆盖正好卡在大多数数字芯片的噪声“甜点区”。

2. 反应速度合适

电容容量越大,存的电荷多,但充放电速度慢;容量小,反应快,但存电不够。100nF的优势就是它能存够芯片一次开关需要的电荷,通常是pC到nC级别,当然这实际上要视芯片电流而定。同时,100nF的充放电时间常数(RC)很短,能跟得上几十MHz的瞬态跳变。

咱们可以举个例子:假设一个芯片内部晶体管开关电流峰值10mA,持续10ns,所需电荷Q=I×t=10mA×10ns=100pC。100nF在5V下存电Q = C×V=100nF×5V=500nC,绰绰有余,还能快速释放。

3. 寄生效应可控

电容不是理想元件,实际有寄生电感ESL和电阻ESR,封装越大,比如1206对比0402,寄生电感越高,高频下效果越差。100nF的电容常用0402或0603封装,寄生电感低,一般0.5nH左右。自谐振频率SRF(电容和寄生电感共振的点)在几十MHz到100MHz左右,正好覆盖芯片噪声范围。

相比之下1μF的SRF可能掉到10MHz以下,高频就不灵了。10nF的SRF很高(上百MHz),但容量小,低频补电不够。所以100nF电容在容量和寄生效应间平衡得不错。

4. 习惯使然

还有很重要的一点是100nF不是理论算出来的“完美值”,而是多年设计里大家试出来的“万金油”。芯片厂商像TI、ST、NXP啥的在数据手册里老推荐0.1μF,搞得这值成了行规。并且电容厂家供应链也配合,100nF便宜好买,封装齐全,谁也不想费劲去改。

4.总结

当然100nF不是万能钥匙,有些场景得换思路,比如超高频(GHz级),100nF的寄生电感在1GHz以上拖后腿,阻抗上升。这时候就需要10nF甚至1nF,小容量电容SRF更高,配合紧贴芯片布局,或者组合使用应对大电流瞬态,1μF或10μF,跟100nF并联,大的管低频补电,小的管高频滤波。1μF加0.1μF组合,稳得一批。如果以低频噪声为主,100nF对kHz级噪声阻抗太高,滤不干净。组合使用10μF甚至100μF,容量大,低频效果好。

100nF能当去耦电容的“标配”,不是因为它完美,而是因为它够“中庸”。频率响应、反应速度、寄生效应和工程习惯凑一块儿,造就了它的地位。但设计时别死脑筋,具体芯片的噪声频率、电流需求不一样,得多试试。我干活时,示波器一测,哪个值稳就用哪个,数据说话比啥都强。

来源:硬件那点事儿

关键词: 芯片