嘉峪检测网 2025-03-14 08:51

导读:各位芯片行业的朋友们,今天,我想结合相关资料和最新研究,和大家聊聊FinFET技术中常见的失效分析(FA)问题、可靠性问题以及相应的定位方法。

各位芯片行业的朋友们,今天,我想结合相关资料和最新研究,和大家聊聊FinFET技术中常见的失效分析(FA)问题、可靠性问题以及相应的定位方法。

一、FinFET简介

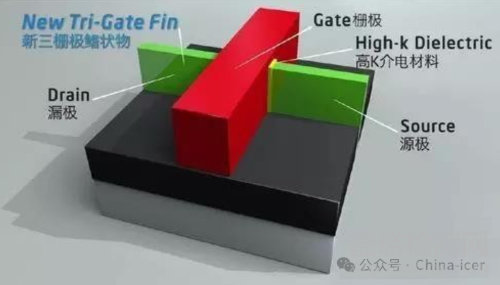

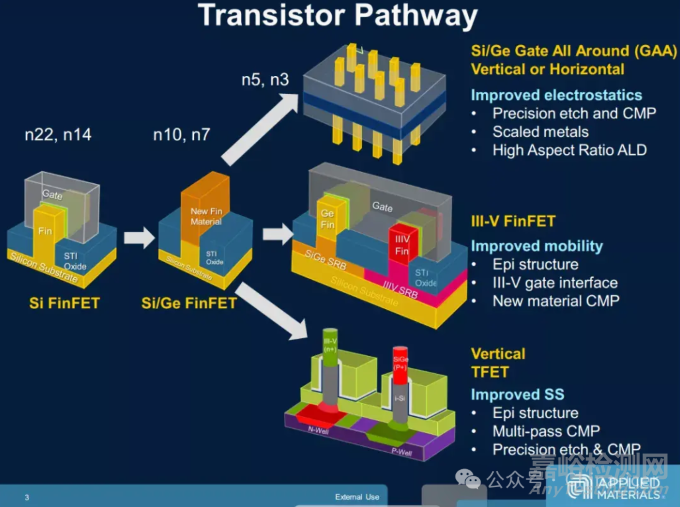

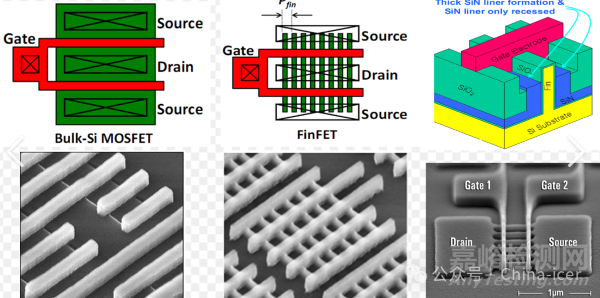

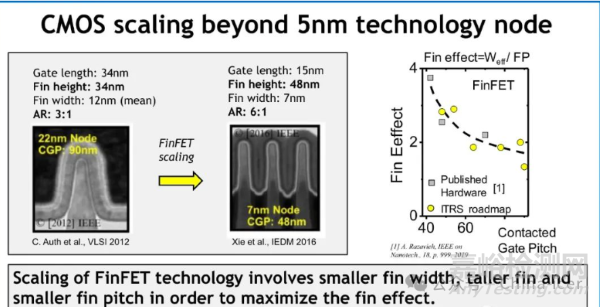

FinFET(鳍式场效应晶体管)是一种新型的Transistor结构,它通过在传统planner 结构上引入3D Fin结构,大大提高了Transistor的性能和集成度,在现代芯片制造中得到了广泛应用。然而,随着工艺节点的不断缩小,FinFET也面临着一系列的FA和可靠性挑战。

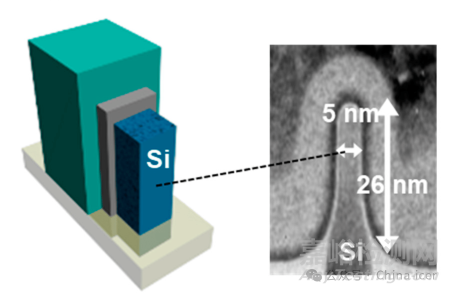

很多人后台私信我,哪里是Fin Width和Fin Hight,这里放张图,解释一下

FinFET/Planar工艺对比表

|

Loop |

Planar |

FinFET |

|

AA |

Single pattern STI |

SADP,Fin etch,Cut,SDB |

|

Poly Gate |

P1+P2 |

Poly CMP+ Line+Cut |

|

EPI |

SiGe/SiC |

SiP/SiGe/low-K spacer |

|

RMG |

Single pattern |

Single pattern+self-align contact |

|

MEOL |

Single pattern |

M0 AA/M0 Gate/Cut block |

|

Metal |

Single pattern |

LELE |

二、常见的FinFET FA问题

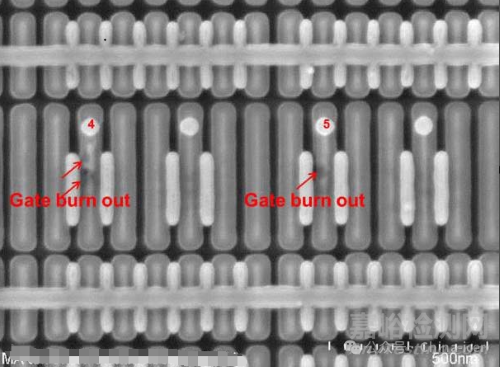

(一)Gate related issue

As we all known,Gox Integrity 是一个Key issue。Gox过薄可能会导致Leakage current增加,影响T的开关性能。此外,Gate material与Fin之间的界面质量也会影响器件的性能,如 interface states密度过高会导致载流子 μ 迁移率下降。

(二)Fin related issue

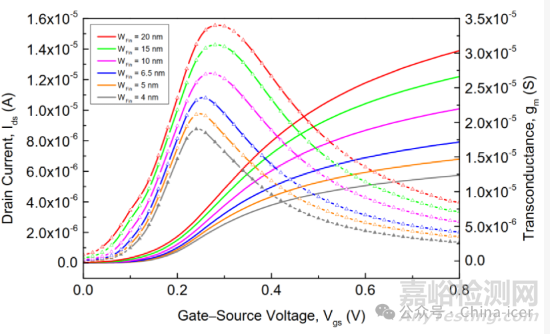

Fin size和形状对FinFET的性能有重要影响。Fin height ,Fin width non - uniform会导致device parameters的non - uniform,进而影响芯片的整体性能。另外,Fin surface的粗糙度也会影响carrier的传输,增加电阻。

(三)SD related issue

SD的掺杂浓度和分布不均匀会导致Transistor 的阈值电压漂移,影响器件的稳定性。同时,SD与Fin之间的接触电阻过大也会降低器件的性能。

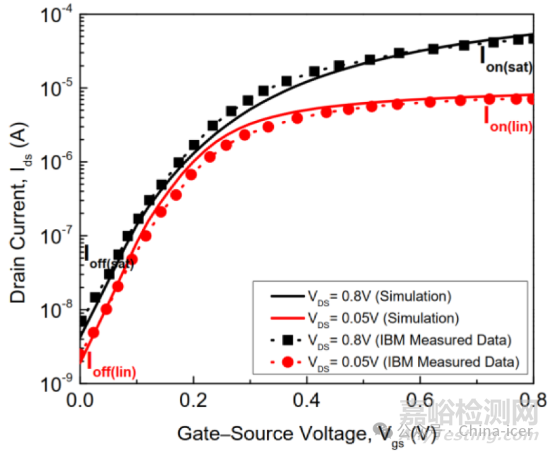

Simulation and experimental I–V curves of the investigated FinFET model

三、常见的FinFET Rel Issue

FinFET 可靠性问题是复杂的二维问题, 可靠性问题类似,

(一)HCI

HCI是FinFET中常见的可靠性问题之一。在高电场作用下,Carrier获得足够的能量注入到栅极氧化层中,导致Gox trapped charge增加,从而引起Threshold voltage thift和Gm down,影响device的性能和寿命。

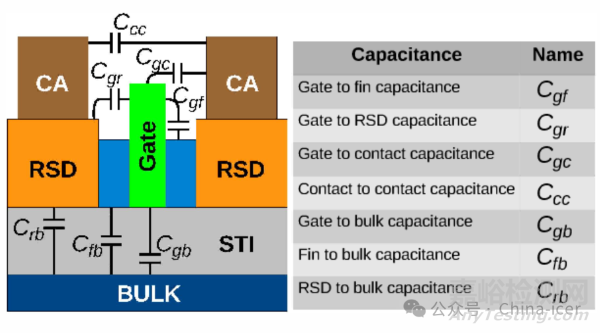

FinFET Parasitic Capacitance Model

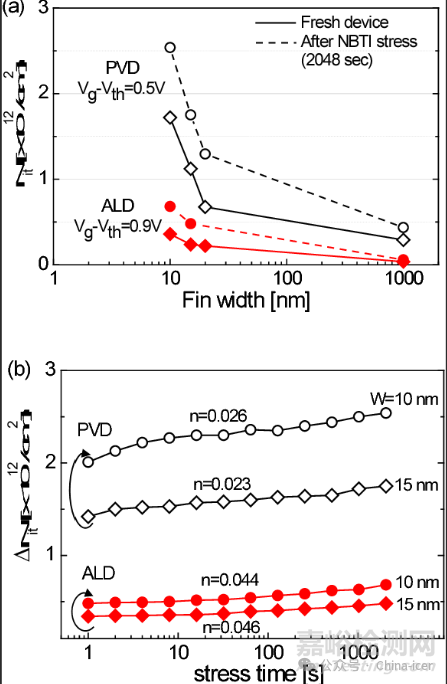

(二)NBTI

NBTI主要发生在P型FinFET中。在负偏压和高温条件下,Gox与Si interf. 处会产生defect,导致Gox drift Positive,降低器件的驱动能力。

(三)EM

随着芯片集成度的提高,金属互连线中的电流密度增大,EM 问题变得更加突出。EM 会导致金属互连线中的原子迁移,形成 Void 或Short,影响芯片的可靠性。

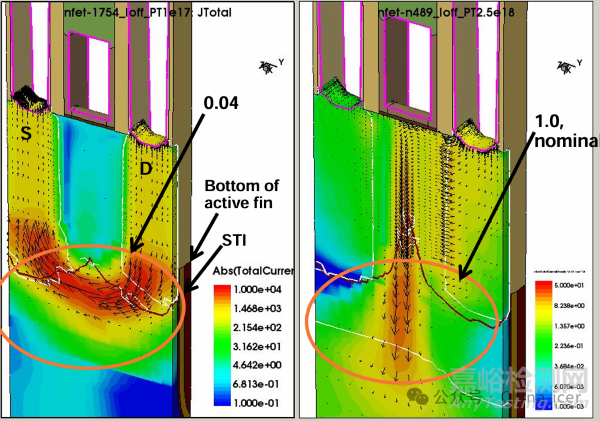

4)known unkonw Issue?

太多,人类已知知<<知道的知识

最典型的我约到 doping导致 leakage,可以仿真无法探测

TCAD plot

再有就是量子力学的问题

四、FinFET问题的定位方法

(一)电性测试定位

通过对芯片进行各种电性测试,如I - V特性测试、C - V特性测试等,可以初步判断问题所在的区域。例如,如果某个Transistor的漏电流异常增大,可能是栅极氧化层存在问题。

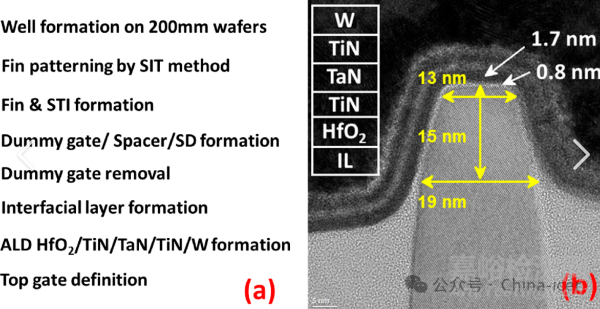

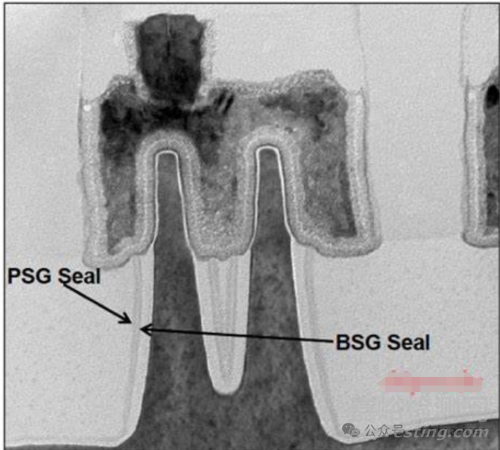

(二)物理分析定位

利用SEM、TEM等设备对芯片进行物理分析,可以直观地观察IC的微观结构和缺陷。例如,通过TEM可以观察到Gate OX的厚度和质量,以及Fin的尺寸和形状。

TEM image

(三)失效分析技术

常用的失效分析技术包括微OBIRCH、Emmi、LCT、Nano-probe、SIL等。这些技术可以检测到芯片中的漏电点和热点,帮助定位失效位置。例如,OBIRCH可以通过检测芯片表面的光反射变化来定位漏电点。

Nanoprobe

因为我的背景是从芯片的质量失效分析可靠性,之后转到了流程质量,过程质量、SQE, TQM, 所有对这个有些涉猎

FinFET的质量控制

会根据 Fin Height variation, Fin width variation

Fin With variation (脱敏版)

以及对测量方法, 质量管控、要求,有专项要求

五、总结

FinFET技术在提高芯片性能和集成度方面具有巨大优势,但也面临着诸多FA和可靠性问题。作为芯片质量管理人员,我们需要深入了解这些问题,了解要求的来源, 并掌握有效的定位方法,以确保芯片的质量和可靠性。希望今天的分享能对大家有所帮助,让我们一起为芯片行业的发展贡献力量!

最近有个别同志举报我违反原创, 导致我被平台警告和屏蔽, 国内最新的材料不多, 发文献前我也比较谨慎, 只能保证不是为盈利为目的为目的的分享。 也希望高抬贵手。

来源:芯芯有我