嘉峪检测网 2025-05-14 17:11

导读:本文介绍了芯片Latch up(闩锁)检测标准与方法。

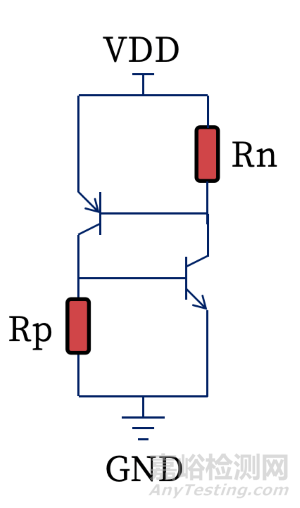

闩锁效应是指在CMOS集成电路中寄生的PNP和NPN双极型晶体管相互影响而产生的一种低阻抗通路,从而产生大电流。由于正反馈作用,该状态会被持续维持(即“闩锁”),从而导致集成电路失效,严重时可能造成器件烧毁。

示意图

等效电路

Latch up标准及测试方法

常见测试标准

JESD78与AEC-Q100-004

测试方法

闩锁测试实际是通过电流脉冲激励于非电源(输入、输出、输入/输出等)管脚或者施加过电压脉冲于电源管脚来评估芯片抗闩锁效应的能力,即过电压测试V-test及过流测试I-test。

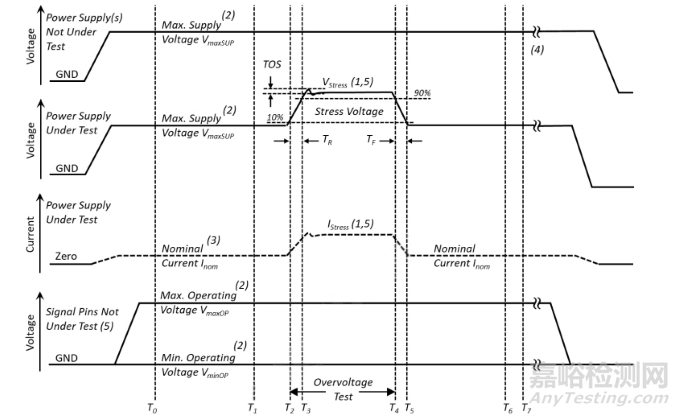

电源过电压测试V-test

所有输出管脚置于悬空状态,输入、输入/输出管脚置于逻辑高电平,预置管脚置于固定状态。量测每个电源管脚电流。

待测电源管脚施加电压触发。

去除触发源对比前后电流变化。

重复2-3测试每一个电源管脚并判断测试结果。

电源测试V-TEST

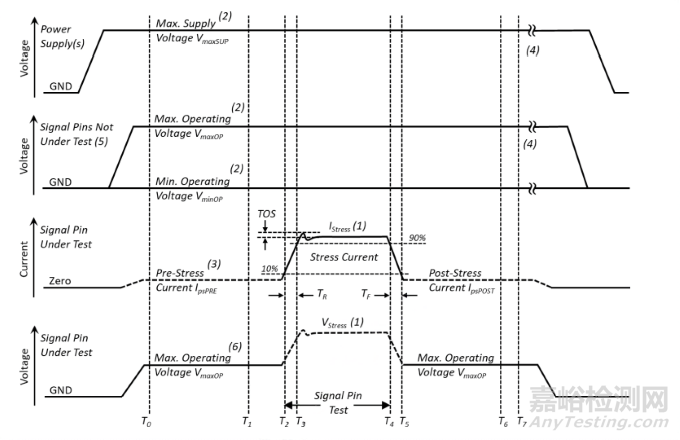

I/O测试I-TEST或E-TEST

所有非待测输出管脚置于悬空状态,输入、输入/输出管脚置于逻辑高电平。预置管脚置于规定的固定状态。

对待测管脚置于逻辑高状态。测量每个电源管脚电流,然后对待测管脚施加正向及负向触发电流或电压。

去除触发源后,将被测管脚恢复到施加触发源之前的状态,测量每个电源管脚电流。

重复2-3测试每一个待测管脚,并判断测试结果。

I/O正向电流测试 I-TEST

判断标准

触发前电流绝对值小于25mA,触发后电流应小于触发前电流加10mA。

触发前电流绝对值大于25mA,触发后电流应小于触发前电流的1.4倍。

另外测试后漏电流过大、IV曲线严重偏移、功能失效等情况,均可判为失效。

测试结果判断

来源:Internet

关键词: 芯片