嘉峪检测网 2025-05-12 15:50

导读:本文将从定义、结构、作用及缺失风险四个维度,全面解析这一芯片 "守护者" 的技术内涵。

在集成电路制造领域,Seal ring 虽不直接参与电路信号处理,却是芯片物理防护体系的核心构件。这个看似简单的环形结构,从版图设计到工艺实现都承载着多重使命,是保障芯片可靠性的关键屏障。本文将从定义、结构、作用及缺失风险四个维度,全面解析这一芯片 "守护者" 的技术内涵。

一、多维视角下的定义阐释

从版图设计(Layout)角度,Seal ring 是由有源区(diff)、过孔(contact)、通孔(via)和金属层(metal)等工艺层次按严格设计规则(Design Rule)叠加而成的闭合图形。这些层次并非简单堆砌,而是遵循各层 "暗 / 明"(dark/clear)属性的匹配原则 —— 只有当设计层与工艺层属性一致时,才会在 Seal ring 中保留该层图形,形成立体防护结构。

从工艺实现角度,Seal ring 呈现为金属层、氧化层、钝化层的复合结构。其本质是在芯片边缘构建一圈 "电子堤坝":底层金属层提供导电通路,氧化层隔离水汽,钝化层抵御机械冲击,三层协同形成多维度防护体系。

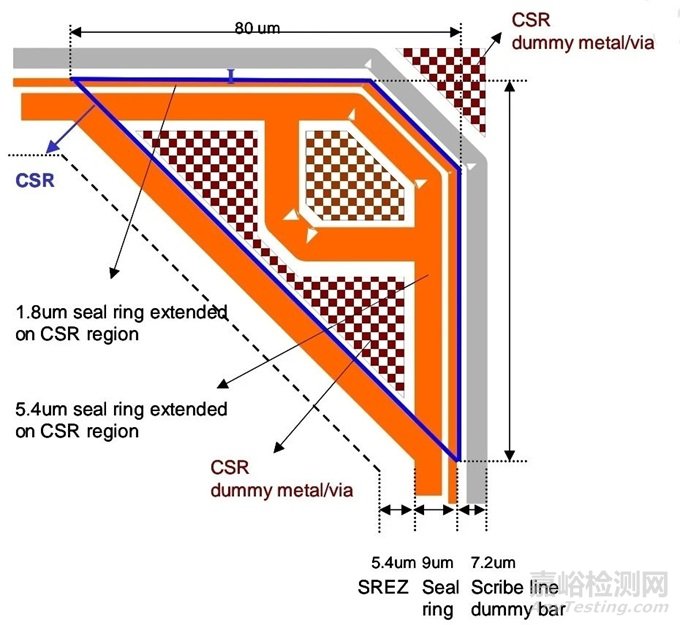

从物理布局角度,Seal ring 位于芯片(Chip)与划片槽(Scribe Line)之间,犹如一道环形缓冲带。其宽度通常遵循 10 微米以上的设计规范,为后续芯片切割预留安全边界,避免切割应力直接作用于核心电路区域。

二、精密构造的层次解析

Seal ring 的核心构造包含四大工艺层次:

有源区(Diffusion):作为底层支撑,通常采用 P + 掺杂形成导电通道,与衬底接地网络连接,为静电释放提供低阻抗路径。靠近 Seal ring 的扩散区需特别设计浅硅化物(Salicide)结构,通过添加 RPO(反刻保护层)或 SAB(硅化阻挡层),增强 ESD 防护能力。

过孔与通孔(Contact/Via):区别于普通电路的离散方孔设计,Seal ring 采用连续长条孔构造,形成 "护城河" 式导电通路。相邻层的孔结构需错位排列,避免垂直方向形成直通通道,这种设计能有效吸收切割过程中产生的水汽,防止内部电路受潮。

金属层(Metal):优先使用上层金属(如 Metal2 及以上)连接核心电路与 Seal ring,避免底层金属(Metal1)因厚度不足导致的机械脆弱性。宽金属连接时,需避免在近环区域开槽,确保护环的结构完整性。

氧化与钝化层:通过热氧化形成致密氧化层隔离水汽,表面覆盖氮化硅或聚酰亚胺等钝化材料,构建机械缓冲层,抵御切割时的机械应力。

三、多重防护的核心作用

(一)机械防护:抵御切割冲击

作为芯片切割的物理缓冲带,Seal ring 承担着 90% 以上的机械应力。划片刀在划片槽(Scribe Line)作业时,振动和摩擦产生的应力通过 Seal ring 的金属 - 氧化层复合结构逐级衰减,避免核心电路因应力集中出现裂痕。特别是芯片四角的强化结构,能有效防止切割偏斜导致的边缘损伤。

(二)环境隔离:阻断水汽入侵

切割过程中产生的微裂纹可能成为水汽渗透通道,Seal ring 的连续长孔结构与多层钝化层形成 "迷宫式" 隔离:金属层导电网络吸收切割产生的游离水,氧化层阻断液态水渗透,钝化层隔绝气态水分子。实测数据显示,带 Seal ring 的芯片在 85℃/85% RH 环境下的失效时间比无环结构延长 3 倍以上。

(三)静电防护:构建泄放网络

切割摩擦产生的静电通过 Seal ring 的 P + 有源区迅速导入接地系统,邻近的环结构形成并联泄放通道,将瞬间电流冲击分摊到整个芯片边缘。这种设计使 ESD 防护能力提升 40%,尤其对高速接口电路的保护效果显著。

(四)电磁屏蔽:隔离外部干扰

通过将 Seal ring 整体接地,形成环绕式电磁屏蔽层,有效衰减外部电磁场对芯片内部的耦合干扰。在射频芯片中,该结构可降低 20dB 以上的寄生耦合噪声,保障高频信号的完整性。

四、缺失 Seal ring 的潜在风险

(一)机械损伤风险加剧

无 Seal ring 的芯片在切割时,机械应力直接作用于 IO 环区域,导致边缘电路断裂的概率增加 60%。某 MCU 芯片案例显示,省略 Seal ring 后,切割良率从 98% 骤降至 82%,主要失效模式为边缘晶体管栅氧破裂。

(二)环境可靠性下降

潮气从切割断面侵入后,会导致金属层电迁移速率加快,尤其在混合信号芯片中,湿气引发的漏电流可使待机功耗升高 30% 以上。存储芯片的位线漏电问题更为严重,无环结构的芯片在潮湿环境下的数据保持时间缩短至标准值的 1/5。

(三)静电防护失效

切割产生的静电无法及时泄放,导致 ESD 事件能量集中于核心电路。某 ADC 芯片实测显示,无 Seal ring 时,±2kV 静电放电即可造成 15% 的通道失效,而标准结构可承受 ±4kV 冲击无损伤。

(四)电磁兼容性恶化

外部电磁干扰直接耦合至边缘电路,导致模拟信号信噪比下降 15dB,数字电路的时钟抖动增加 25%。在车规级芯片中,这种干扰可能引发逻辑误判,威胁系统安全。

(五)工艺兼容性问题

省略 Seal ring 后,划片槽与核心电路距离不足,可能导致切割过程中砂轮碎屑飞溅至芯片表面,造成表层金属短路。某功率芯片案例中,因 Seal ring 缺失引发的短路失效占比达 22%。

结语:平衡设计的重要考量

Seal ring 的设计本质上是可靠性与成本的平衡:尽管增加约 5%-8% 的芯片面积,但能显著提升良率和长期可靠性。随着先进封装技术(如 SiP、2.5D 集成)的发展,Seal ring 的功能正从单一机械防护向多功能复合防护进化,未来可能集成应力传感器、环境监测等智能模块。对于设计者而言,遵循 Foundry 提供的设计规则,合理优化环结构参数,是打造高可靠性芯片的必要前提。在追求极致集成度的同时,切勿忽视这道守护芯片的 "隐形长城"。

来源:国芯制造

关键词: 芯片