嘉峪检测网 2025-05-23 20:59

导读:此次台积电发表了两项研究成果:《采用后端RC优化技术与远端写入辅助方案的3纳米工艺3.6GHz双端口SRAM》、《基于2纳米CMOS纳米片技术的高密度能效SRAM(存储密度达38.1Mb/mm²)。

在今年ISSCC(国际固态电路会议)的全会上,第29分会场主题聚焦SRAM(静态随机存储器),台积电(TSMC)、英特尔(Intel)、联发科(MediaTek)和新思科技(Synopsys)四家公司共发表了五项技术研究成果。

此次台积电发表了两项研究成果:《采用后端RC优化技术与远端写入辅助方案的3纳米工艺3.6GHz双端口SRAM》、《基于2纳米CMOS纳米片技术的高密度能效SRAM(存储密度达38.1Mb/mm²)。

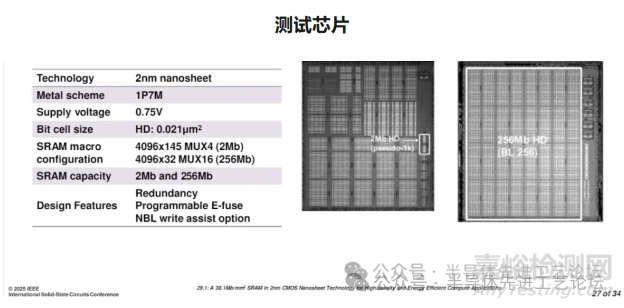

台积电在2nm工艺发文中展示了SRAM测试芯片图像。根据测试芯片缺陷密度分析(数据来源:日本科技媒体ASCII),其良率表现良好,具体数据如下:

左侧为2Mbit SRAM测试芯片,右侧为256Mbit SRAM测试芯片。

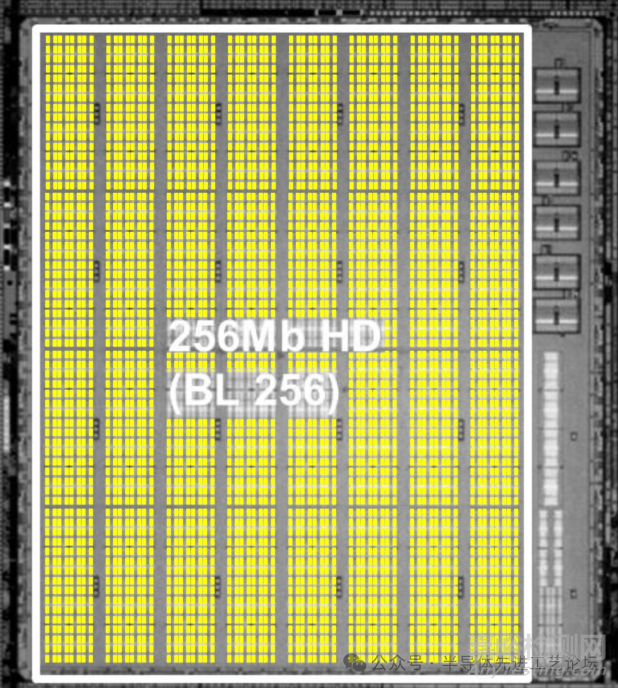

下图是上面测试芯片细节放大视图: 其中黄色标注区域为实际SRAM存储单元部分,未填充颜色的区域则是纵横交错的布线通道。

虽然号称是高密度(HD)设计,但明显可见布线区域占据了相当大的面积。

每个存储单元(Bit cell)的面积为0.021μm²(即1bit SRAM单元的面积),因此集成256Mbit所需的总面积(也就是上图中黄色区域的总和)约为5.673mm²。另一方面,整个测试芯片的尺寸估计为4.24×4.70mm,总面积约为19.95mm²。

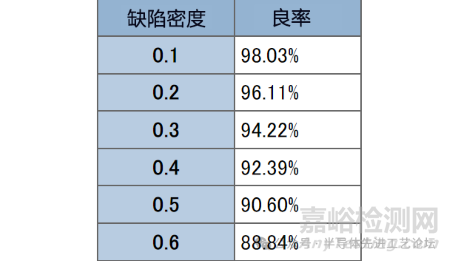

基于这些尺寸参数,我们对缺陷密度进行了估算。使用SemiAnalysis的芯片良率计算器(Die Yield Calculator)进行模拟后,得到如下表所示的结果。

缺陷密度与良率的关系

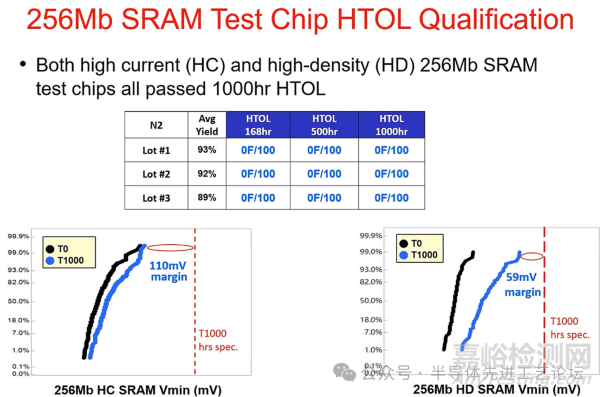

根据下方幻灯片数据,Lot #1至#3三个生产批次的平均良率分别为93%、92%和89%。由此推算:

Lot #1的缺陷密度略低于0.4个/cm²

Lot #2的缺陷密度略高于0.4个/cm²

Lot #3的缺陷密度略低于0.6个/cm²

来源:半导体先进工艺论坛

关键词: 芯片