嘉峪检测网 2025-05-26 08:44

导读:本文介绍了芯片光刻过程中Overlay技术。

随着半导体工艺节点不断向 5nm、3nm 甚至更先进的技术迈进,晶圆上各层图案之间的对准精度(Overlay)成为影响良率和性能的关键因素之一。在多层掩模图案叠加的过程中,任何微小的对准误差都可能导致电路功能失效或性能下降。

半导体器件结构的日益复杂,Overlay 测量工具在精度提升的同时,成功保持了可接受的测量吞吐率,能够在精度与效率之间找到平衡,满足了先进制程的双重需求。在这场不断追求极限精度的竞赛中,先进制程芯片的实芯 Overlay 容差正在迅速收紧。以 3nm 节点(22nm 金属间距)为例,overlay 精度已经进入个位数纳米级别。为了确保 5nm 和 3nm 节点的良率,业界正在采用新的 Overlay 测量目标、机器学习方法及更先进的光学 Overlay 系统,从而加速关键检测流程。

1.Overlay介绍

Overlay 是指两个或多个光刻层之间的图形是否能够精确叠加。每一层的图形必须准确地对准下层结构,否则电路连接将出现错位或断点,导致器件失效。例如,在 3nm 节点,金属线宽可能只有 20nm 左右,而 Overlay 的容差需要控制在 2nm 以内。如此高的对准精度要求,对光刻设备、测量工具和工艺控制提出了极大的挑战。

|

维度 |

对应图中标识 |

说明及影响 |

|

Overlay |

红圈(图层偏移) |

控制图层间的对准精度,避免电连接失败或短路 |

|

CD & Pitch |

绿色标签(结构尺寸) |

决定布线和图案最小尺寸,是评估分辨率和工艺极限的指标 |

|

Focus & Imaging |

绿色箭头 |

保证图案清晰稳定成像,避免曝光模糊和线宽漂移 |

|

Productivity |

蓝色标签(WPH) |

衡量设备效率与吞吐能力,是制造成本控制的重要参数 |

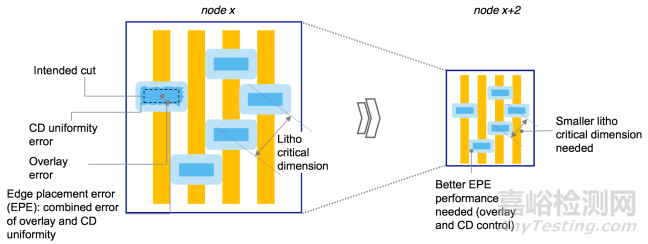

在光刻工艺中,Overlay 精度已成为影响芯片良率的关键限制因素之一。Overlay 控制的核心目标是确保每一层掩膜图形与其下方图形的精准对准,尤其是在像 5nm 这样的先进节点中,Overlay 容差通常是图形尺寸的 30%。因此,这一精度必须严格控制在几纳米之内,以确保良率的提升。

|

工艺节点 |

Overlay控制目标 |

|

28nm |

~5-6nm |

|

14nm |

~4nm |

|

7nm |

~3nm |

|

5nm |

~2.5nm |

|

3nm以下 |

< 2nm |

一个典型的芯片可能包含超过 50 层的掩膜图层,其中部分关键层采用极紫外(EUV, 13.5nm)曝光,而非关键层则使用阿根廷氟(ArF, 193nm)曝光。EUV 扫描设备、检测系统及其背后的算法层面取得的关键技术进展,共同提升了 Overlay 控制能力,从而实现了更高良率的晶圆生产。

Overlay 技术的发展趋势表现在多个方面,主要包括:

1. 使用更长波长的近红外(near IR)对准:这种技术可穿透新型硬掩膜材料,尤其是那些在可见光下不透明的材料,进一步提高测量精度。

2. 设计更符合实际电路结构的 Overlay 测量目标:这一发展有助于提高测量的准确性,尤其是在复杂电路的实际应用中。

3. 提高测量采样密度:增加采样点数,使得数据的覆盖更广泛,从而提升测量的代表性和准确性。

4. 应用机器学习算法:通过更快速的数据处理,优化在线检测结果,减少人工干预和误差。

此外,硬件改进(如吸附盘 chuck 的升级)也在不断优化测量精度,帮助抵消晶圆弯曲等因素带来的影响,从而进一步提升系统的整体性能。这些技术进步共同推动了 Overlay 测量的精度提升,为先进制程的芯片生产提供了坚实的支持。

2.EUV工具层面的技术进展

EUV 光刻技术使用波长为 13.5nm 的极紫外光,实现更小的图形尺寸。然而,EUV 光刻也带来了新的 Overlay 控制挑战:

光学系统的复杂性:EUV 光刻系统采用反射式光学系统,增加了光学路径的复杂性,容易引入图形畸变。

掩模的热变形:EUV 掩模在曝光过程中容易发生热变形,影响图形的准确性。

随机性效应的增强:EUV 光刻中,光子数量减少,随机性效应更加显著,导致图形边缘的粗糙度增加。

EUV 工具层面的技术进展在实现高精度 Overlay(图层对准)方面起着至关重要的作用。光刻工艺的核心目标不仅是以极高分辨率打印出微小特征图形,还必须确保图层之间的精准对准,以实现完美的芯片制造。

为了达到这一目标,工程师们会在晶圆和光罩(掩膜)上刻画微小的对准标记。这些对准标记帮助光刻机内部的晶圆台和掩膜台进行精确对齐。在曝光过程中,光刻机采用扫描方式逐一完成掩膜图案的曝光。每次曝光完成后,系统会移动至下一个芯片位置,重新进行对准并曝光,直到整个晶圆的图案曝光完成。

|

英文术语 |

中文对应 |

简要说明 |

|

Litho Process |

光刻工艺 |

曝光并显影图案 |

|

ADI OL Metrology |

显影后对准量测 |

显影后检查图层对准情况 |

|

Etch Process |

刻蚀工艺 |

将图案转移至材料层 |

|

AEI OL Metrology |

刻蚀后对准量测 |

检查最终图案是否准确 |

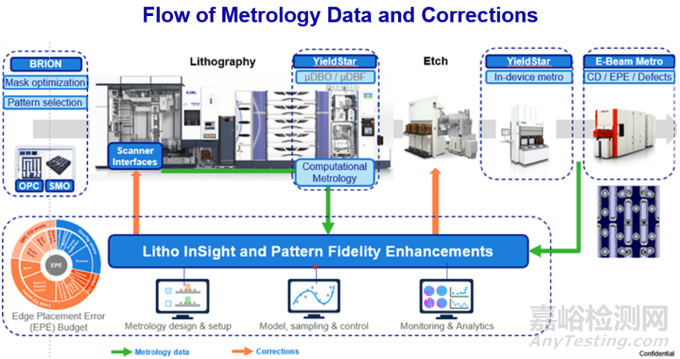

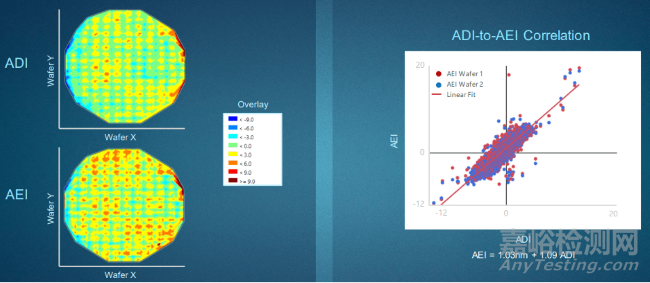

Overlay 测量通常通过两种光学量测系统来完成:显影后检测(ADI)和蚀刻后检测(AEI)。ASML 应用工程部门主管 Jim Kavanagh 提到,存储芯片客户加速采用蚀刻后检测(AEI),这一变化尤其重要,因为在 3D NAND 通道孔结构中,由于蚀刻过程中晶圆间、批次间及腔室间的差异,可能导致 Overlay 偏差变得非常显著。相比之下,逻辑芯片由于器件特征种类繁多,选择一个具有代表性的 Overlay 特征变得更加困难,因此更多依赖显影后检测(ADI)。

|

比较维度 |

ADI(显影后检测) |

AEI(蚀刻后检测) |

|

时间位置 |

光刻显影之后、刻蚀之前 |

蚀刻之后 |

|

检测对象 |

光刻胶图案 |

蚀刻后实际功能层结构 |

|

主要用途 |

曝光质量评估、提前筛查 |

蚀刻质量评估、工艺偏移反馈 |

|

数据反馈对象 |

光刻机修正、OPC模型修正 |

Etch偏移建模、闭环补偿OPC |

|

对良率控制影响 |

避免错误图案继续加工,节约成本 |

最终功能结构判断,影响可靠性 |

|

精度 |

通常为nm级别(受胶形貌影响) |

更高精度(真实结构) |

在晶圆厂中,每台 EUV 光刻设备通常配备 2 至 4 台 Overlay 量测设备,ASML、KLA 和应用材料(Applied Materials)等公司提供了针对这两个步骤优化的关键尺寸(CD)和 Overlay 量测设备。常见的量测方法包括基于图像的 Overlay(IBO)和基于衍射的 Overlay(DBO,或称散射计量 Scatterometry),一些系统则将这两种方法结合使用。

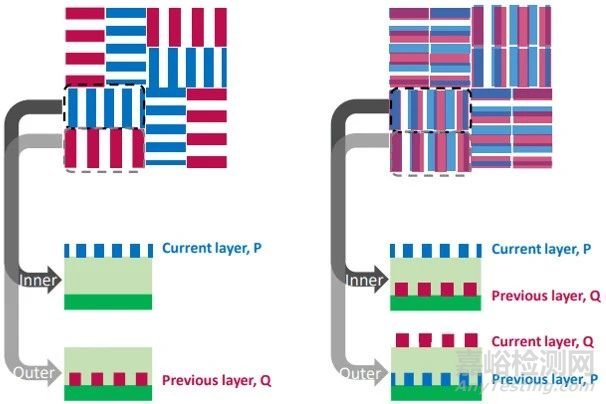

Overlay 测量目标通常设计为上下两个光栅结构,通过调整角度进行成像,检测两者图像边缘的差异来产生信号,实现高精度的 Overlay 测量。在控制过程中,系统结合显影后(ADI)和蚀刻后(AEI)的反馈数据,以及来自光刻机内部传感器的信息,进行补偿和校正。例如,系统会对 x 和 y 方向的线性偏移进行修正,同时进行角度上的旋转误差校正。随着制程的推进和图形的缩小,现代光刻机还具备更高阶的误差修正能力,以确保达到极高精度的要求。

|

维度 |

说明 |

|

检测时点 |

Overlay误差可在 ADI 和 AEI 两个阶段分别评估 |

|

Overlay@ADI |

光刻后评估对准偏移,判断曝光定位精度是否达标(对准参考通常是下层结构的对准标记) |

|

Overlay@AEI |

蚀刻后评估实际功能层之间的对准偏移,更贴近真实器件制造精度 |

Fractilia 公司 CTO Chris Mack 强调,光刻机在扫描过程中不仅能够校正平移和旋转误差,还能够进行更高阶的误差补偿。光刻机通常在芯片的 scribe line 区域放置 Overlay 测量目标,以便进行误差分析。值得注意的是,高阶误差不仅仅存在于芯片四个角落,还可能出现在芯片的中央等区域。因此,晶圆与掩膜在扫描运动中必须进行精细调整,测量点数量越多,运动补偿也越精确,进一步提升了精度控制的能力。

3.边缘定位误差(Edge Placement Errors, EPE)

随着器件特征尺寸的缩小和掩膜层数的增加,Overlay 的容差预算正在不断缩减。此外,随机性效应(stochastic effects)的影响也加剧了这一问题,进一步降低了 Overlay 和关键尺寸(CD)量测的精度。

边缘定位误差(EPE)表示的是晶圆上理想图案与实际制造图案之间的偏差,主要来源于以下四个部分(按重要性排序):

1. CD 均匀性中的随机性误差(如线宽粗糙度 LWR 和线边粗糙度 LER)

2. 光学邻近效应(OPC)引起的 CD 偏差

3. 全局 CD 不均匀性

4. Overlay 误差本身

目前,EPE 的最大来源是随机性误差,而这类误差难以控制。因此,减少 Overlay 误差成为关注的重点,因为它相对较为可控。这对 Overlay 控制的影响意味着,晶圆厂仍需要制造边缘误差非常小的器件,但他们可用于控制 Overlay 和 CD 均匀性的预算已经不足以应对过去的要求。因此,Overlay 和 CD 的精度要求变得更加严苛,缩小速度也更快。

KLA 工艺控制解决方案总监 Andrew Cross 也表达了类似的看法:“随着 5nm 节点对 EPE 容差预算的收紧,Overlay 所占的预算收缩速度最快,并且在同一曝光场内的变化也更加显著。”

为了应对这些日益严苛的要求,业界正在采取多项措施,包括:

提高光学 Overlay 的采样频率,以提高测量的精度和可靠性。

改进现有的 Overlay 测量技术,增强系统的性能。

引入基于扫描电镜(SEM)的 Overlay 测量技术,适用于显影后检测(ADI)和蚀刻后检测(AEI)。

传统光学计量工具通常使用 500 到 650nm 波长的光源,这在许多制程层上能达到较好的测量效果。然而,随着技术进步,也出现了使用 900nm 长波长激光的新方法,能够穿透光学不透明的硬掩膜层(如 NAND 和部分 DRAM 层),这使得量测工具的适用范围进一步扩大。

综上所述,随着制程工艺的复杂化和精度要求的提高,计量系统的灵活性和技术升级至关重要,这些进展将帮助满足不断变化的制程需求,确保晶圆制造中的精度控制不断提升。

4.Overlay 测量与校准

Overlay 测量与校准是确保光刻工艺精度的关键步骤,特别是在现代半导体制造过程中,随着器件特征的不断缩小,精度要求也越来越高。图形定位的首次检查通常发生在光刻胶显影之后。如果在这一阶段发现 Overlay 超出容差范围,晶圆仍可通过返工进行修复。在大规模量产(HVM)过程中,晶圆厂通常会选择每批次(lot)中约 6 片晶圆进行关键尺寸(CD)均匀性和 Overlay 的监控,频率可能为每批次或每两批次一次。

ASML 的 Overlay 监控方法依赖于大量数据的采集与分析处理,能够实时监测并校准图形定位误差。ASML 的 Mulkens 解释了 Overlay 测量的几个关键组成部分:“客户通常从晶圆刻线(scribe line)中的 Overlay 目标图案采集衍射测量数据。我们必须了解这些测得的 Overlay 数据与实际器件区域的 Overlay 之间的关系,这就是所谓的器件 Overlay(device overlay)。"

由于光学测量目标的图案间距一般为几百纳米,而器件图案的间距则只有大约 20 到 30 纳米,这就导致了计量目标与器件之间存在一定的偏差,称为测量目标到器件的偏差(MTD offset)。因此,客户需要对这些偏差进行测量和校准,以确保精确的图形定位。

|

流程阶段 |

关键设备/模块 |

核心作用 |

主要数据类型 |

反馈路径与修正对象 |

|

1.掩模设计(起点) |

BRION 模块(如OPC/SMO引擎) |

- 进行图案仿真与建模 |

- 模拟图形形貌 |

设计端 → 提前补偿掩模图案,减少下游误差 |

|

- 利用OPC(光学邻近效应校正)、SMO(源掩模优化)技术进行预补偿 |

- 图案扭曲预测数据 |

|||

|

|

- 工艺窗口 |

|||

|

2.曝光执行(Litho) |

Scanner(光刻机) |

- 将掩模图案通过光刻投影到晶圆表面 |

- 曝光参数(Dose, Focus) |

曝光偏移、热漂移等误差待后续量测检测 |

|

- 实际执行图案转移的第一步 |

- 投影图案 |

|||

|

3.显影后量测(ADI) |

YieldStar(光学量测) |

- 获取曝光后光刻胶图案的 Overlay/CD(临界尺寸)数据 |

- ADI Overlay |

数据送入 Litho InSight (LIS) 平台,修正曝光或掩模设计参数 |

|

- 提供快速在线量测 |

- ADI CD |

|||

|

|

- 图形变形数据 |

|||

|

4.图案刻蚀(Etch) |

Etcher(等离子蚀刻设备等) |

- 将光刻胶图案转移进工艺层,如 Poly、Contact、Fin 等结构 |

- 图案蚀刻深度与边缘转移行为 |

转移过程中可能引入额外偏移或形变 |

|

5.蚀刻后量测(AEI) |

YieldStar + E-Beam Metrology |

- 使用光学+电子束混合手段进行高分辨率检测 |

- AEI Overlay |

将高精度数据反馈至: |

|

- 获取更真实、最终图案位置数据 |

- AEI CD |

- 曝光参数(如 Dose、Offset) |

||

|

- 检查蚀刻后与下层的对位关系 |

- EPE(Edge Placement Error) |

- 掩模图案(OPC迭代) |

||

|

|

- 缺陷位置与形貌 |

- 光源设定(SMO调整) |

||

|

6.闭环修正(Correction) |

Litho InSight (LIS) 平台 + BRION 模型库 |

- 综合处理所有量测数据 |

- 全流程量测数据(CD、Overlay、EPE等) |

驱动掩模图案、光刻曝光条件、工艺窗口等的实时修正,提升图案保真度与一致性 |

|

- 进行模型拟合与误差分析 |

- 历史趋势与场内变形模型 |

|||

|

- 驱动掩模/工艺/设备参数的修正优化 |

|

然而,这还不是全部。Mulkens 进一步指出:“在 EUV 工艺中,可能还会存在非常局部的随机误差(stochastics),这些误差的量级可能达到几个纳米。因此,业界通常使用电子束(e-beam)系统来测量这些局部误差。综合考虑 CD 误差与 Overlay 误差后,整体的图形定位误差(overlay & placement error)可能达到 4 到 5 纳米。”

电子显微镜(SEM)被用来捕捉这些局部随机性误差,并将其与 Overlay 测量结果结合,进而对扫描曝光系统(scanner)进行 Overlay 和 CD 校正。当新技术的引入以及光学测量系统的相关性成为焦点时,电子束成像(e-beam imaging)逐渐得到了广泛应用。电子束设备能够通过探测背散射电子信号,在埃(Å)级别分辨率下精确识别表面特征,从而提供更高精度的测量结果。

Overlay 测量的精度与准确性在很大程度上依赖于测量目标(target)的结构设计,这些目标通常被放置在晶圆的刻线区域(scribe line)或器件内部的特定区域。目标结构通常由多层薄膜堆叠而成,并包含一个较宽线距(数百纳米)的光栅图案。这种设计能够适配当前的制程层次,并更好地反映器件中的 Overlay 偏差,确保精确的图形定位。

目标图案的设计对 Overlay 测量的效果至关重要。然而,这种设计也受到刻线区域空间限制的影响。为了满足不断提高的精度要求,业界正在向更小、更精细的目标图案迁移。例如,新的设计中,目标图案的尺寸已经缩小至每边仅为 4 到 8 微米(µm),相较于传统的 25×25µm 目标,精度更高。传统的目标图案结构通常采用 bar-in-bar 或 box-in-box 设计,而现在的趋势是采用具有更高灵敏度的改进版设计。

KLA 公司应用开发团队负责人 Shlomit Katz 表示,Overlay 测量目标设计近期出现了显著变化,尤其是莫尔条纹(Moiré effect)目标图案的广泛应用。莫尔条纹效果通过叠加两个略有偏移的图案,产生干涉条纹,从而导致图案的位移、旋转或周期变化。这些变化在测量中被用作相位诱导干涉(phase-induced interference)的基础,从而提高测量精度。

5.APC(先进过程控制)

先进过程控制(APC)是半导体制造中确保高精度与高稳定性的关键技术之一,特别是在曝光前的晶圆测量环节。通过扫描仪对晶圆的形貌(topography)进行实时测量,不仅可以优化曝光质量,还能为过程控制环路提供关键的反馈信息。例如,晶圆形貌地图能有效识别由对焦不均引起的局部 Overlay 偏差,这类偏差往往在传统的 Overlay 抽样中被忽视,从而影响最终的产品质量。

ASML 与 STMicroelectronics 合作展示了其未来晶圆厂的 Overlay 计算修正系统(computational overlay correction)的原型。这一系统通过将物理建模与机器学习结合,能够在没有直接测量的情况下,通过扫描仪的测量结果预测晶圆或批次的 Overlay 偏差。这一创新方法不仅提高了测量的准确性,还为晶圆厂提供了更具前瞻性的过程优化手段。

随着对高精度与高准确度的需求不断上升,行业正逐步转向更高密度的晶圆抽样,以更全面地捕捉晶圆内的特征分布(fingerprints)并深入挖掘晶圆与批次间的差异。这一趋势不仅在光学目标的 ADI 测量中得到体现,在刻蚀后的测量中也同样具有显著意义。特别是在使用电子束(e-beam)工具时,人们越来越关注局部图形定位误差(local placement),这些误差通常会影响到精密工艺的稳定性和可靠性。

应用材料公司(Applied Materials)也指出,提高晶圆抽样密度对于提升测量精度、识别晶圆内的变化或特征模式至关重要。例如,其电子束设备可以同时在多个层级上测量边缘定位误差(Edge Placement Error)与光刻宽度(CD),进一步支持工艺开发中的鲁棒性。

在 Overlay 控制过程中,图案显影后(ADI)与刻蚀后(AEI)之间的相关性被认为是不可或缺的基础。通过精确掌握这两者之间的关系,能够有效优化整个过程的控制能力,确保制程精度的持续提升,从而在不断发展的半导体制造环境中维持竞争力。

|

项目类别 |

ADI(显影后检测)中的 Overlay 用途 |

AEI(蚀刻后检测)中的 Overlay 用途 |

|

检测时机 |

光刻后,显影后(开发后) |

蚀刻完成后 |

|

主要目的 |

- 评估曝光对准精度 |

- 检测最终图案与前一层结构的对准偏差 |

|

- 快速捕捉对准误差 |

- 反映器件层间的真实对位情况 |

|

|

- 捕捉设备热漂移或场内变形 |

- 对关键层对准精度做最终验证 |

|

|

适用场景 |

- 曝光过程在线控制 |

- 工艺过程优化 |

|

- 对准精度快速反馈与修正 |

- 高精度建模验证 |

|

|

- 多图层结构的预判调整 |

- 关键层结构的质量控制(如Fin、Via) |

|

|

优势 |

- 检测快速,数据反馈及时 |

- 精度高,更贴近实际结构对准状态 |

|

- 支持曝光参数快速调节闭环 |

- 更能真实反映良率相关问题 |

|

|

局限 |

- 基于光刻胶图案,可能受胶厚或形貌畸变影响 |

- 检测周期长、成本高 |

|

- 不能代表最终器件结构对位情况 |

- 不适合大规模生产线全覆盖测量 |

EPE = CD误差 + Overlay误差 + Etch Bias误差

ADI 评估的是 EPE 的前两项:CD + Overlay(光刻前)

AEI 能评估全量 EPE:CD + Overlay + Etch偏移(蚀刻后实际结构)

ADI和AEI是Overlay控制的两个关键环节,ADI适合前段快速修正,AEI更贴近真实结构偏移,二者协同构建了先进工艺中精密的图案对准闭环系统。Overlay误差则是EPE控制中的核心变量,决定了最终芯片图案的精度与可靠性。

6.结 语

在半导体先进制程中,Overlay 控制的核心目标是实现更快速的数据反馈,以便及时进行误差补偿,从而确保曝光过程的高精度。然而,随着下一代 EUV 技术——高数值孔径(High-NA)EUV的引入,制程将面临全新的挑战。

高-NA EUV 系统采用了非等距放大(anamorphic lens)技术,这意味着在一个方向上放大 8 倍,在另一个方向上放大 4 倍,导致曝光区域的大小变为传统图场的一半。这一变化要求在晶圆上进行两片掩模图形的拼接(stitching),从而增加了对精度和同步性的要求。

伴随着高-NA EUV 技术的不断发展,Overlay 控制的技术难度将进一步提升,特别是在高精度图形拼接和误差补偿方面的要求将更加严格。通过精确的算法和先进的光学设计,业界正在不断推动技术进步,以应对不断增长的制程要求。

参 考:

1.Patterning Problems Pile Up

2.How Overlay Keeps Pace With EUV Patterning

3.Fabrication of three-dimensional suspended, interlayered and hierarchical nanostructures by accuracy-improved electron beam lithography overlay | Scientific Reports

4.EUV Mask-related Inspection Systems | Lasertec Corporation

来源:芯片技术与工艺

关键词: 芯片