嘉峪检测网 2025-05-12 09:31

导读:今天,我想和大家分享一下 3D IC 设计与封装技术的最新进展、行业应用,以及未来的发展趋势。

1.引 言

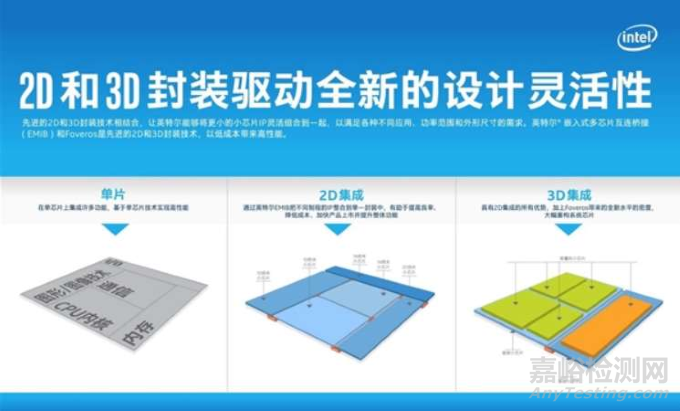

作为一名在半导体封装测试领域摸爬滚打了 21年的“Old Money”,我见证了这个行业从传统2D芯片到如今复杂3D集成的飞速发展。记得有一次,我参与了一个高端芯片项目的封装设计,当时我们遇到了一个棘手的散热问题。传统2D封装无论如何优化,都无法满足芯片的散热需求,项目一度陷入僵局。就在我们几乎要放弃的时候,3DIC封装技术给了我们新的希望。通过将芯片垂直堆叠,并在中间加入微通道冷却结构,我们不仅解决了散热问题,还大幅提升了芯片性能。从那以后,我就深深意识到 3D IC 技术的巨大发展空间潜力,类似国贸大厦,向天上要空间。

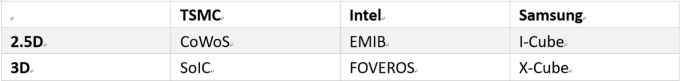

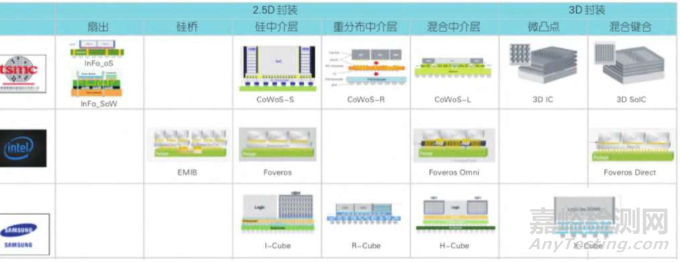

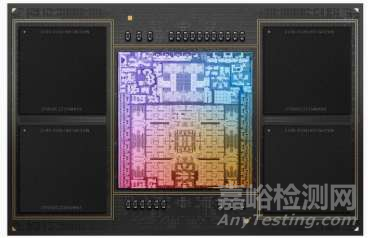

三巨头 2.5D、3D 封装工艺对照如下(附图)

今天,我想和大家分享一下 3D IC 设计与封装技术的最新进展、行业应用,以及未来的发展趋势。

2.3D IC 设计与封装技术的最新进展

(一)技术突破与创新

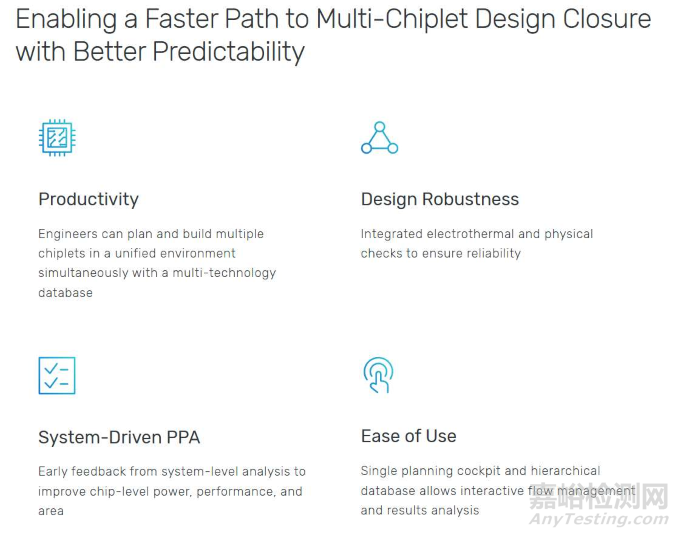

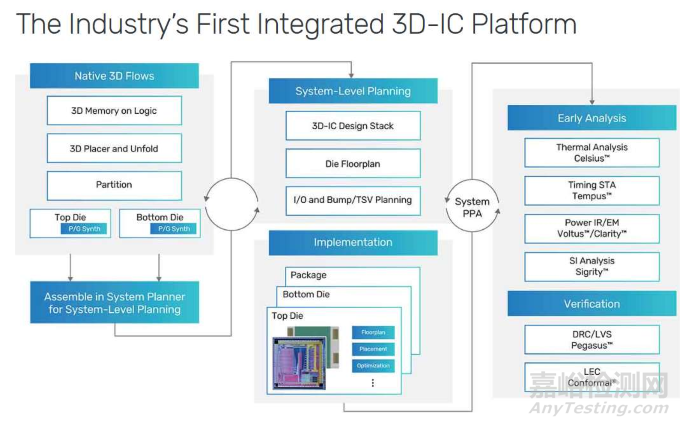

1. Cadence:打通从 Chiplet 到系统的完整 3D-IC 平台生态

Cadence 的 Integrity™3D-IC 平台是目前行业内唯一能覆盖 Chiplet 设计、封装规划、system-level 分析的完整方案。它就像一个“超级管家”,从芯片的最初设计到最终的系统集成,都能提供一站式服务。这个平台不仅支持数字、定制/模拟、热分析工具,还全面覆盖从芯片到系统的全流程设计需求。有了它,Engineers 可以更高效地完成复杂的设计任务,减少设计错误,缩短产品上市时间。

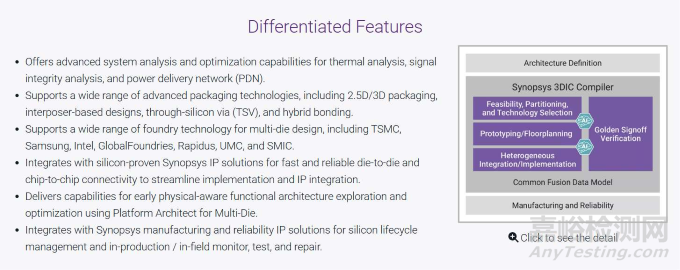

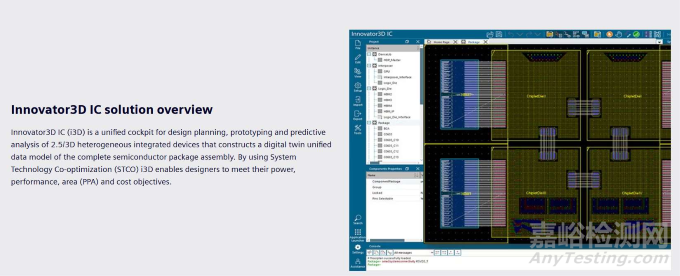

2. Synopsys:多物理场仿真与 AI 赋能设计

Synopsys 通过收购 Ansys,显著提升了多物理场仿真能力。这就好比给设计师们配备 了一双“透视眼”,能够看到芯片在各种物理条件下的表现。其 3DIC Compiler 平台与Ansys 的SI、Thermal landscape和可靠性sign off工具集成,为客户提供芯片、封装和系统级效应的黄金标准sign off精度。此外,Synopsys还引入了AI技术,让设计过程更加智能化。AI可以根据历史数据和设计规则,自动优化设计参数,提高设计efficiency 和质量。

3. Siemens EDA:系统级仿真与封装技术

Siemens EDA(原 Mentor Graphics)在系统级仿真和封装技术方面也持续创新。它的Xpedition™封装设计工具就像一个“精密的拼图大师”,能够将不同的芯片和封装组件完美地拼接在一起。同时,Siemens EDA 的 Calibre®平台提供了从设计到制造的全流程验证工具,支持 2.5D/3D 封装技术。这就好比为芯片设计和制造过程安装了一道“安全门”,确保每一个环节都符合设计要求。

(二)行业应用

1. HPC

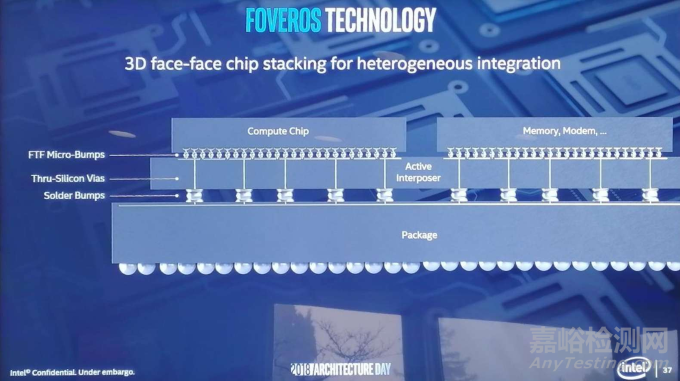

3D IC技术在HPC领域大放异彩。以Intel的Foveros Direct 3D技术为例,它在数据中心GPU应用中支持8层芯片Stack,就像把8块高性能的“砖块”叠在一起,显著提高了计算能力和数据传输速率。这种技术使得数据中心的服务器能够更快地处理海量数据,为 AI、大数据分析等应用提供了强大的支持。

2. 消费电子

在消费电子领域,3D IC 技术让我们的手机、平板电脑等设备变得更轻薄、更强大。

TSMC 的SoIC 技术(基于 CoWoS+WoW 的封装方式)被应用于Apple A16 和 N2 芯片的堆叠,就像在芯片上搭建了一座“微型摩天大楼”,不仅提升了芯片性能,还为设备腾出了更多空间用于其他功能模块。未来,随着技术的不断进步,我们的电子产品将变得更加智能、高效。

3. 汽车电子

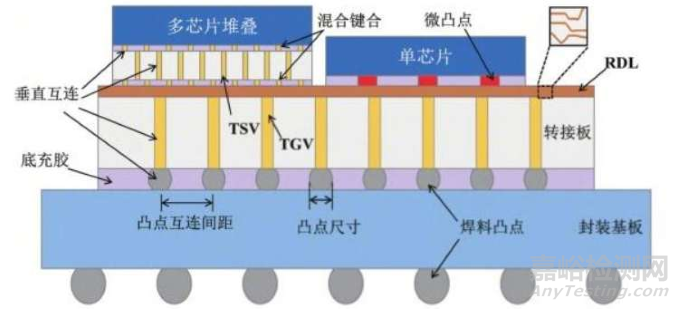

汽车电子领域对可靠性和性能的要求极高。3D IC 技术在这里也大有可为。例如,ASE 的 TGV 技术用于 3D 电感封装,就像给芯片穿了一件“防护服”,显著提高了信号完整性和可靠性。这种技术在自动驾驶辅助系统和车载信息娱乐系统中发挥着重要作用,为我们的出行安全和便利提供了保障。

(三)行业报告与研究

1. CSPT(中国封装协会)报告

根据中国封装协会(CSPT) 的最新报告,中国在2.5D和3D封装技术领域取得了显著进展。国内厂商如JCET、HTtech等在先进封装技术上持续突破,就像在半导体封装的“赛道”上加速奔跑。预计到2025年,中国先进封装市场规模将上涨至1137亿元人民币,这将为国内半导体产业的发展注入强大动力。

中国先进和传统封装规模趋势分析如下(销售口径)

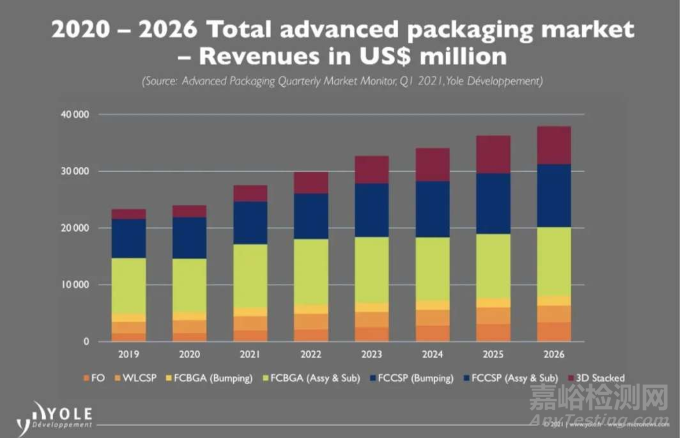

2. ICEPT(世界封装协会)报告

ICEPT 的报告也显示,3D IC 封装技术的实用化开发正在全球范围内加速推进。从2013年开始,3D IC 封装技术的研究开发就涵盖了多种应用场景,包括 3D 系统封装、微波传输系统封装、MEMS 设备制造等。这些技术的发展不仅推动了半导体行业的发展,也为其他高科技领域带来了新的机遇。

3.未来发展趋势

(一)更高集成度

未来,3D IC 技术将朝着更高集成度的方向发展。就像在芯片上搭建更高的“摩天大楼”,实现更多功能单元的堆叠。TSMC 预计到 2027 年,其 SoIC 技术将实现 3μm 间距,支持 8 层芯片堆叠。这意味着我们可以在更小的空间内实现更强大的功能,为未来的智能设备和高性能计算提供更强大的支持。

(二)更低功耗

随着技术的不断进步,3D IC 将进一步降低功耗。通过优化设计和制造工艺,例如 Intel 的 Foveros Direct 3D 技术,互连功耗降低至 0.15pJ/bit,相比传统方案降低 30%。这不仅延长了设备的电池寿命,也为环保和可持续发展做出了贡献。

(三)更广泛应用

3D IC 技术将在更多领域得到应用,如 AI、量子计算、生物医学等。例如,在 AI 领域,3D IC 可以实现更高的计算能力和更低的延迟,为智能算法的运行提供强大的硬件支持。在生物医学领域,3D IC 可以用于开发微型化的医疗设备,为疾病的诊断和治疗提供更精准的工具。

4.面临的挑战

(一) Heat dissipation

High - density stacking 带来了散热挑战。就像在“摩天大楼”里安装了太多的“发动机”,如果不解决散热问题,IC 可能会因为过热而损坏。Intel 开发的纳米复合应力缓冲层, CTE 可调范围达 3-7ppm/°C,为散热问题提供了一种解决方案。

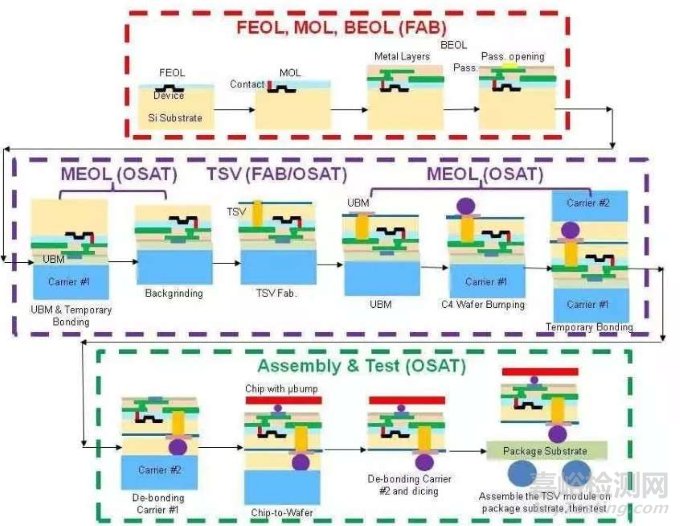

(二)TSV

TSV 的制造过程复杂,需要高精度的深孔刻蚀和金属填充技术。TSV 内的缺陷可能导致信号传输问题,就像在“摩天大楼”的“电梯”里出现了故障。这需要进一步改进制造工艺,确保 TSV 的质量和可靠性。

(三) Rel of Bonding

键合技术需要确保芯片层间的物理连接和对齐,特别是在高温和高湿度环境下。键合强度的稳定性是一个关键问题,就像“摩天大楼”的“地基”必须足够坚固。这需要开发更先进的键合材料和技术,以提高键合的可靠性和稳定性。

5.总 结

3D IC 设计与封装技术作为半导体行业的前沿领域,正在快速改变芯片制造和系统集成的未来。通过将多个芯片垂直堆叠,3D IC 技术不仅提高了集成度和性能,还显著降低了功耗和尺寸。尽管面临散热、制造、键合等挑战,但随着技术的不断进步,3D IC 将在更多领域得到广泛应用,推动半导体行业的发展。未来,3D IC 技术将朝着更高集成度、更低功耗、更广泛应用的方向发展,为高性能计算、消费电子、汽车电子等领域带来更多的创新和突破。

参 考:

《Cadence whitepaper》

《集成电路封装可靠性技术》

《Cadence Design Systems Annual Report 2022》

《基于SiP技术的微系统》

半导体国产替代三大核心赛道梳理

台积电新一轮EDA订单已锁定:西门子、新思科技、Cadence、Ansys!

先进封装:美国、中国、韩国最新进展盘点-电子工…

来源:芯片技术与工艺

关键词: 芯片