嘉峪检测网 2025-05-19 10:12

导读:台积电(TSMC)提出了一种基于2nm CMOS纳米片工艺的38.1Mb/mm² 高密度SRAM设计,用于高密度与高能效计算应用。

本文是台积电(TSMC)存储器IP开发总监Tsung-Yung Jonathan Chang博士在2025年第72届国际固态电路会议(ISSCC)SRAM专题会议上发表的题为《A 38.1Mb/mm² SRAM in 2nm CMOS Nanosheet Technology for High Density and Energy-Efficient Compute Applications》的演讲。

英特尔与台积电关于先进制程节点中的相同SRAM面积微缩成果对比

在4月15日的公众号发文中我们详细阐述了英特尔基于18A工艺节点RibbonFET与PowerVia技术的高容量(HCC)/高密度(HDC)6T SRAM架构:相较FinFET方案,HCC与HDC存储单元面积分别缩减至0.77倍与0.88倍,对应0.023μm²与0.021μm²。通过优化传输门(PG)与下拉管(PD)比例,可在读写路径间实现最低VMIN。RibbonFET技术使HDC/HCC存储单元无需依赖字线欠压驱动(WLUD)等辅助电路即可达成具有竞争优势的VMIN,并在全压驱动下获得额外读取性能增益。

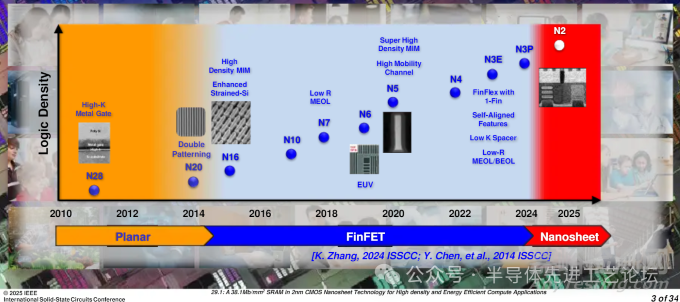

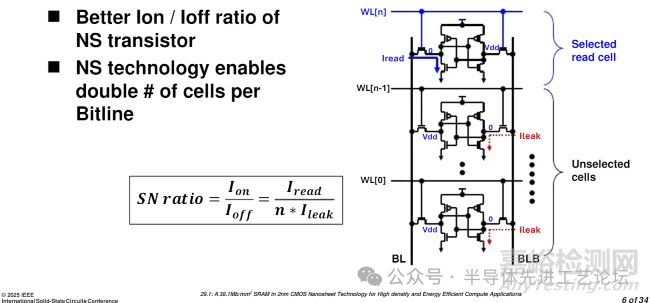

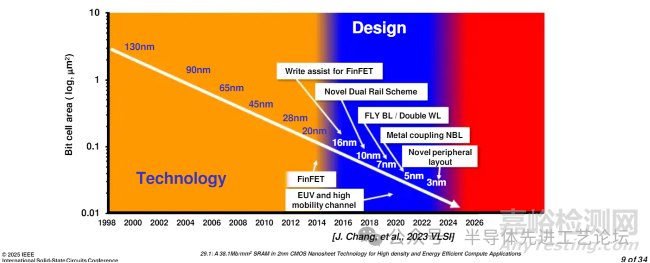

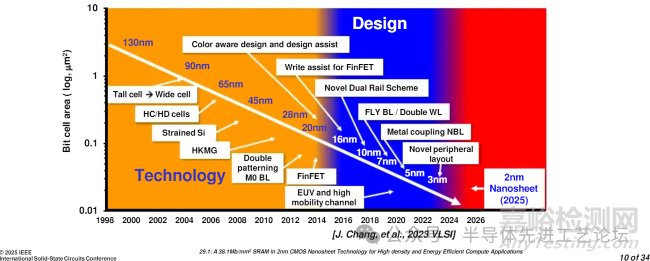

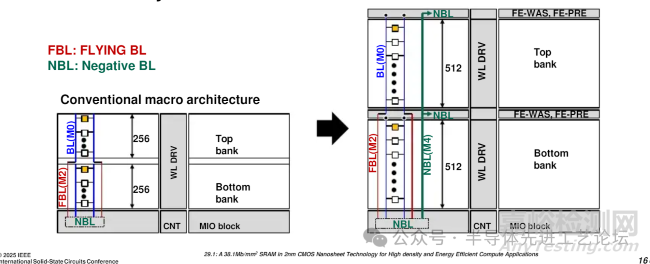

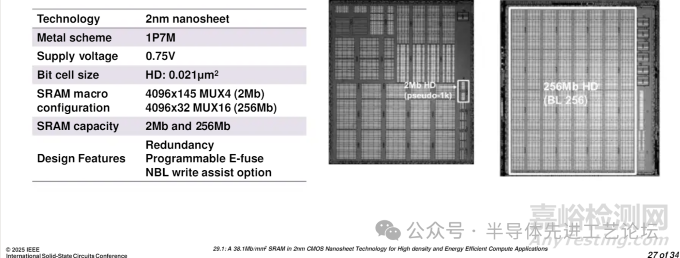

台积电在2025年ISSCC SRAM专题会议中详述其2nm(N2)节点的SRAM微缩路线。SRAM微缩在3nm节点停滞之后,于2nm节点实现部分重启。台积电基于2nm的SRAM宏单元采用0.021μm²存储单元,阵列规模为4096×145(总容量580Kb)。相较前代节点,存储密度提升10%,达到38.1Mb/mm²。为实现这一目标,台积电通过最大化存储单元阵列规模并最小化外围电路:2nm纳米片晶体管技术改善了存储单元的开关电流比,使得单条位线(BL)可负载的单元数量翻倍。相较于FinFET技术最大256单元/BL的限制,2nm技术允许其扩展至512单元/BL。此外,采用飞行位线(FBL)架构进一步提升了阵列效率。这本质上是利用纳米片晶体管(NSH)较FinFET更优的Ion/Ioff特性,重构外围电路设计。

综上所述,尽管技术路径不同(纳米片vs纳米带),台积电N2与英特尔18A均实现SRAM存储单元0.021μm²级密度。从单纯追求特征尺寸微缩,转向器件结构创新(GAA)与系统级供电/互连优化(PowerVia/FBL)的协同设计。新型晶体管通过Ion/Ioff提升,推动存储阵列规模扩展与外围电路精简,为存算一体架构奠定物理基础。

演讲摘要

在本文中,台积电(TSMC)提出了一种基于2nm CMOS纳米片工艺的38.1Mb/mm² 高密度SRAM设计,用于高密度与高能效计算应用。该设计采用0.021um²的高密度存储单元,并通过设计-工艺协同优化(DTCO),使整体SRAM密度较前代技术节点提升1.1倍。

半导体赋能创新,智享生活

Outline

2nm工艺技术亮点

SRAM存储单元及微缩趋势

SRAM设计技术

最大化存储单元效率

远端写入辅助(FE-write assist)技术

远端预充电器(FE-pre-charger)

高性能计算双泵(Double pump)SRAM架构

芯片实测结果

总结

2nm工艺技术亮点

成功迈入纳米片(NS)晶体管时代

基于三维集成电路(3DIC)技术定义和优化,实现高能效计算与系统集成。

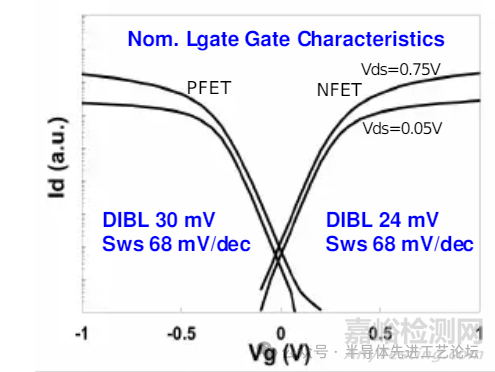

高能效纳米片晶体管(NS),具备优异的驱动电流、漏致势垒降低(DIBL)和亚阈值摆幅(SWS)特性。

中段/后段制程(MEOL/BEOL)实现约20%的RC降低,并为高密度设计优化设计规则。

铜再分布层(Cu RDL)与平坦化钝化技术实现更低电阻、更优性能、可靠芯片封装互连(CPI)及更高芯片间(D2D)I/O密度。

每根位线的存储单元数量

更优的纳米片晶体管(NS)开态/关态电流比(Ion/Ioff)

纳米片(NS)技术实现每根位线存储单元数量翻倍

SRAM存储单元及微缩趋势

技术与设计创新共同推动SRAM微缩

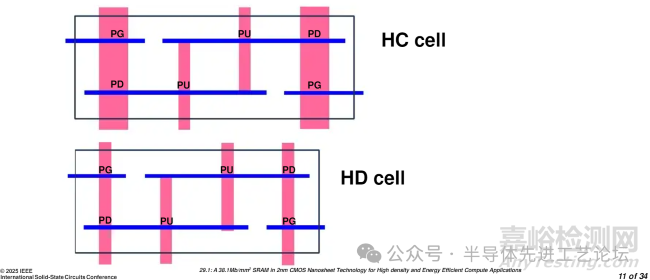

基于纳米片技术的高容量(HC,High-Capacity)/高密度(HD,High-Density)存储单元

灵活的氧化层定义(OD)宽度实现最优存储单元工作电压(VDD)窗口

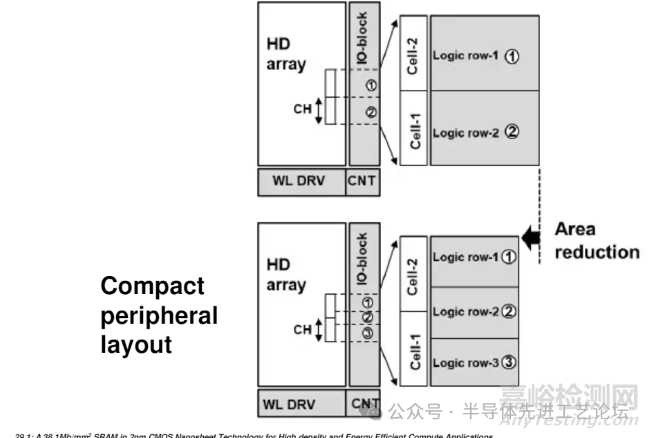

高密度存储单元(HD Cell)的外围电路布局方案

采用2位-3行结构的紧凑型外围布局是高密度SRAM面积微缩的关键调节手段。

高容量存储单元(HC Cell)的类似布局技术

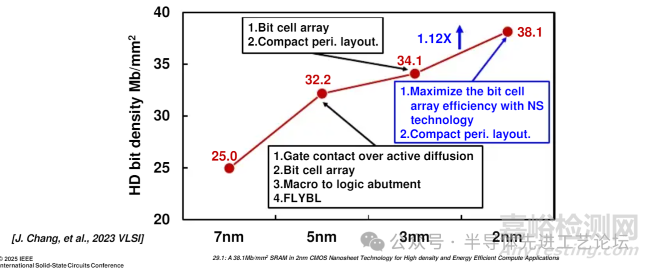

高密度SRAM(HD SRAM)的密度发展趋势

紧凑的外围电路布局可实现高密度(HD)宏单元微缩

N2工艺高密度(HD)位密度 >38.1Mb/mm²

高容量SRAM(HC SRAM)的密度发展趋势

设计工艺协同优化(DTCO)推动高容量SRAM宏单元持续微缩

1.18倍密度提升(相较于3nm工艺)

SRAM设计技术

最大化存储单元效率

远端写入辅助(FE-write assist)技术

远端预充电器(FE-pre-charger)

高性能计算双泵(Double pump) SRAM 架构

HD宏单元布局规划

通过优化存储单元效率实现SRAM密度倍增

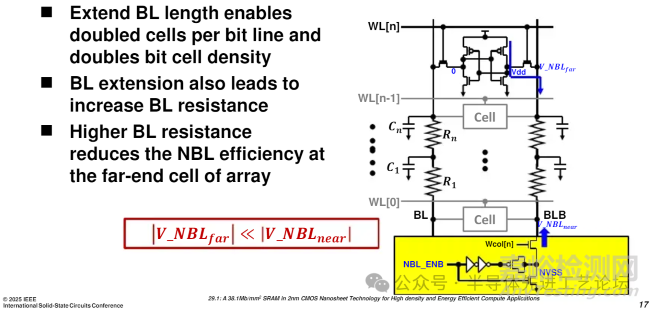

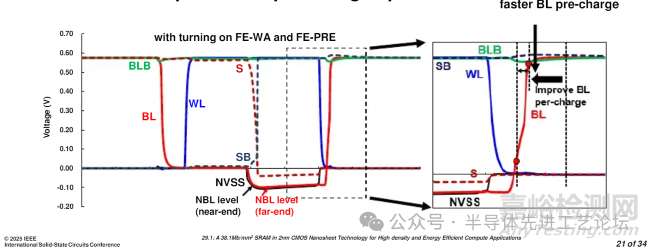

远侧存储阵列的NBL升压技术挑战

通过延长位线(BL)长度,实现每根位线连接单元数量翻倍,从而使存储单元密度倍增。

位线(BL)延长同时会导致位线电阻增加

更高的位线电阻会降低阵列远端单元的NBL(负位线)效率

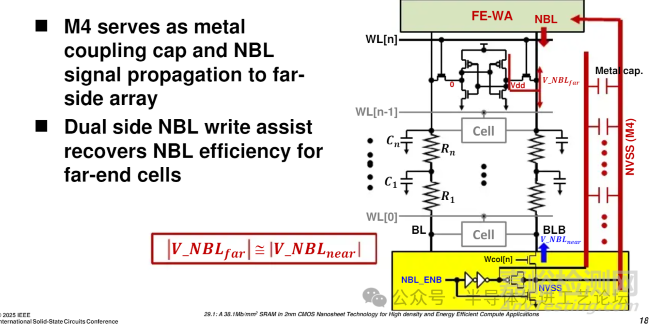

远端写入辅助(Far End Write Assist)技术

M4金属层充当耦合电容,并负责将 NBL(负位线)信号传输至远侧存储阵列。

双侧NBL写入辅助技术可恢复远端存储单元的负位线效率

双侧预充电器与写入驱动器

位线预充电与列选信号传输至阵列远侧

写入数据信号(Write Data Signals)

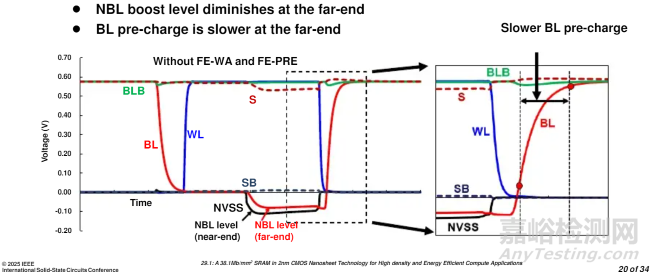

由于位线(BL)RC参数增加

负位线(NBL)升压电平在远端衰减

位线(BL)预充电速度在远端变慢

采用远端写入辅助(FE-WA)与远端预充电(FE-PRE)的仿真波形

FE-WA技术显著缩小近端与远端负位线(NBL)电平差异

FE-PRE技术显著提升位线(BL)预充电速度

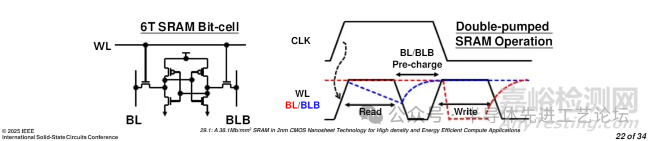

AI/HPC的双泵式(Double-pumped)SRAM设计

AI/HPC对高内存带宽的需求: 双泵6T SRAM设计

双泵SRAM实现每周期1次读取+1次写入(1R1W)操作

相较于8T(双端口)SRAM的密度优势

在1R1W操作场景下,较单端口SRAM实现更高带宽与最大频率。

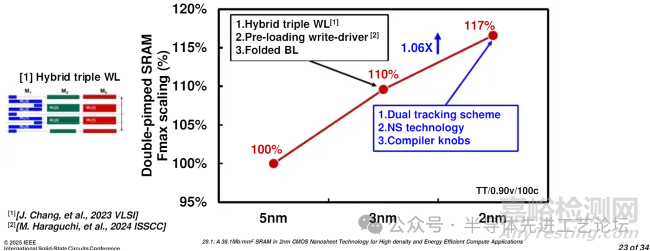

双泵SRAM的最大工作频率(Fmax)优化技术

核心调控手段: 双轨追踪技术、NS技术与电路优化

1.06倍最大频率提升(相较于3nm工艺)

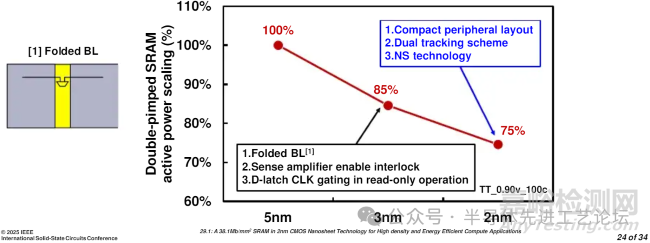

双泵SRAM动态功耗(Active Power)优化技术

核心调控手段: NS技术、紧凑外围布局与双轨追踪技术

动态功耗降低: 较3nm工艺标准宏单元(Macro)减少11%

能效提升: 较3nm基准工艺实现约1.19倍增益

双泵SRAM中的双轨追踪技术

TURBO ON模式: 绕过追踪单元以优化设计裕量

Fmax提升6.3%,同时保持充足的读取/写入裕量(RM/WM)。

动态功耗降低11.5%: 通过减少BL/BLB电压摆幅实现

TURBO OFF模式: 追踪单元可实现更低的最小工作电压(Vmin)操作

芯片实测结果

测试芯片

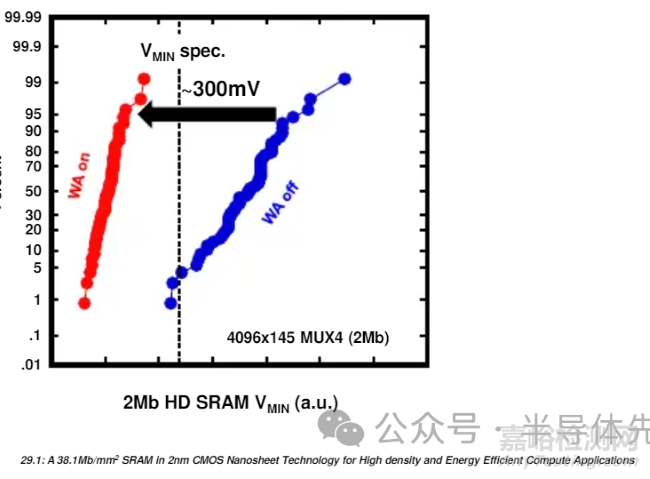

2Mb高密度(HD)SRAM最低工作电压(VMIN)累积分布图

写入辅助(Write Assist)技术使2Mb高密度(HD)SRAM的伪1024cells/BL设计最低工作电压(VMIN)降低超300mV。

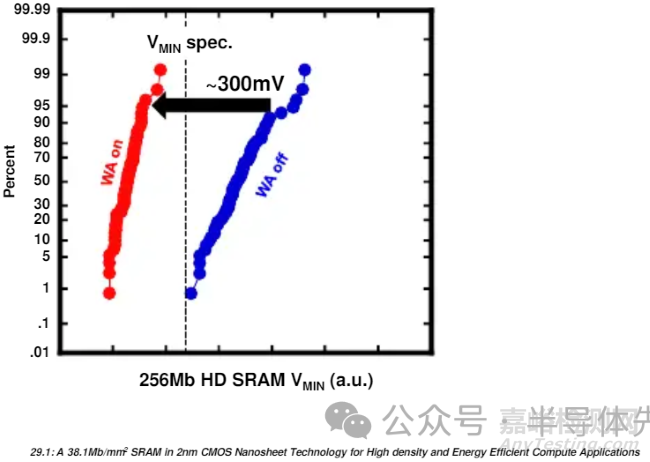

256Mb高密度(HD)SRAM最低工作电压累积分布图

写入辅助(Write Assist)技术使256Mb高密度(HD)SRAM(256 cells/BL)的最低工作电压降低超300mV。

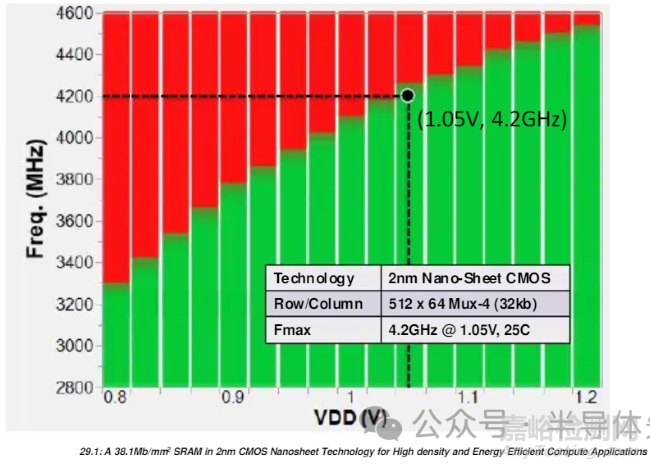

双泵SRAM最大工作频率(Fmax)参数扫描分析图

双轨追踪(Dual-Tracking)技术方案在1.05V电压下实现4.2GHz工作频率。

总结

成功在2nm纳米片(Nanosheet)工艺上验证全功能高密度(HD)SRAM,实现38.1Mb/mm²存储密度。

高密度SRAM(HD SRAM)通过远端写入辅助(FE-WA)和远端预充电(FE-PRE)实现最低工作电压(V_MIN)降低超300mV。

采用双轨追踪(Dual-Tracking)技术方案的高容量(HC)SRAM在1.05V电压下实现4.2GHz工作频率,较3nm工艺能效提升约1.19倍。

来源:半导体先进工艺论坛

关键词: 存储器