嘉峪检测网 2025-05-10 10:46

导读:本文介绍了DDR3的测试规范。

一、测试目的

DDR3的测试分为三类:

1、直流参数测试(DC Parameter Testing):校验工作电流、电平、功率、扇出能力、漏电流等参数特性。内存的工作电流与功耗、负载有关,工作电流过高时,将造成功耗过高,给系统造成的负载过大,严重情况下将造成系统无法正常工作。存储芯片也存在漏电流,当漏电流超出阈值时可能造成系统无法正常工作。

2、交流参数测试(AC Parameter Testing):检测诸如建立时间、保持时间、访问时间等时间参数特性。

3、可靠性测试(Functional Testing):测试存储器件的逻辑功能是否正常。对存储单元、读出放大器、写驱动器等产生的物理故障进行检测。另外,在存储器装配到电路板上以后,存储器外围互连线的故障也在规范要求的测试范围内。

二、存储器测试规范总则

规则2.1:UT相关测试项要求主芯片工作在最重的负载状态。

说明:因为主器件的工作状态对其输出信号的指标影响很大,包括芯片内部串扰,供电能力,SSN影响等,都对输入到DDR3芯片的信号有影响,所以要求主芯片工作在重载状态。

规则2.2:在对存储器进行测试时,如果发现故障,必须打印详细的故障信息。

说明:提供详细的信息主要是为了方便定位故障,上报的信息包括但不限于:什么测试失败,在哪个地址,写入什么数据,读到什么数据等。如:上报数据线走步1测试失败,在0x00000000地址,写入0x00000100,读出0x00000000,则可以大致确定为D8相连的网络有问题,当然仅凭这些信息还不能准确的定位是存储器侧数据线故障还是与之数据线相连的其它芯片故障。

三、单元测试

噪声/热/功耗测试

此处定义芯片的最大功耗模式工作状态

1、接近物理极限的的行切换速率

ACTIVATE/PRCHARGE命令实现行打开及关闭,BANK内行切换速率受限于Trc参数。行切换速率同时受限于控制器PHY的访问方式。行切换速度越高,芯片功耗越大。

2、接近物理带宽的读写访问

读写速率取决于控制器性能及控制器访问方式。

3、所有BANK同时打开其中一行,使用BANK交织的方式进行读写操作

不同BANK 行间的切换速率受限于Trrd参数

4、自刷新打开

DDR3芯片自刷新瞬间电流很大,刷新周期38us左右,使用高采样率ms级测试能够将刷新毛刺带来的噪声捕获到。

规则3.1.1:功耗,热,噪声测试要求芯片处于功耗最大状态。

信号线测试

本节定义接口信号测试码型:

1、芯片工作于最大功耗模式

参考3.1节要求,在3.1节要求基础上提出更进一步测试条件定义。

2、读写均衡,按照芯片工作场景定义;

软件实现如下配置的选择:完全读,完全写,1读1写,N读N写。

3、总线50%时间执行SSN测试

在DDR3测试规范中,SSN(Simultaneous Switching Noise,同时切换噪声) 是指当多个信号线(如数据总线、地址总线或控制信号)在同一时刻切换电平时,由于电流突变和电源/地网络的寄生电感效应产生的瞬态噪声。这种噪声可能导致信号完整性下降,进而引发时序错误或逻辑误判。

验证在以下场景中,信号和电源完整性是否满足DDR3规范要求:

多信号同时切换 :大量总线同时翻转时产生的噪声(如选项A、B)。

极端频率覆盖 :确保从基频(1x时钟)到低频谐波(1/5x时钟)均无噪声超标(选项C)。

对定义A/B/C的详细解读

A. 全总线同步切换测试

操作:所有总线在同一时刻切换电平,数据码流为交替的 010101 和 101010。

目的 :模拟最恶劣的噪声场景(所有信号同时翻转),验证电源/地网络能否承受最大瞬时电流变化,避免电压跌落(IR Drop)或地弹(Ground Bounce)。

B. 部分总线切换测试

N-1总线切换,1条总线保持静态(长高/长低)

操作:N-1条总线执行SSN测试,1条总线(Xi)保持固定电平(高或低)。

目的 :测试静态信号线在周围信号切换时是否受到串扰(Crosstalk),尤其是相邻信号线的高频噪声耦合。

N-1总线切换,1条总线反向切换

操作:N-1条总线执行SSN测试,1条总线(Xi)与其他信号反向切换。

目的:验证反向信号是否因共模噪声(Common-Mode Noise)导致时序偏差或眼图闭合。

C. 频率覆盖测试

要求 :信号频率需覆盖基频(1x时钟)及其分频(1/2x, 1/3x, 1/4x, 1/5x)。

目的:确保系统在不同频率下的噪声抑制能力,尤其是低频场景(如低功耗模式)下电源滤波和去耦电容的有效性。

DDR3中SSN测试的关键点

电源完整性(PI)验证 :测量电源网络在SSN下的瞬态响应(如电压波动ΔV)。

确保去耦电容(Decoupling Capacitor)布局合理,抑制高频噪声。

信号完整性(SI)验证 :通过眼图分析信号质量(抖动、上升/下降时间、过冲)。

检查时序裕量(Timing Margin)是否满足规范(如DDR3的tDS/tDH参数)。

测试方法 :码型生成器 :发送特定码流(如选项A的交替码)模拟极端场景。

示波器/逻辑分析仪:捕获信号波形和噪声频谱。

时域反射计(TDR):定位阻抗不连续点(如过孔、连接器)。

对于SSN测试的定义:

A、所有总线同时刻处于某一电平标准,数据码流为010101 101010时钟码流的SSN测试

B、N条总线Xn,N-1条SSN测试,1条Xi信号长高,长低;i∈{X0…..Xn}

N条总线Xn,N-1条SSN测试,1条Xi信号信号与其他信号反向;i∈{X0…..Xn}

C、要求信号频率覆盖1x时钟频率,1/2x时钟频率,1/3x时钟频率,1/4x时钟频率,1/5x时钟频率。

4、总线50%时间执行PRBS测试

对于PRBS测试的定义:

A所有总线同时刻处于某一电平标准,数据码流为PRBS码流的SSN测试

A所有总线执行独立的PRBS码流测试

5、地址线保证

地址线的测试条件和数据线一样。

地址线速率比数据线速率低一半,关注重负载时候的时序指标。

由于地址线实现类似数据线的要求难度很大,信号测试要求地址线有较频繁操作即可(既每根地址线都有高频率的01翻转)。

规则3.2.1:对存储器数据线进行测试时,要求芯片工作于最大功耗模式。总线读写均衡,测试码型覆盖SSN和PRBS测试。

建议3.2.1:信号测试使用眼图测试,保证眼图捕获到各种码型的叠加效果。高速信号使用差分探头做小量信号抽测。

规则3.2.2:UT测试过程必须保证正常的访问,不能在访问出错的时候进行。

初始化测试

1、上电初始化时序测试

1、/RESET、CKE、电源的处理

A、/RESET保持小于0.2 VDD,所有其余输入信号状态无关;

B、在电源稳定后,/RESET保持至少200us低电平;

C、CKE在/RESET拉高前拉低,CKE拉低到/RESET拉高至少有10ns延时;

D、电源从300mV到VDDmin的时间应小于200ms;

E、电源上升时,VDD>VDDQ,且(VDD-VDDQ)<0.3V;

2、/RESET拉高后,CKE需至少保持500us低电平再拉高。(这期间DRAM开始内部状态初始化,这些操作独立于外部时钟)

3、CK、CKE的处理

A、CK、/CK在CKE ACTIVE前至少要稳定tCKSRX(max[10ns,5tck]);

B、保证CKE拉高到CLOCK的setup时间tIS;

C、在CKE ACTIVE前需要注册一个NOP或Deselect命令,此命令也要保证tIS;

D、一旦CKE在/RESET后被拉高,CKE要保持高直到初始化过程完毕(包括tDLLK、tZQinit)。

4、ODT的处理

A、DDR3在/RESET、CKE为低的时间内保持ODT高阻,一直到CKE被拉高后;

B、对于DDR3颗粒来说,ODT 输入信号在CKE拉高前可以为不确定状态,CKE拉高后ODT输入信号将稳定为高或低;

C、如果Rtt_nom使能,ODT输入信号应保持低;

D、ODT输入信号保持稳定直到上电初始化过程完毕(包括tDLLK、tZQinit)。

5、CKE拉高后需要等待tXPR后才能发第一个MRS命令,用以加载模式寄存器。

6、加载MR2。

7、加载MR3。

8、加载MR1。

9、加载MR0。

10、发ZQCL命令启动ZQ校准。

11、等待tDLLK、tZQinit延时完毕。(tDLLK从加载MR0开始算,tZQinit从ZQCL命令开始算)

12、DDR3 准备好正常操作。

2、复位测试

同上电复位流程,重点关注单板热复位时候DDR3有无复位信号发送

无复位信号下发的时候确保读写操作完成后再复位(拉低cke,停时钟)

单元测试用例

UT测试说明:示波器在DDR测试中越来越局限,例如读方向控制器端最终信号、内部时序调整部分是无法搞定的,当然还是有些参数的测试值是有参考意义的,此处列出UT测试标准供参考。

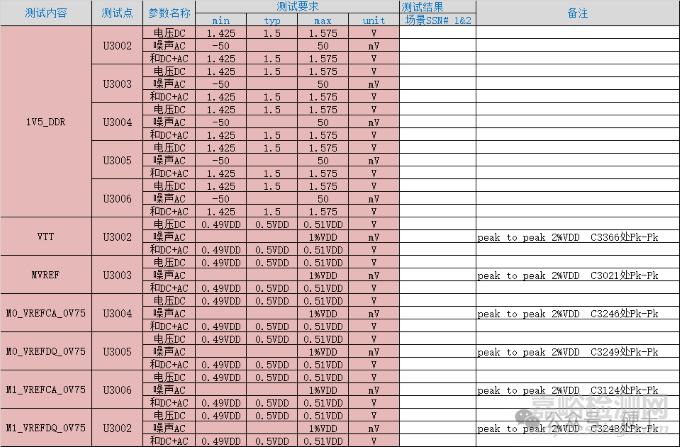

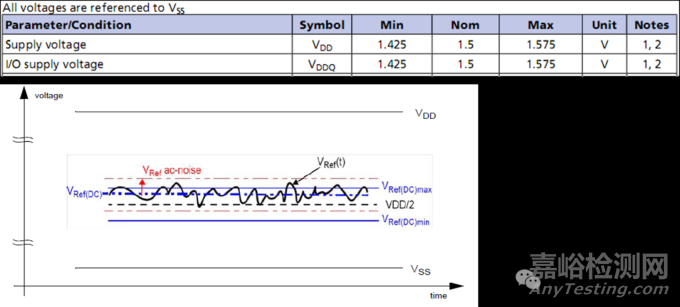

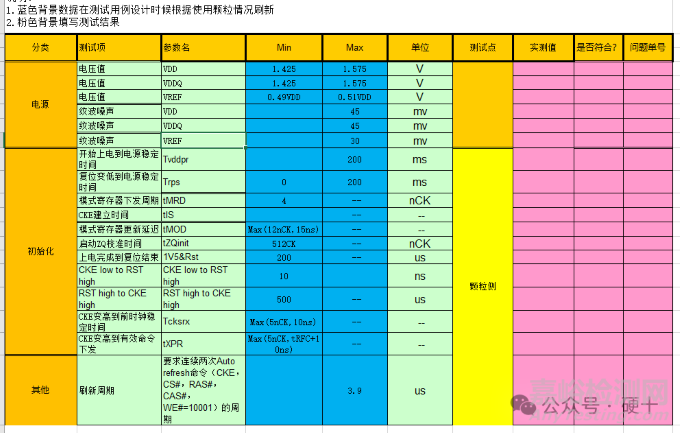

电源及初始化

写方向

读方向

来源:硬十

关键词: 存储器