嘉峪检测网 2025-06-25 08:38

导读:本文介绍了用于提升CMOS性能的应变技术SMT/CESL/eSiGe/eSiC-原理及应用。

工艺尺寸微缩可提升芯片集成密度并加速逻辑开关速度,但 Shrinking size 面临以下挑战:制造可行性、性能与可靠性维持,以及栅极氧化层减薄引发的迁移率劣化。为突破性能瓶颈,除Shrinking size 外,迁移率增强也是一个有吸引力的选择,而应变硅技术通过调控载流子迁移率成为关键解决方案。

下面会逐步介绍应变硅技术的原理及应用:

Strain Process:

应力记忆技术(SMT):增加NMOS电子迁移率

接触孔刻蚀停止层(CESL):协同增加NMOS/PMOS迁移率

嵌入式SiGe(eSiGe):增强PMOS空穴迁移率

嵌入式SiC(eSiC):增强NMOS电子迁移率

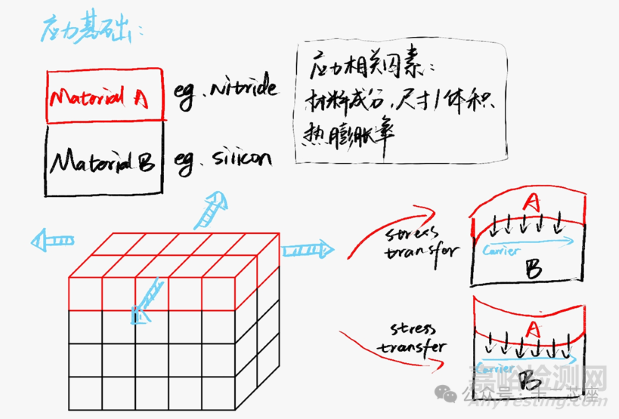

Stress basic:

由于材料A与B在组分成分、原子/分子尺寸(体积)及热膨胀系数上的不匹配,A会对B施加机械应力。

Fig1. Mechanical Stress: basic

其物理原因和机制如下:

应力传递有多种方式,主要取决于

材料A的沉积/生长条件(如工艺温度、材料特性)

后续工艺步骤(如退火、离子注入)

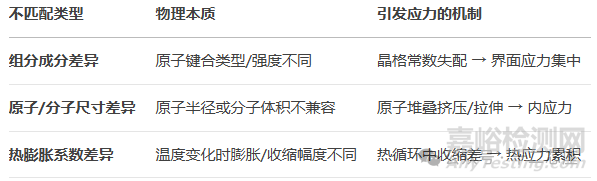

Fig2. Uniaxial stress: 1-direction(left); biaxial stress: 2-directions(right)

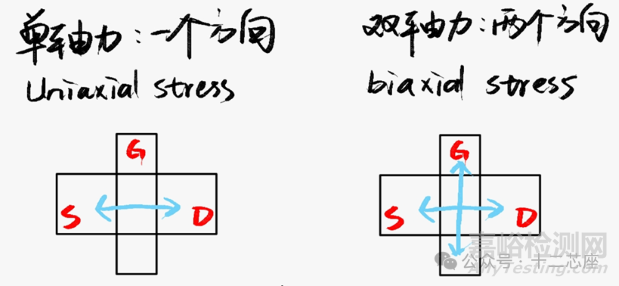

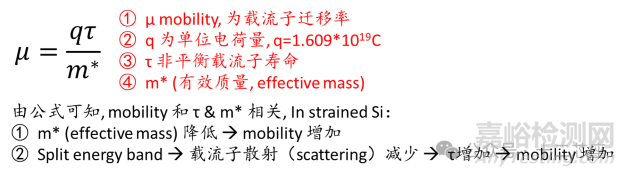

从载流子迁移率公式可知,迁移率大小和有效质量和非平衡载流子寿命相关,那么应力是怎样影响到载流子迁移率的呢,是让其变快还是变慢呢?

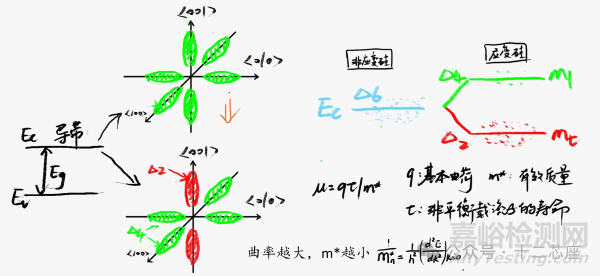

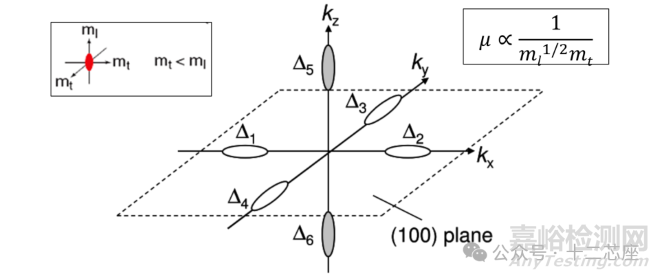

导带调控,对于电子迁移率(electronic mobility)

Fig3. 应变硅中的导带调控

拉应力(Tensile)作用:

解除六重简并 → Δ5/Δ6 (对应上图 Δ2)

能谷下移电子优先占据低有效质量能谷 Δ5/Δ6(纵向有效质量小-mt)

电子迁移率和有效质量的关系如下,综合ml和mt,电子有效质量降低导致电子迁移率增加。

Fig4. 硅的导带能谷原理图, Schematics of the conduction band valleys of silicon

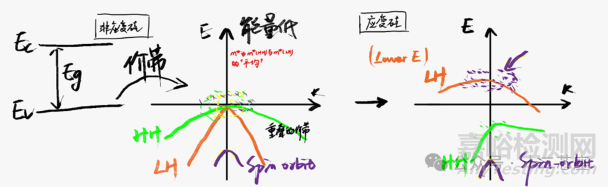

价带调控,对于空穴迁移率(hole mobility)

Fig5. 硅的价带最大值示意图,Schematics of valence band maximum of silicon

压缩应力作用:

HH/LH简并解除,LH带上移,HH带下移,能带分裂带来更少的载流子散射,从而得到更高的迁移率。

HH=heavy holes, LH=light holes

空穴优先占据LH带(低能态),空穴迁移率的各向异性:

<110>沟道:LH主导 → 迁移率显著提升

<100>沟道:HH贡献大 → 提升有限

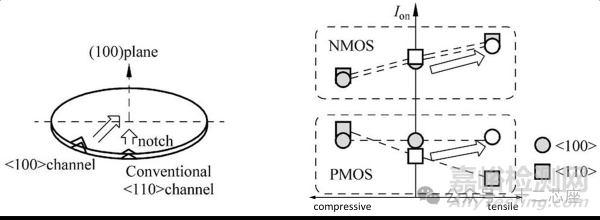

Fig6. 沟道晶向和应力类型对于CMOS器件驱动电流的影响

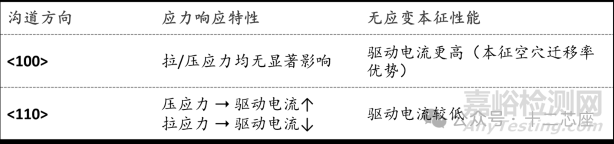

由Fig6. 可知,对于不同的沟道晶向,NMOS/PMOS 对应力所起的作用具有差异,具体如下:

对于NMOS:

<110>和<100>沟道:拉应力均使驱动电流增大,压应力则使其减小。

PMOS则表现出与NMOS不同:

<100>沟道:拉/压应力对驱动电流影响微弱;

<110>沟道:压应力均使驱动电流增大,拉应力则使其减小。

需特别说明的是,未施加应变时,<100>沟道PMOS因本征空穴迁移率更高,其驱动电流优于<110>沟道。

这也是未采用应变技术时,业界选择(100)晶圆上<100>沟道设计PMOS的原因。而后为实现应变工程增益,PMOS须制备于<110>沟道并施加压应力。

应变工程方案:

PMOS:采用 <110>沟道 + 压应力(eSiGe等)

NMOS:任意晶向 + 拉应力(SMT/CESL等)

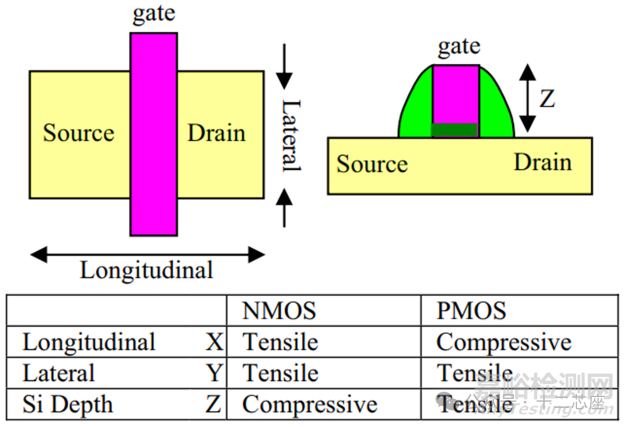

Fig7. CMOS 性能提升所期望得到的力

由上文可知应力破坏了晶体对称性,分别消除了价带的2重简并性和导带的6重简并性。这将导致能带散射率和或载流子有效质量发生变化,进而影响载流子迁移率。然而,NMOS和PMOS载流子在三个方向即纵向(longitudinal)、横向(lateral)和硅深度方向(Si depth directions)上与沟道应变的相互作用不同。Fig7. 展示了单轴应力的可能方向及NMOS/PMOS 性能提升所期望得到的力。

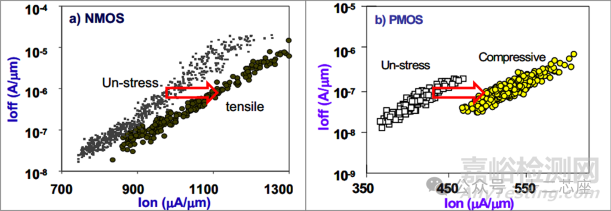

Fig8. NMOS & PMOS 有无应力响应性能对比

NMOS电流在通道中施加拉应力时增强,而PMOS电流在施加压应力时增强。Ion/Ioff 提升如Fig8. 所示。

Reference:

1.H. Ibach and H. Lüth (2003). Solid-State Physics: An Introduction to Principles of Materials Science, Springer-Verlag Berlin Heidelberg New York, p. 395.

2.Strain for CMOS performance Improvement.

3.J. Singh (1993). Physics of Semiconductor and their heterostructures. McGraw-Hill, pp. 98109.

4.Effects of mechanical stress on the performance of metal‑oxide‑semiconductor transistors.

来源:十二芯座

关键词: 芯片