随着摩尔定律的持续推进,芯片设计对功耗(Power)-性能(Performance)-面积(Area)(PPA)的优化需求愈发严苛。

标准单元(Standard Cell)作为数字芯片设计的基础构件,其布局质量直接影响整个芯片的PPA表现。

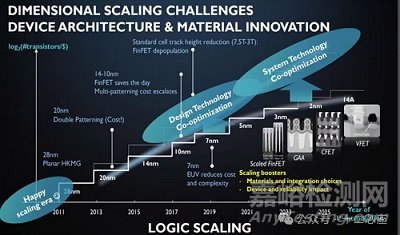

这里指出,从平面晶体管(Planar)到FinFET,再到环栅晶体管(GAA)、互补场效应晶体管(CFET)等新型器件结构,标准单元的轨道高度(Track Height)从7.5T压缩至3T,晶体管密度持续提升,设计规则愈加复杂,给标准单元布局生成带来了前所未有的挑战。

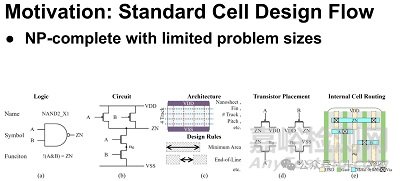

标准单元设计流程

从逻辑到布局

标准单元的设计流程通常包括以下几个阶段:

逻辑电路设计:定义单元功能(如NAND、NOR、XOR等);

晶体管级网表:将逻辑功能映射为晶体管电路;

晶体管布局(Placement):在满足设计规则的前提下,安排晶体管位置;

内部布线(Routing):在单元内部完成晶体管之间的连接;

版图优化:优化面积、延迟、功耗、可布线性等指标。

在亚10nm工艺节点下,设计空间巨大,优化目标复杂,传统方法难以兼顾最优性与计算效率。

核心挑战

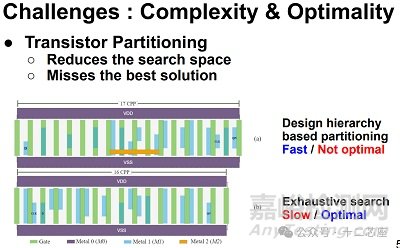

复杂性与最优性的博弈

晶体管分区(Transistor Partitioning)

目的:缩小搜索空间,加快布局速度;

问题:可能错过全局最优解;

权衡:快速 vs 最优。

如上图示,采用基于设计层次的分区方法可快速生成布局,但可能不如穷举搜索得到的布局紧凑。

Gear Ratio & Offset

引入非均匀网格(如2:3齿轮比)可增加布线资源;

不同 Gear Ratio,布局结构、引脚位置、布线通道都会发生变化。

面积与引脚可接入性的权衡

增加单元面积可提升引脚接入性(如从6CPP增至10CPP);但会牺牲面积,需要在面积最小化与布线友好性之间找到平衡点。

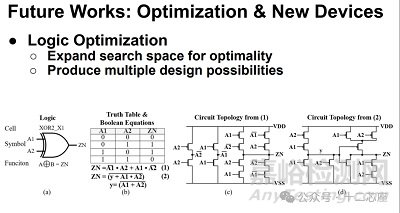

优化新方法与新器件结构

逻辑级优化

Expand search space for optimality

产生多种设计可能性

同一逻辑功能可通过不同布尔表达式实现;

例如 XOR2 可表示为:

F = A·B' + A'·B

或 F = (Y + A·B),其中 Y = (A + B)'

不同表达式对应不同晶体管拓扑结构;

通过逻辑变换可生成多种电路结构,供后续布局选择。

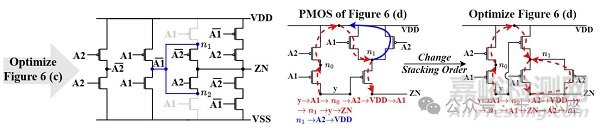

拓扑优化:晶体管堆叠顺序与网表重构

通过调整晶体管堆叠顺序,优化 Euler path,减少布线复杂度,可移除冗余晶体管,优化内部网表结构。

例如将某些中间信号直接映射为晶体管堆叠节点,减少过孔与金属层使用。

欧拉路径(Euler path) :通过图中所有边的简单路。(换句话说,每条边都通过且仅通过一次)

欧拉回路:闭合的欧拉路径。(即一个环,保证每条边都通过且仅通过一次)

驱动能力优化

通过网表分裂(Net Splitting)技术,将大驱动单元拆分为多个小单元;

可提升电路性能(如降低延迟、提高驱动能力),同时保持面积与功耗的可控性。

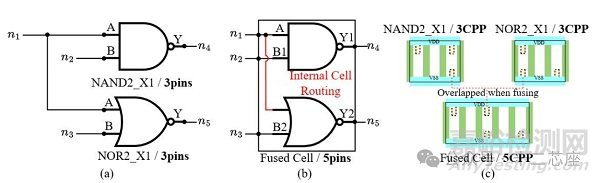

标准单元融合

将多个标准单元(如NAND2与NOR2)融合为一个复合单元;

可减少引脚数量、压缩单元面积,适用于引脚密度墙(Pin Density Wall)问题严重的场景;

总结

通过逻辑层、拓扑层、物理层的协同优化,可显著提升PPA;

结合DTCO(设计-工艺协同优化)与STCO(系统-技术协同优化)理念,未来仍有广阔提升空间;

新器件(如MESO、TFT)的引入,可能重新定义标准单元的设计范式。

在先进工艺节点下,标准单元不再只是“积木”,而是PPA战争的微观战场。每一个晶体管的摆放、每一条金属线的走向、甚至每一个过孔的位置,都会影响最终芯片的性能与良率。未来的标准单元设计,不再是“画版图”,而是跨层次、跨器件、跨工艺的系统级优化工程。(DTCO/STCO)

来源:十二芯座

关键词:

芯片

标准单元