嘉峪检测网 2025-04-18 09:11

导读:本文介绍了MOSFET失效原因及对策。

一、主要失效原因分类

MOSFET 失效可分为外部应力损伤、电路设计缺陷、制造工艺缺陷三大类,具体表现如下:

1. 外部应力损伤

(1)静电放电(ESD)击穿

成因:MOSFET 栅源极(G-S)间电容极小(几 pF)、输入阻抗极高(10⁹Ω+),少量静电电荷(如人体、环境摩擦产生)通过公式 \(U = Q/C\)

可生成数百伏高压,直接击穿 G-S 绝缘层。

典型场景:未接地的操作环境、化纤衣物摩擦、干燥环境下的器件搬运。

我们都知道虽然管子有抗静电的保护措施,但仍需小心对待,在存储和运输中最好用金属容器或者导电材料包装,不要放在易产生静电高压的化工材料或化纤织物中。组装、调试时,工具、仪表、工作台等均应良好接地。要防止操作人员的静电干扰造成的损坏,如不宜穿尼龙、化纤衣服,手或工具在接触集成块前最好先接一下地。对器件引线矫直弯曲或人工焊接时,使用的设备必须良好接地。

(2)过流、过压、过温

成因:

过流:输入端保护二极管电流容限仅约 1mA,瞬态电流超过 10mA(如浪涌、负载突变)时,二极管过热烧毁,失去保护作用。

过压:栅极电压超过额定值(如驱动电路故障),导致氧化层击穿;漏源极(D-S)间电压超过耐压值(VDS),引发雪崩击穿。

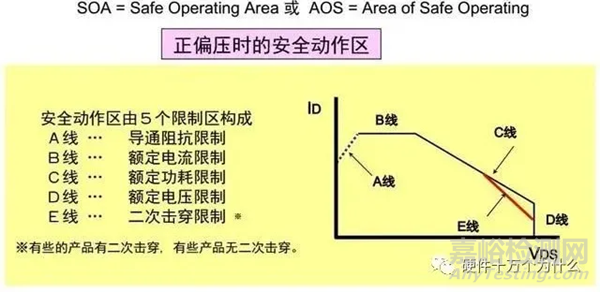

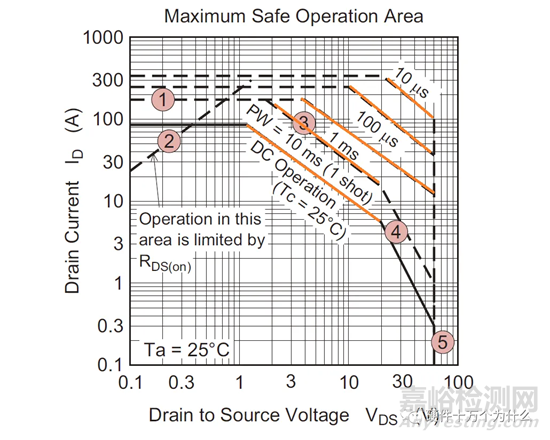

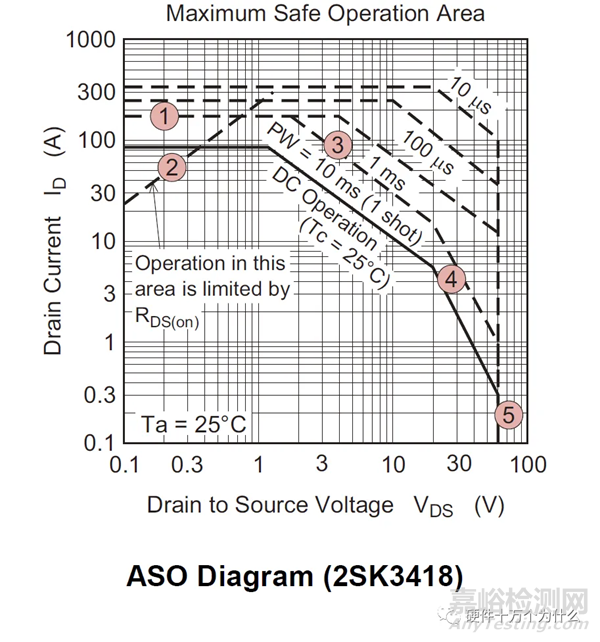

有的厂家将他称之为 “Area of Safe Operation (ASO)”

安全工作区:SOA(Safe operating area)是由一系列(电压,电流)坐标点形成的一个二维区域,开关器件正常工作时的电压和电流都不会超过该区域。简单地讲,只要器件工作在SOA区域内就是安全的,超过这个区域就存在危险。

SOA(Safe operating area)是指安全工作区,由一系列限制条件组成的一个漏源极电压VDS和漏极电流ID的二维坐标图,开关器件正常工作时的电压和电流都不应该超过该限定范围。

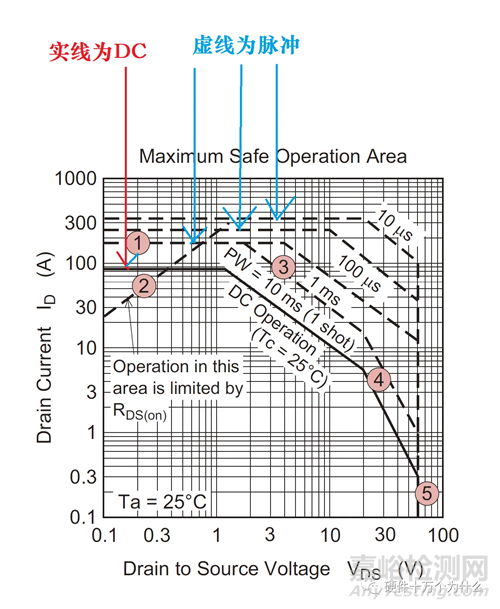

SOA区域分为以下5个区域。

A线 是由导通电阻RDS(on)max[ID=VDS/RDS(on)]限制的区域。该区域一般与ASO区域分开讨论。

因为在固定的VGS电压和环境条件下,功率MOSFET的RDS(ON)是固定的,因此这条斜线的斜率为1/R(DS(ON))。

B线 是受最大额定电流IDC(稳态直流)、ID(pulse)(脉冲)max限制的区域。即:Ids能够承载最大电流限制的线。

需要注意的是IDM是脉冲工作状态的最大电流IDC,通常最大漏极脉冲电流IDM为连续漏极电流ID的3到4倍,因此脉冲电流要远高于连续的直流电流。

C线 是受通道损耗(Channel dissipation或者Channel loss,ID流经DS这是主要功率产生的功耗)限制的区域,电流和电压的乘积的最大值,即额定功耗限制的线路。

正如我们注意到的那样,这条线带有一个恒定的斜率,但却是一个负斜率。它是恒定的,因为这条 SOA 功率限制线上的每个点都承载相同的恒定功率,由公式 P = IV 表示。

因此,在这个 SOA 对数曲线中,这会产生 -1 的斜率。负号是因为流过 MOSFET 的电流随着漏源电压的增加而减少。

这种现象主要是由于 MOSFET 的负系数特性在结温升高时会限制通过器件的电流。

D线 是Vds的额定电压相关,受耐压VDSsmax限制的区域。

漏源击穿电压BVDSS限制了器件工作的最大电压范围,在功率MOSFET正常工作中,若漏极和源极之间的电压过度增高,PN结反偏发生雪崩击穿,为保障器件安全,在关断过程及其稳态下必须承受的漏极和源极间最高电压应低于漏源击穿电压BVDSS。

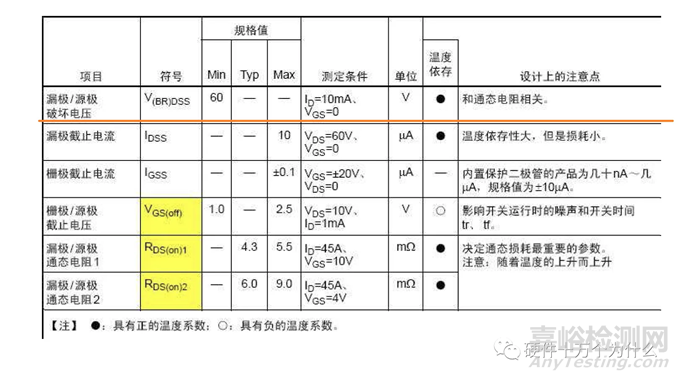

V(BR)DSS:漏-源击穿电压(破坏电压)

V(BR)DSS(有时候叫做BVDSS)是指在特定的温度和栅源短接情况下,流过漏极电流达到一个特定值时的漏源电压。这种情况下的漏源电压为雪崩击穿电压。V(BR)DSS是正温度系数,温度低时V(BR)DSS小于25℃时的漏源电压的最大额定值。在-50℃, V(BR)DSS大约是25℃时最大漏源额定电压的90%。

E线 是二次击穿限制, 与双极晶体管中的二次击穿区域类型相同,该区域在连续运行或以相对较长的脉冲宽度(几毫秒或更长)打开的条件下出现。这是因为,当工作电压在相同的外加电源线上升高时,工作电流自然降低,但在这个小电流区域,输出传输特性(Vgs Id特性)是负温度特性。当该区域变为大电流区域,需要改变正温度特性时,该现象消失。温度特性从负变为正的电流值不同于产品对产品,以及几安培或更小的产品,这种现象不太可能发生,这可以通过所谓的无二次击穿的恒定电源线来保证。

ABCDE线对应datasheet中标注的是2、1、3、5、4

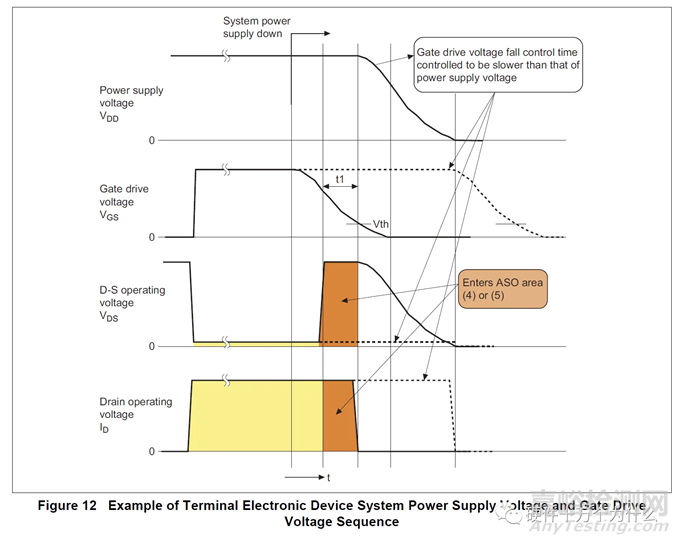

由于功率MOS FET通常用于开关应用,在正常操作中,它们通常用于有限区域(2)。电路设计中需要注意的一点是控制系统顺序。

图1.12显示了当系统的源电源被切断时,电子设备的电源电压和门驱动电压序列的示例。

如图中的实线所示,如果直到电源电压VDD关闭的下降时间长于栅极驱动电压VGS的下降时间,则VGS在图中的周期t1处于欠驱动状态,并进入ASO限制区域(4)或(5),因此有必要确认其是否处于安全操作区域。

避免此类操作区域的有效方法是执行顺序控制,以便栅极驱动电压VG的下降时间延迟到电源电压VDD完成下降之后,如Vgs那个图的虚线所示。

(3)栅极悬空与干扰

成因

栅极未接偏置或信号源时(悬空),易受外部电磁干扰,积累电荷导致误导通或 G-S 电压异常升高,最终击穿。

(4)操作不当(焊接、存储等)

成因

电烙铁未接地或漏电,焊接时瞬间高压击穿栅极;

存储运输中使用非导电包装(如塑料、化纤),积累静电;

引脚频繁弯曲导致内部引线断裂或封装开裂。

2. 电路设计缺陷

(1)保护措施缺失

未在栅极串联保护电阻(限制瞬态电流)或并联下拉电阻(泄放静电电荷);

驱动感性负载时未加续流二极管,导致 D-S 间反电动势过压。

(2)偏置与驱动不当

栅极驱动电压不足(低于开启电压 VGS (th))或过高(超过最大额定值);

高速开关场景中未优化驱动电阻,导致栅极振荡或电压过冲。

(3)散热与布局问题

大功率场景下散热设计不足,器件长期工作在高温区(超过结温 Tjmax),导致性能退化或热失控;

电路布局不合理,栅极走线过长易受干扰,或漏极大电流路径产生电磁耦合。

3. 制造工艺缺陷(批次性失效)

(1)封装与内部结构问题

固晶层(芯片与基板连接层)分层、厚度不均或固化不良(如案例中现象),导致散热失效或机械应力集中,引发接触不良或热敏感失效;

键合引线焊接不牢、氧化或断裂,造成引脚开路;

栅极氧化层厚度不均或存在缺陷,降低 ESD 耐压能力。

(2)材料与设计缺陷

保护二极管参数不匹配(如电流容限不足);

芯片掺杂工艺异常,导致沟道导通特性漂移。

二、针对性对策与预防措施

1. 外部应力防护(操作与环境控制)

(1)静电防护全流程管控

存储运输:使用金属屏蔽袋、导电泡沫或防静电包装,避免与化纤、塑料接触;

操作环境:工作台、工具(电烙铁、镊子)可靠接地,操作人员佩戴防静电手环 / 手套,穿棉质衣物;

电路设计:栅极并联 10-20kΩ 下拉电阻(泄放感应电荷),高频场景加 RC 滤波(如 100Ω 电阻 + 10nF 电容)抑制振荡。

(2)过流 / 过压保护设计

输入保护:可能出现大瞬态电流的回路中串接保护电阻(阻值 \(R = V_{surge}/I_{limit}\),如限制电流 1mA 时,R≥1kΩ@1V 浪涌);

耐压设计:选择 D-S 耐压值(VDS)高于电路最大工作电压 1.5 倍以上的器件,感性负载并联续流二极管(如肖特基二极管);

驱动电路:使用专用 MOSFET 驱动芯片,确保栅极电压稳定在额定范围内(如 N-MOS 选 10-15V 驱动)。

(3)规范操作与焊接工艺

焊接时电烙铁断电后利用余热操作,或使用恒温接地焊台(接地电阻<1Ω),先焊接地引脚;

引脚整形时使用防静电镊子,避免过度弯曲(距封装 1mm 以上操作)。

2. 电路设计优化

(1)栅极驱动与偏置设计

避免栅极悬空,未使用的栅极必须接下拉电阻(10-20kΩ)或信号地;

高速开关场景中,栅极串联阻尼电阻(10-100Ω)抑制振铃,并联 TVS 二极管(耐压值≤栅极额定电压)吸收瞬态过压。

(2)散热与布局策略

大功率 MOSFET 配置足够面积的散热片或 PCB 铜箔,确保结温 满足降额要求。

栅极走线尽量短且远离大电流路径,采用屏蔽线或覆地处理;

输入输出端并联去耦电容(如 100nF),抑制电源纹波干扰。

(3)器件选型原则

优先选择内置保护电阻、ESD 防护结构(如 VMOS)或集成驱动电路的器件;

大功率场景选栅极电容较大的型号(降低感应电压),小信号场景选高输入阻抗型号。

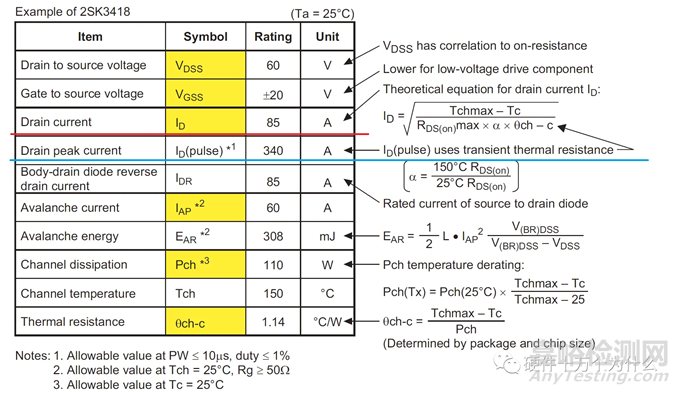

满足电压额定值及降额

电压额定值

漏源电压(VDS)

需大于电路中可能出现的最大工作电压(包括瞬态尖峰电压),一般预留 20%~30% 安全裕量。

例:若电路中 VDS 实际峰值为 100V,建议选择 VDS≥130V 的器件。

栅源电压(VGS)

超过额定 VGS(通常 ±20V 以内)会导致栅极氧化层击穿,需确保驱动电压在安全范围内,避免静电或干扰引入异常电压。

满足电流额定值及降额

连续漏极电流(ID)

需大于实际工作电流,同时考虑温升影响(环境温度升高时,ID 降额使用)。

计算公式:

脉冲漏极电流(IDM)

满足短时峰值电流需求(如开关瞬态、启动冲击电流),确保不超过器件脉冲额定值。

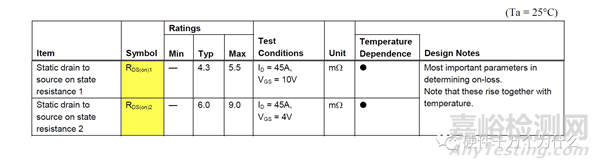

导通电阻(RDS (on))

热性能

3. 制造与质量管控

(1)来料检测与工艺追溯

新批次器件抽检 ESD 耐压(如 ±2kV 接触放电)、固晶层结合力(拉力测试);

保留首件样品,失效时对比分析(如 C-SAM 扫描、SEM 成像检查内部结构)。

(2)生产流程优化

固晶、键合工序严格控制参数(如胶水厚度、焊接温度),定期校准设备;

批量生产前进行 DFMEA 分析,识别潜在失效模式(如热应力、机械应力集中点)。

三、总结

MOSFET 失效多源于静电、过流等外部应力与设计、工艺缺陷的叠加作用。通过全流程静电防护(接地、下拉电阻、防静电操作)、电路保护设计(限流电阻、续流二极管)、器件选型优化(内置保护、合适耐压 / 电流规格)及制造质量管控(来料检测、工艺追溯),可显著降低失效风险。尤其注意:栅极绝不悬空、焊接必须接地、驱动电压合规,是避免人为失效的 “黄金三原则”。

来源:硬十

关键词: MOSFET失效