嘉峪检测网 2025-08-16 20:56

导读:本文将围绕栅氧化层击穿的成因、特征及失效模型展开探讨。

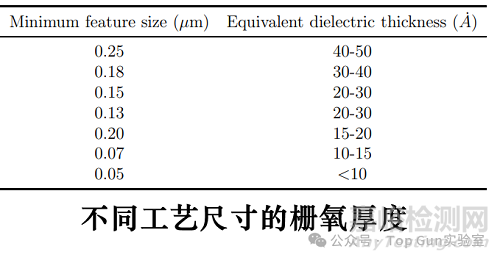

互补金属氧化物半导体(CMOS)工艺中,栅氧化层厚度(tₒₓ)随技术发展不断缩减。在65nm技术节点,其厚度已达到1.2nm至1.6nm。随着尺寸缩小,栅氧化层中的电场随之升高,薄氧化层的长期可靠性成为深亚微米(<0.10μm)工艺中的关键问题。本文将围绕栅氧化层击穿的成因、特征及失效模型展开探讨。

栅氧化层虽薄,却是晶体管的“守护神”,它的可靠性直接关系到整个芯片的寿命。

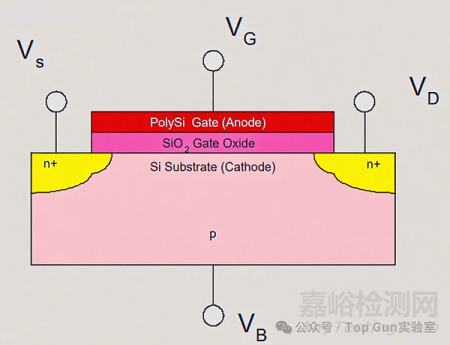

N型金属氧化物半导体(NMOS)晶体管是四端器件,栅极控制P型硅衬底中沟道的形成,以连接N型掺杂的源极和漏极。第四端(体端)在NMOS中通常接地,在P型金属氧化物半导体(PMOS)中接VDD。栅氧化层由二氧化硅构成,作为栅极与衬底间的绝缘体。多晶硅栅极经重掺杂成为导体,衬底虽也是硅,但采用生长而非结晶方式形成(即多晶硅)。

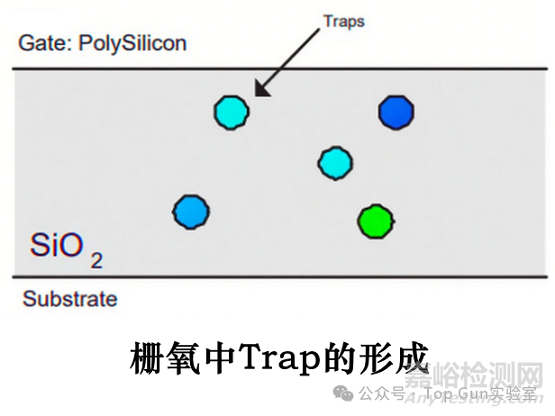

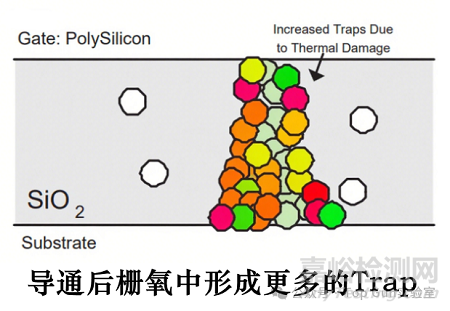

栅氧化层中的缺陷通常称为陷阱,因退化的氧化层能捕获电荷而得名。陷阱通常呈电中性,在阳极附近会迅速带正电,在阴极附近则带负电。

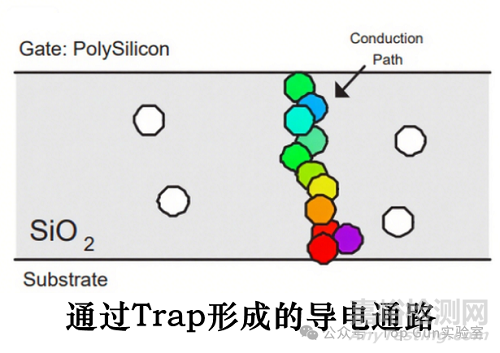

栅氧化层击穿指从栅氧化层某一界面的“种子”开始,一系列相连的键形成的簇到达另一界面的时刻。

击穿始于氧化层中陷阱的形成。初期陷阱互不重叠,无法导电;随着陷阱增多,它们重叠形成导电通路,此时发生软击穿(SBD)。

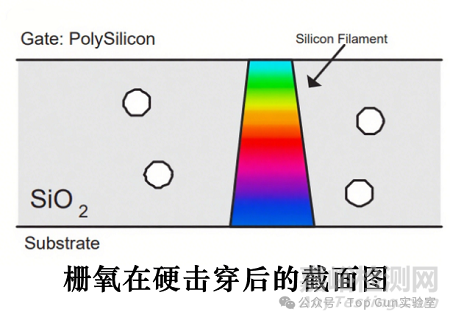

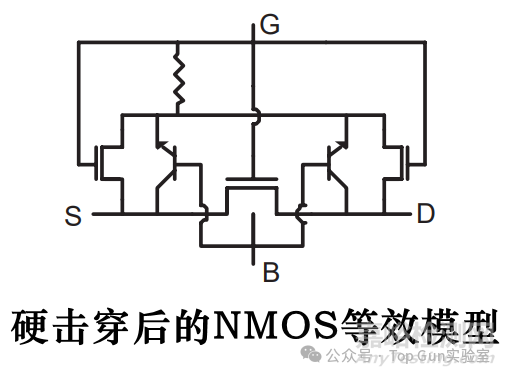

导电发生后,热损伤会产生新陷阱,进一步增加电导,形成“导电-产热-更多导电”的循环,最终导致热失控和击穿点横向扩展。氧化层击穿点中的硅熔化并释放氧气,形成硅丝,这种击穿称为硬击穿(HBD)。从SBD到HBD,就像小火花变成了大火苗,破坏程度逐级升级。

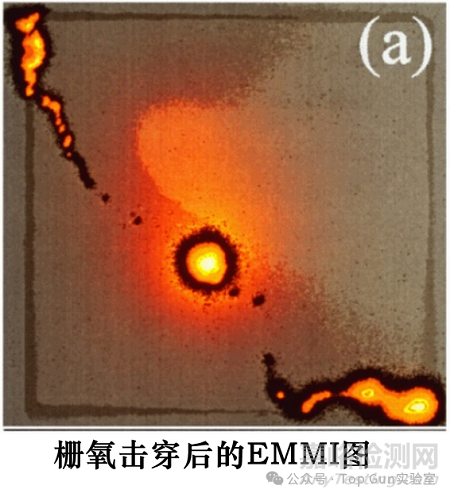

下图展示了通过发射显微镜(EMMI)观察到的栅氧化层;亮区是光子发射集中的区域,显示出栅氧化层击穿的部位。

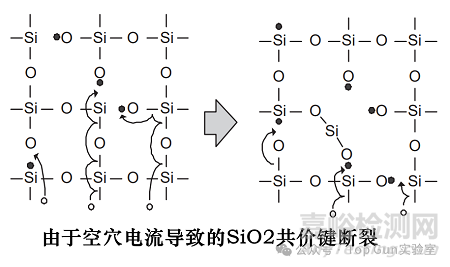

反相器击穿后,漏极电流与栅极电流密切匹配,源极电流大幅增加。正电压应力下NMOS受损,负电压应力下PMOS受损,传输特性发生偏移。下图展示了空穴在氧化物中如何产生陷阱的一个示例,其中空穴会在单个硅原子处引发两次键断裂

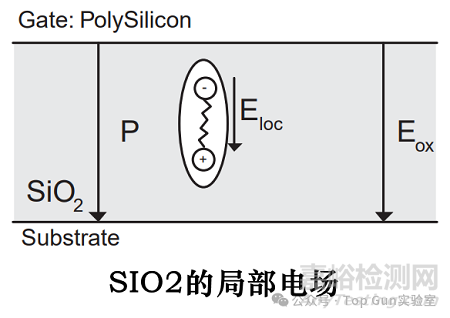

当连接键角超过 150° 时,化学键的强度会大幅减弱,进而产生氧空位,此时硅 - 氧 - 硅(Si - O - Si)键会被硅 - 硅(Si - Si)键取代,如下图所示 。这种氧空位被认为是导致氧化层击穿的缺陷。氧化物内剩余的氧 - 硅(O - Si)键是极性很强的键;总能量的 70% 源于离子键成分。此外,硅 - 硅(Si - Si)键是一种非常弱的键。因此,当向氧化物施加电场时,由于 O - Si 键的极性,晶格会发生畸变。而且,这种畸变会引发如下图所示的极化(P) 。这样一来,每个二氧化硅(SiO₂)分子不仅会受到外加电场的作用,还会受到由极化(P)产生的偶极场的影响,所以局部电场(Eloc)会显著大于外加电场(Eox) 。

当击穿发生在沟道上方时,就如同电流从栅极通过击穿路径注入沟道,随后流向漏极和源极。这种效应可以用下图右侧和左侧的两个晶体管来模拟。此外,当栅极电压(VG)<0 时,下图的模型中会额外加入两个双极晶体管,以解释从栅极注入的电子通过衬底扩散并最终在源极或漏极收集的现象。

栅氧化层击穿是CMOS技术中的关键可靠性问题,随氧化层变薄愈发突出。软击穿和硬击穿均由陷阱形成导电通路导致,渗流模型能较好描述这一过程。阳极空穴注入模型和热化学模型解释了陷阱产生机制,但仍存在争议。

来源:Internet