嘉峪检测网 2025-03-26 20:08

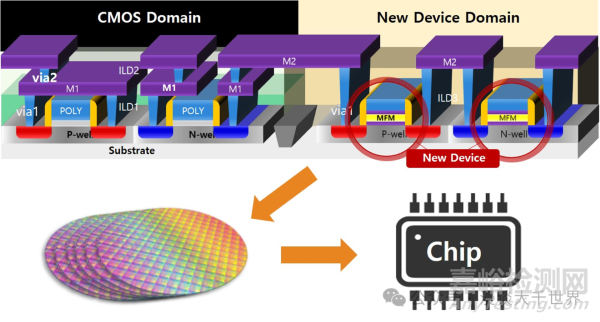

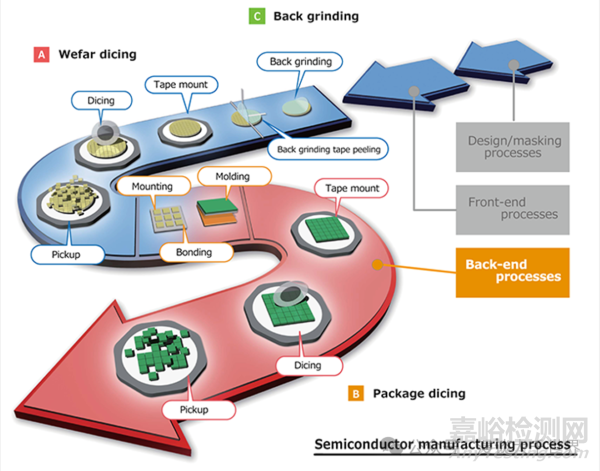

导读:前段工艺(Front-End)、中段工艺(Middle-End)和后段工艺(Back-End)是半导体制造过程中的三个主要阶段,它们在制造过程中扮演着不同的角色。

前段工艺(Front-End)、中段工艺(Middle-End)和后段工艺(Back-End)是半导体制造过程中的三个主要阶段,它们在制造过程中扮演着不同的角色。

前段工艺(Front-End)主要关注晶体管的制造;中段工艺(Middle-End)则侧重于连接晶体管与金属互连,起到承上启下的关键作用;后段工艺(Back-End)主要负责构建金属互连层,实现芯片内部各晶体管之间的电气连接。

芯片制造的三个阶段形成了精密的技术链条,前段的器件性能、中段的界面质量和后段的互连效率共同决定了芯片的PPA(功耗、性能、面积)特性。

1. 前段工艺(FEOL: Front-End-of-Line)

1.1 核心任务

在硅晶圆上构建晶体管等基础器件,为后续的互连和封装奠定基础。这一阶段的精度和质量直接影响到芯片的性能和功耗。

1.2 关键技术

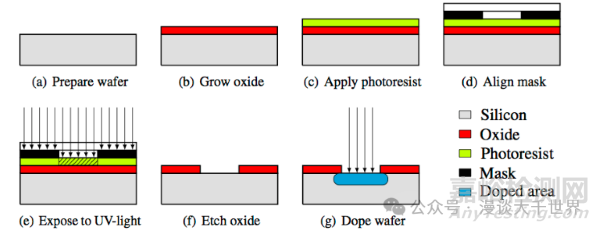

衬底制备

硅片抛光和清洗:通过化学机械抛光(CMP)和多级清洗工艺,消除硅片表面的划痕、颗粒污染物和有机残留,确保表面粗糙度小于0.1nm,为后续外延生长提供完美界面。

外延生长(Epitaxy):采用化学气相沉积(CVD)技术,在硅片表面原子级平整的基础上,生长出高质量的半导体层,如Si/SiGe,厚度可精确控制在10nm~10μm范围内,用于构建FinFET的鳍式结构或GAA晶体管的沟道层。

器件成型

光刻与刻蚀:利用极紫外光刻(EUV)技术,其波长为13.5nm,能够定义纳米级甚至亚纳米级的图形。例如,在FinFET工艺中,通过EUV光刻将设计好的鳍式结构图案转移到光刻胶层,随后采用反应离子刻蚀(RIE)技术,将图案精确转移到硅衬底,形成高度约50nm、宽度约7nm的鳍式结构,线宽粗糙度(LWR)控制在<1nm。

离子注入:使用高能离子注入机,将掺杂离子(如硼、磷、砷等)以精确的能量和剂量注入硅片特定区域,形成源极(Source)、漏极(Drain)和阈值电压调整区。例如,在先进节点中,为了实现原子级掺杂均匀性,采用多重离子注入工艺,结合低温注入和快速热退火(RTP),确保掺杂原子的精确分布,形成陡峭的掺杂剖面,源漏延伸区的掺杂浓度梯度可达到1×10²⁰ atoms/cm³/nm。

栅极堆叠:采用高k介质(如HfO₂,k值约为20~25)结合金属栅(RMG)工艺,降低漏电流。例如,在3nm节点的FinFET器件中,高k介质层厚度约为1nm,金属栅材料采用TiN/TaC/TiAl等多层结构,通过原子层沉积(ALD)技术实现高k介质的均匀生长和金属栅的精确填充,有效降低栅极漏电流至1×10⁻¹⁰A以下。

高温工艺

快速热退火(RTP):在氮气或氩气氛围下,利用卤素灯或激光作为热源,将硅片迅速加热至1000℃~1300℃,并在几秒到几十秒内完成掺杂原子的激活和损伤修复,确保源漏区的掺杂激活率大于95%。

氧化/氮化硅沉积:采用热氧化或等离子体增强化学气相沉积(PECVD)技术,在硅片表面形成氧化硅或氮化硅薄膜,厚度约为5nm~50nm,用于形成侧墙(Spacer),保护栅极结构,减少短沟道效应。

1.3 技术挑战

3nm以下节点的短沟道效应控制:随着器件尺寸缩小至3nm以下,短沟道效应愈发严重,导致漏电流增大和阈值电压难以控制。例如,在3nm节点的FinFET器件中,由于鳍宽和鳍高尺寸的缩小,纵向和横向的电场耦合增强,使得漏电流增加至1×10⁻⁸A以上。为解决这一问题,需要采用新型器件结构如GAA(环绕栅极)晶体管和CFET(互补FET),通过全包围栅极控制沟道电势,有效抑制短沟道效应,将漏电流降低至1×10⁻¹²A以下。

原子级掺杂均匀性:在先进节点中,源漏区的掺杂浓度需要达到1×10²⁰ atoms/cm³以上,且掺杂剖面的均匀性要求在±5%以内。例如,在FinFET器件的源漏延伸区,需要实现精准的SD掺杂剖面,即从源漏主区到沟道区的掺杂浓度逐渐降低,形成陡峭的掺杂梯度,以减少结深和漏电流。目前,通过多重离子注入和低温注入技术,结合精确的热处理工艺,能够实现原子级掺杂均匀性,但仍然面临掺杂浓度波动和杂质聚集等问题。

EUV多重曝光套刻精度:为了实现更高分辨率的图形转移,EUV多重曝光技术应运而生。例如,在5nm节点及以下工艺中,通常需要进行2~4次EUV曝光,每次曝光的套刻精度要求在<1nm范围内。然而,由于EUV光刻机的光学系统复杂性和机械精度限制,以及光刻胶的敏感性和显影工艺的影响,实际套刻精度往往在1.5nm~2nm之间,导致图形转移误差和器件性能波动。为提高套刻精度,需要优化光刻机的对准系统和曝光参数,同时开发新型光刻胶材料和显影工艺,以实现Overlay < 1nm的目标。

2. 中段工艺(MEOL:Middle-End-of-Line)

2.1 核心任务

建立晶体管与金属互连的桥梁,确保信号能够高效、准确地在器件和互连网络之间传输,对芯片的速度和功耗具有重要影响。

2.2 关键技术

接触孔(Contact)制造

自对准硅化物(Salicide):在源/漏/栅极表面形成NiPtSi等低电阻接触。例如,在FinFET工艺中,通过沉积镍铂合金薄膜,随后进行快速热退火,使镍铂与硅发生反应,形成低电阻的硅化物相,电阻率可降低至5μΩ·cm以下,减少接触电阻,提高器件的开关速度。

钨栓塞(W-Plug):采用化学气相沉积(CVD)技术,将钨填充到高深宽比接触孔中,孔深与孔径之比大于10:1。例如,在3nm节点的FinFET器件中,接触孔直径约为20nm,深度约为200nm,通过CVD-W工艺实现无空洞填充,确保接触孔的导电性和可靠性。

局部互连(Local Interconnect)

沉积TiN/TaN等扩散阻挡层:在铜互连工艺中,为了防止铜原子扩散到低k介质中,采用物理气相沉积(PVD)技术,在铜线和低k介质之间沉积TiN/TaN等扩散阻挡层,厚度约为2nm~5nm,确保阻挡层的完整性和致密性,铜原子扩散系数可降低至1×10⁻²⁰cm²/s以下。

铜双大马士革工艺(Dual Damascene):形成M0/M1金属层。例如,在3nm节点的BEOL工艺中,采用铜双大马士革工艺,通过光刻和刻蚀技术,在低k介质中形成通孔和沟槽的双重图案,随后采用电化学沉积(ECD)技术填充铜,实现M0/M1金属层的互连,铜线宽和间距可达到15nm~20nm,电阻率约为1.7μΩ·cm。

平坦化工艺

化学机械抛光(CMP):在多层互连工艺中,为了消除表面起伏,确保光刻焦深,采用化学机械抛光技术对铜层和低k介质层进行平坦化处理。例如,在BEOL工艺中,每完成一层互连的沉积和图案化后,都需要进行CMP工艺,将表面粗糙度控制在<0.5nm,确保后续光刻工艺的精度和质量。

2.3 技术挑战

接触孔电阻控制:在先进节点中,接触孔的电阻对器件性能和功耗的影响愈发显著。例如,在3nm节点的FinFET器件中,接触孔电阻要求小于10Ω·μm,否则会导致源漏电流降低和器件速度减慢。为降低接触孔电阻,需要优化自对准硅化物工艺和钨栓塞工艺,提高硅化物的形成质量和钨的填充密度,同时减小接触孔的尺寸和深度比。

高深宽比结构的无空洞填充:随着互连结构尺寸的缩小,高深宽比结构如TSV(硅通孔)的填充难度增加。例如,在3D封装中,TSV的深宽比可达到15:1以上,直径约为5μm~10μm,深度可达50μm~100μm。采用CVD-W或电镀铜工艺进行填充时,容易出现空洞和缝隙,导致互连可靠性降低。为实现无空洞填充,需要优化工艺参数和材料选择,例如采用新型的填充材料如钴或钌,以及改进的填充工艺如种子层增强电镀技术。

界面态密度优化:在互连结构中,界面态密度对电迁移和可靠性具有重要影响。例如,在铜/低k介质界面,界面态密度要求低于1×10¹¹ cm⁻²eV⁻¹,否则会加速铜原子的扩散,导致互连断路。通过优化扩散阻挡层的沉积工艺和表面处理技术,能够降低界面态密度,提高互连的可靠性和寿命。

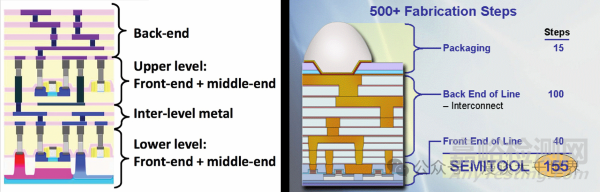

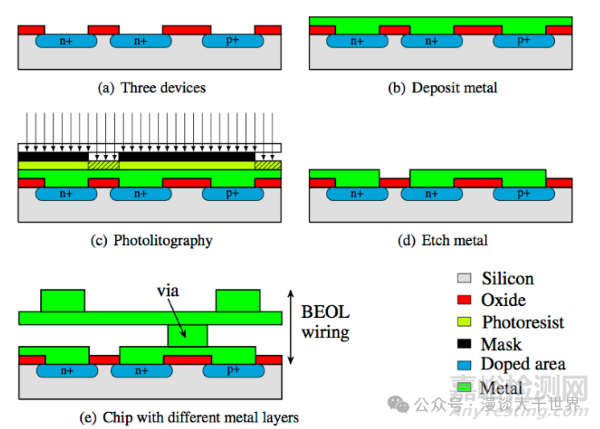

3. 后段工艺(BEOL:Back-End-of-Line)

3.1 核心任务

构建多层金属互连网络,实现芯片内部数百万甚至数千万个晶体管之间的电气连接,对芯片的性能、功耗和面积(PPA)具有决定性影响。

3.2 关键技术

互连层堆叠

低k介质(如SiCOH,k=2.4~3.0)沉积:采用化学气相沉积(CVD)技术,在互连层之间沉积低k介质,减少寄生电容。例如,在10nm节点及以下工艺中,低k介质的厚度约为100nm~200nm,其k值的降低能够显著减少互连之间的电容,提高信号传输速度和降低功耗。

铜互连(Cu Damascene)替代传统铝线:铜的电阻率约为1.7μΩ·cm,比传统铝线(电阻率约为2.8μΩ·cm)更低,能够降低互连电阻,提高芯片的性能和能效。例如,在14nm节点及以下工艺中,铜互连已经成为主流技术,通过铜双大马士革工艺实现铜线的精确填充和图案化,铜线宽和间距可达到30nm~50nm。

多层布线

通孔(Via)与金属线(Metal Line)的逐层构建:在BEOL工艺中,通常需要构建10层以上的金属互连网络。例如,在7nm节点的芯片中,金属层数量可达12层,每层金属线和通孔的尺寸和间距逐渐缩小,最上层金属线宽和间距可达到1μm~2μm,而最下层(M1层)金属线宽和间距可达到20nm~30nm。通过逐层的光刻、刻蚀和填充工艺,实现信号在不同层之间的传输和分配。

空气隙(Air Gap)技术进一步降低k值:为了进一步降低互连之间的寄生电容,采用空气隙技术,在互连结构之间形成真空或气体间隙,其k值接近1。例如,在5nm节点及以下工艺中,空气隙技术应用于局部互连和部分金属层之间,通过优化工艺流程和材料选择,确保空气隙的稳定性和可靠性,减少电容达30%~50%。

封装集成

硅通孔(TSV)实现3D堆叠:在3D封装技术中,通过在硅片上制造TSV,实现芯片之间的垂直互连。例如,在3D NAND闪存和高端处理器的3D封装中,TSV直径约为5μm~10μm,深度可达50μm~100μm,能够显著减少芯片之间的互连长度,提高集成度和性能。

微凸点(Microbump)键合用于Chiplet集成:在Chiplet集成技术中,通过微凸点键合实现小芯片之间的水平互连。例如,在AMD的Ryzen系列处理器中,微凸点直径约为10μm~20μm,间距约为20μm~50μm,能够实现高密度的电气连接,提高芯片的模块化设计和制造灵活性。

3.3 技术挑战

电迁移(EM)和应力迁移(SM)导致的互连可靠性问题:在高电流密度和温度应力下,铜互连容易发生电迁移和应力迁移现象,导致互连断路或短路。例如,在10nm节点及以下工艺中,铜互连的电流密度可达到1×10⁶ A/cm²以上,电迁移失效时间可缩短至1×10⁶小时以下。为提高互连可靠性,需要优化铜互连的结构设计和材料选择,例如采用新型的阻挡层材料如钴或钌,以及改进的互连工艺如空气隙技术和应力缓冲层沉积。

超低k介质机械强度不足:随着k值的降低,低k介质的机械强度也相应降低,容易在后续的CMP和封装工艺中出现划伤和破裂。例如,超低k介质(k<2.0)的杨氏模量通常低于5GPa,而在CMP工艺中,抛光垫的压力可达到10kPa~50kPa,容易导致低k介质层的损伤。为提高低k介质的机械强度,需要开发新型的低k介质材料和加固工艺,例如采用多孔结构优化和表面涂层技术。

多层布线中的RC延迟优化:在多层互连网络中,互连的电阻(R)和电容(C)会导致信号传输延迟,影响芯片的性能。例如,在14nm节点的芯片中,互连的RC延迟占总信号延迟的50%以上。为优化RC延迟,需要采用低电阻的互连材料如铜和低k介质,同时优化互连的布线拓扑结构和层次设计,例如采用RDL(重分布层)技术重新分配互连网络,减少互连长度和交叉电容。

4. 工艺演进

4.1 先进技术

前段:GAA(环绕栅极)晶体管、CFET(互补FET)

GAA晶体管:通过全包围栅极结构,有效控制沟道电势,抑制短沟道效应,适用于3nm及以下节点。例如,在三星的3nm GAA工艺中,采用纳米线或纳米片作为沟道材料,沟道长度可缩小至1nm~3nm,漏电流可降低至1×10⁻¹²A以下,同时提高器件的驱动电流和性能。

CFET(互补FET):将NMOS和PMOS器件垂直堆叠,进一步缩小芯片面积,提高集成度。例如,在IMEC的CFET研究中,通过3D集成技术将PMOS器件堆叠在NMOS器件之上,芯片面积可缩小30%~50%,同时减少互连长度和功耗。

中段:自对准通孔(Self-Aligned Via)

自对准通孔技术:通过光刻和刻蚀工艺的优化,使通孔与下方的金属线自动对准,减少工艺偏差和接触电阻。例如,在台积电的N7工艺中,采用自对准通孔技术,通孔与金属线的对准精度可达到±5nm,接触电阻可降低至5×10⁻¹⁰Ω·μm以下,提高互连的可靠性和性能。

后段:混合键合(Hybrid Bonding)、光互连

混合键合技术:结合微凸点键合和TSV技术,实现高密度、低延迟的3D封装互连。例如,在苹果的M1 Ultra芯片中,采用混合键合技术将两颗M1 Max芯片无缝连接,互连带宽可达2.5TB/s,延迟极低,相当于单颗芯片的性能。

光互连技术:利用光信号代替电信号进行长距离、高速率的数据传输,减少互连功耗和延迟。例如,在Intel的研究中,通过在芯片表面集成光波导和光收发器,实现芯片内部和芯片之间的光互连,传输速率可达100Gbps以上,功耗降低至1pJ/bit以下。

4.2 材料革新

二维材料(MoS₂):具有原子级厚度和优异的电学性能,可用于构建超薄沟道器件,适用于后摩尔时代的小尺寸器件。例如,在MoS₂基的晶体管中,沟道厚度可达到1nm以下,载流子迁移率可达到200cm²/V·s以上,具有低功耗和高性能的特点。

钴互连:钴的电阻率约为6μΩ·cm,虽然高于铜,但在小尺寸互连中具有更好的电迁移特性和与低k介质的兼容性。例如,在7nm节点及以下工艺中,钴互连应用于最下层金属线和接触孔,提高互连的可靠性和工艺良率。

铋基接触金属:铋具有低电阻和良好的与硅的接触特性,可用于替代传统的镍硅化物接触,降低接触电阻。例如,在FinFET器件中,采用铋基接触金属,接触电阻可降低至1×10⁻¹⁰Ω·μm以下,提高器件的性能和能效。

来源:漫谈大千世界

关键词: 芯片